УА/х

Изобретение относится к радиотехнике и может быть использовано в приемопередающей аппаратуре и в ))измери- тельной технике.i

Целью изобретения является уменьшение шага сетки выходных частот.

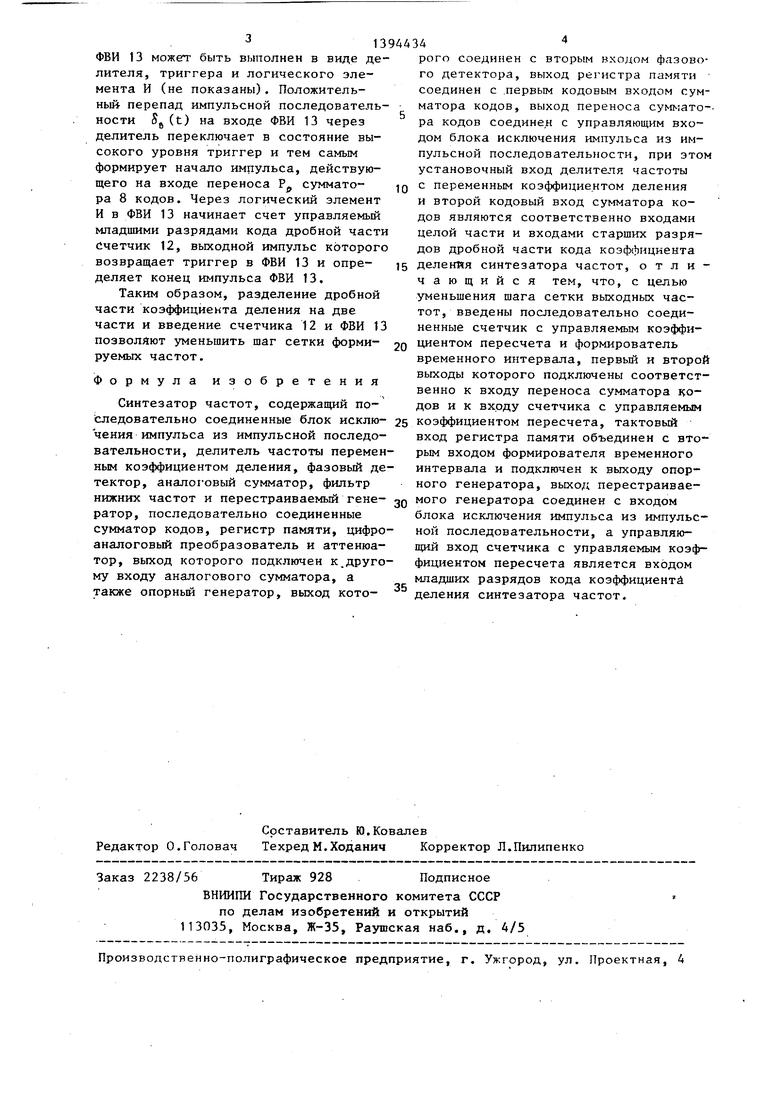

На чертеже п)едставлена структурная электрическая схема синтезатора частот.

Синтезатор частот содержит перестраиваемый генератор 1, блок 2 исключения импульса из импульсной после15

довательности, делитель 3 частоты переменным коэффициентом деления (ДПКД), фазовый детектор 4, аналоговый сумматор 5, опорный генератор 6, фильтр 7 нижних частот, сумматор 8 кодов, регистр 9 памяти, циф-2о роаналоговый преобразователь (ЦДЛ) 10, аттенюатор 11, счетчик 12 с управляемым коэффициентом пересчета и формирователь 13 временного интервала (ФВИ).25

Синтезатор частот работает следую- , щим образом.

Перестраиваемый генератор 1, блок 2 исключения импульса, ДПКД 3, фазоЧастота, с которой осуществляет исключение одного импульса, меняет в зависимости от содержания суммат ра 8 кодов. Содержимое сумматора 8 кодов изменяется с опорной частото на величину кода дробной части коэ фициента деления. Выходной код сум тора 8 кодов записывается в регист который несет информацию об опереж нии импульсной последовательности {t) последовательности Sg (t) . Пе ложение сумматора 8 кодов соответс вует фазовому сдвигу, равному Zlf, служит сигналом для запуска блока исключения имцульса. Выход регистра 9 соединен с входом ЦАП 10, поэ му выходное напряжение ЦАП 10 изме ется по тому же пилообразному зако как помеха дробности на выходе фаз вого детектора 4. Аналоговое напря ние ЦАП 10 регулируется аттенюатор 11 и в аналоговом сумматоре 5 комп сирует помеху дробности.

Цифровой код дробной части разделяется на две части: на старшие

вый детектор 4, аналоговый сумматор 5 30 младшие FL разряды. Разрядность

и фильтр 7 образуют петлю фазовой автоподстройки частоты. Частота fg выходного сигнала задается тремя цифровыми кодами, соответствующими целой части N, старшим разрядам дробной части FH и младшими разрядами дробной части FL. Поэтому синхронизация частоты перестраиваемого генератора 1 происходит на чатгтоте

старших разрядов определяется разр ностью сумматора 8 кодов. Реально личество разрядов не превьш1ает дес ти. Это может ограничить шаг сетки частот, определяемый значением мла ших разрядов FL кода. ФВИ 13, дейс вующий на входе переноса мпадшего разряда сумматора 8 кодов, и счетчик 12, управляемый кодом младших разрядов дробной части FL, выдают команду для искдючения из выходной последовательности через время

Вы)

„. N, (FH-t-FL).

При 3toM в промежуток времени периода опорной частоты помещается N,(FH+FL) периодов частоты перестраиваемого генератора 1. Дробное деление в петле автоподстройки обеспечивается действием блока 2 исключения импульса. При достижении опережения по фазе на 2, т.е. на время одного периода импульсной последовательности e(t) опорного генератора 6, исключается один период из последовательности перестраиваемого генератора 1. Поэтому на время такого одного цикла коэффициент деления становится N+1, а средние значения час- тот импульсных последовательностей 5(t) и5J,Ct).нa обоих входах фазового детектора 4 сравниваются.

0

5

о 5

Импульс исключается периодически, и из-за эт.ого на выходе фазового детектора 4 появляется помеха дробности.

Частота, с которой осуществляется исключение одного импульса, меняется в зависимости от содержания сумматора 8 кодов. Содержимое сумматора 8 кодов изменяется с опорной частотой на величину кода дробной части коэффициента деления. Выходной код сумматора 8 кодов записывается в регистр 9, который несет информацию об опережении импульсной последовательности {t) последовательности Sg (t) . Переложение сумматора 8 кодов соответствует фазовому сдвигу, равному Zlf, и служит сигналом для запуска блока 2 исключения имцульса. Выход регистра 9 соединен с входом ЦАП 10, поэтому выходное напряжение ЦАП 10 изменяется по тому же пилообразному закону, как помеха дробности на выходе фазового детектора 4. Аналоговое напряжение ЦАП 10 регулируется аттенюатором 11 и в аналоговом сумматоре 5 компенсирует помеху дробности.

Цифровой код дробной части разделяется на две части: на старшие FH

o

5

5

старших разрядов определяется разрядностью сумматора 8 кодов. Реально количество разрядов не превьш1ает десяти. Это может ограничить шаг сетки частот, определяемый значением младших разрядов FL кода. ФВИ 13, действующий на входе переноса мпадшего разряда сумматора 8 кодов, и счетчик 12, управляемый кодом младших разрядов дробной части FL, выдают команду для искдючения из выходной последовательности через время

.- . т

FH+FL

При десятичном п-разрядном сумматоре 8 кодов код старших разрядов равняется

Н,+10 + ,

при т-разрядном счетчике 12 десятичный код младших разрядов

L,

Н4+...+10

Н.+...+

+ Li+...;iO-

где Н; и

ь; Ц-ь,

т

десятичные значения

1-тых разрядов.

Выбором практически реализуемого числа старших разрядов дробной части (пи 10) и подбором величины га достигается требуемый шаг сетки частот.

ФВИ 13 может быть выполнен в виде делителя, триггера и логического элемента И (не показаны). Положительный перепад импульсной последовательности Sg (t) на входе ФВИ 13 через делитель переключает в состояние высокого уровня триггер и тем самым формирует начало импульса, действующего на входе переноса Р сумматора 8 кодов. Через логический элемент И в ФВИ 13 начинает счет управляет й младшими разрядами кода дробной части Счетчик 12, выходной импульс которого возвращает триггер в ФВИ 13 и определяет конец импульса ФВИ 13,

Таким образом, разделение дробной части коэффициента деления на две части и введение счетчика 12 и ФВИ 13 позволяют уменьшить шаг сетки формируемых частот.

Формула изобретения Синтезатор частот, содержащий пороге соединен с вторым входом фазового детектора, выход регистра памяти соединен с .первьм кодовым входом сумматора кодов, выход переноса сумматора кодов соединен с управляющим входом блока исключения импульса из импульсной последовательности, при этом установочный вход делителя частоты

Q с переменным коэффициентом деления и второй кодовый вход сумматора кодов являются соответственно входами целой части и входами старших разрядов дробной части кода коэффициента

15 деления синтезатора частот, отличающийся тем, что, с целью уменьшения шага сетки выходньк частот, введены последовательно соединенные счетчик с управляемым коэффи20 циентом пересчета и формирователь

временного интервала, первый и второй выходы которого подключены соответственно к входу переноса сумматора кодов и к входу счетчика с управляемым следовательно соединенные блок исклю- 25 коэффициентом пересчета, тактовый чения импульса из импульсной последо- вход регистра памяти объединен с вто- вательности, делитель частоты переменным коэффициентом деления, фазовый детектор, аналоговый сумматор, фильтр нижних частот и перестраиваемый гене- Q ратор, последовательно соединенные сумматор кодов, регистр памяти, цифро- аналоговый преобразователь и аттенюатор, выход которого подключен к.другому входу аналогового сумматора, а

35

рым входом формирователя временного интервала и подключен к вьпсоду опорного генератора, выход перестраиваемого генератора соединен с входом блока исключения импульса из импульсной последовательности, а управляющий вход счетчика с управляемым коэффициентом пересчета является входом младших разрядов кода коэффициент деления синтезатора частот.

также опорный генератор, выход кото

роге соединен с вторым входом фазового детектора, выход регистра памяти соединен с .первьм кодовым входом сумматора кодов, выход переноса суммато- ра кодов соединен с управляющим входом блока исключения импульса из импульсной последовательности, при этом установочный вход делителя частоты

Q с переменным коэффициентом деления и второй кодовый вход сумматора кодов являются соответственно входами целой части и входами старших разрядов дробной части кода коэффициента

5 деления синтезатора частот, отличающийся тем, что, с целью уменьшения шага сетки выходньк частот, введены последовательно соединенные счетчик с управляемым коэффи0 циентом пересчета и формирователь

временного интервала, первый и второй выходы которого подключены соответственно к входу переноса сумматора кодов и к входу счетчика с управляемым 25 коэффициентом пересчета, тактовый вход регистра памяти объединен с вто- Q35

рым входом формирователя временного интервала и подключен к вьпсоду опорного генератора, выход перестраиваемого генератора соединен с входом блока исключения импульса из импульсной последовательности, а управляющий вход счетчика с управляемым коэффициентом пересчета является входом младших разрядов кода коэффициент деления синтезатора частот.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Синтезатор частот | 1986 |

|

SU1376242A1 |

| Синтезатор частот | 1978 |

|

SU824451A1 |

| Синтезатор частот | 1987 |

|

SU1543545A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1363458A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1483632A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

Изобретение относится к радиотехнике и м.б. использовано в приемопередающей аппаратуре и в измерительной технике. Целью изобретения является уменьшение шага сетки выходных частот. Устр-во содержит перестраиваемый генератор 1, блок 2 исключения импульса из импульсной последовательности, делитель частоты с переменным коэф.деления 3, фазовый детектор 4, аналоговый сумматор 5, опорный генератор 6, фильтр 7 нижних частот, сумматор кодов 8, регистр 9 памяти, ЦАП 10, аттенюатор 11. Цель достигается введением в устройство счетчика 12с управляемым коэффициентом пересчета, формирователя 13 временного интервала и разделением дробной части коэффициента деления на две части: на Q старшие FH и младшие FL разряды, 1 ил.

| Патент США № 3928813, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Патент США № 4179670, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

Авторы

Даты

1988-05-07—Публикация

1986-05-26—Подача