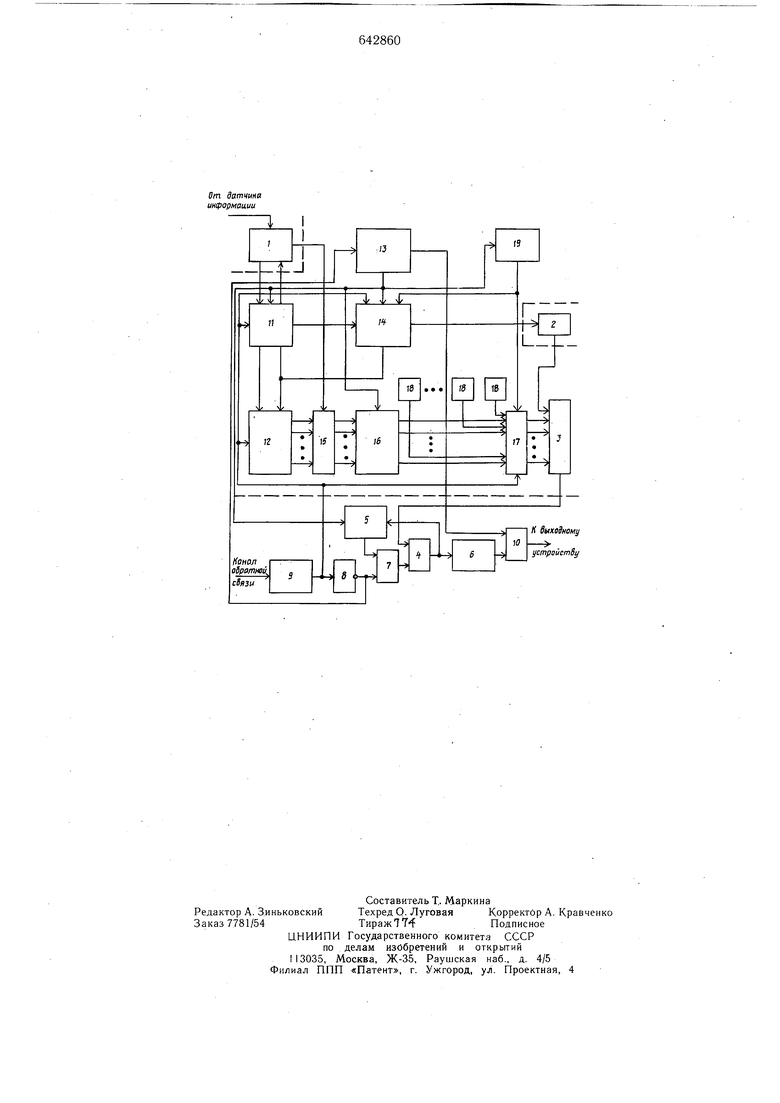

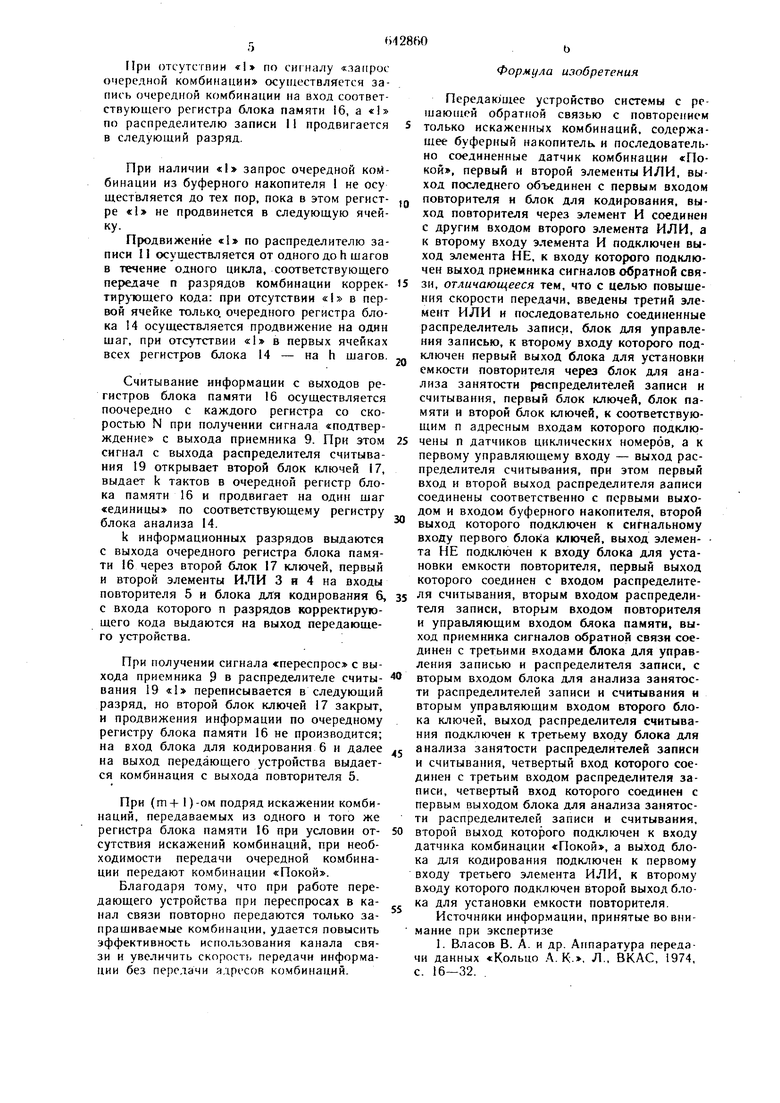

ка для установки емкости повторителя, первый выход которого соединен с входом распределителя считывания, вторым входом распределителя записи, вторым входом повторителя и управляющим входом блока памяти, выход приемника сигналов обратной связи соединен с третьими входами блока для управления записью и распределителя записи, с вторым входом блока для анализа занятости распределителей записи и считывания и вторым управляющим входом второго блока-ключей, выход распределителя считывания подключен к третьему входу блока для анализа занятости распределителей записи и считывания, четвертый ВХОД которого соединен с третьим входом распределителя записи, четвертый вход которого соединен с первым выходом блока для анализа занятости распределителей записи и считывания, второй выход которого подключен к входу датчика комбинации «Покой, а выход блока длякодирования подключен к первому входу третьего элемента ИЛИ, к второму входу которого подключен второй выход блока для установки емкости повторителя. На чертеже приведена структурная электрическая схема устройства. Передающее устройство системы с решающей обратной связью с повторением только искаженных комбинаций содержит буферный накопитель и последовательно соединенные датчик комбинации «Покой 2, первый 3 и второй 4 элементы ИЛИ, выход последнего объединен с первым входом повторителя 5, и блоком для кодирования 6, выход повторителя 5 через элемент И 7 соединен с другим входом второго элемента ИЛИ 4, а к второму входу элемента И7 подключен выход элемента НЕ 8, к входу которого подключен выход приемника 9 сигналов обратной связи, а также третий элемент ИЛИ 10 н последовательно соединенные распределитель записи 11, блок 12 для управления записью, к второму входу которого подключен первый выход блока 13 для установки емкости повторителя через блок 14 для анализа занятости распределителей записи и считывания, первый блок ключей 15, блок памяти 16 и второй блок ключей 17, к соответствующим п адресным входам которого подключены п датчиков 18 циклических номеров, а к первому управляющему входу - выход распределителя считывания 19, при этом первый вход и второй выход распределителя записи 11 соединены с первыми выходом и входом буферного накопителя 1 соответственно, второй выход которого подключен к сигнальному входу первого блока ключей 15, выход элемента НЕ 8. подключен к входу блока 13 для установки емкости повторителя, первый выход которого соединен с входом распределителя считывания 19, вторым входом распределителя записи П, вторым входом повторителя 5 и управляющим входом блока памяти 16,. выход приемника 9 сигналов обратной связи соединен с третьими входами блока 12 для управления записью и распределителя записи II, с вторым входом блока 14 для анализа занятости распределителей записи и считывания и вторым управляющим входом второго блока ключей 17, выход распределителя 19 считывания подключен к третьему входу блока 14 для анализа занятости распределителей записи и считывания, четвертый вход которого соединен с третьим входом распределителя записи 11, четвертый вход которого соединен с первым выходом блока 14 для анализа занятости распределителей записи и считывания, второй выход которого подключен к входу датчика комбинации «Покой 2, а выход блока для кодирования 6 подключен к первому входу третьего элемента ИЛИ 10, к второму входу которого подключен второй выход блока 13 для установки емкости повторителя. Устройство работает следующим образом. В исходном состоянии блок памяти 16 и блок 14 для анализа свободны от информации, а положение распределителя записи И и распределителя считывания 19 обеспечивает готовность остальных блоков к записи комбинации на вход блока памяти 16, при этом разрещается работа датчика комбинации «Покой 2 и выдача этих комбинаций на выход через элемент ИЛИ 4 и блок для кодирования 6. В режиме «передача информации каждая группа из k информационных разрядов. соответствующих одной комбинации, с вы1 со скохода буферного накопителя ростью T(N-h-ni, где N - скорость передачи информации в канале связи; h - количество повторяемых комбинаций при запросе; m - емкость регистров блока памяти 16; через первый блок ключей 15 поочередно записывается в блок памяти 16. Открывание первого блока ключей 15 каждого в течение записи k разрядов осуществляется распределителем записи 11 с помощью блока 12. По мере записи k разрядов в блок памяти 16 на вход блока 14 записывается «I. После записи каждой группы из k разрядов «I в распределителе выдается сигнал «запрос очередной комбинации в буферный накопнтель 1. Продвижение информации по каждому регистру блока памяти 16 осуществляется со скоростью Ti до ближайшей занятой ячейки, занятость ячейки perHctpa блока памяти 16 определяется наличием «I в соответствующем регистре блока 14. Продвижение «I по распределителю записи 11 определяется наличием «U в первых ячейках регистров блока 14, При отсутствии «1 по сигналу «запрос очередной комбинации осуществляется запись очередной комбинации на вход соответствующего регистра блока памяти 16, а «1 по распределителю записи II продвигается в следующий разряд. При наличии «1 запрос очередной комбинации из буферного накопителя I не осу ществляется до тех пор, пока в этом регистре «1 не продвинется в следующую ячейку. Продвижение «1 по распределителю записи II осуществляется от одного до h шагов в течение одного цикла, соответствующего передаче п разрядов комбинации корректирующего кода: при отсутствии «I в первой ячейке только, очередного регистра блока 14 осуществляется продвижение на один щаг, при отсутствии «1 в первых ячейках всех регистров блока 14 - на h щагов. Считывание информации с выходов регистров блока памяти 16 осуществляется поочередно с каждого регистра со скоростью N при получении сигнала «подтверждение с выхода приемника 9. При этом сигнал с выхода распределителя считывания 19 открывает второй блок ключей 17, выдает k тактов в очередной регистр блока памяти 16 и продвигает на один щаг «единицы по соответствующему регистру блока анализа 14. k информационных разрядов выдаются с выхода очередного регистра блока памяти 16 через второй блок 17 ключей, первый и второй элементы ИЛИ 3 и 4 на входы повторителя 5 и блока дяя кодирования 6, с входа которого п разрядов корректирующего кода выдаются на выход передающего устройства.; При получении сигнала «переспрос с выхода приемника 9 в распределителе считывания 19 «1 переписывается в следующий разряд, но второй блок ключей 17 закрыт, и продвижения информации по очередному регистру блока памяти 16 не производится; на вход блока для кодирования 6 и далее на выход передающего устройства выдается комбинация с выхода повторителя 5. При (т+ 1)-ом подряд искажении комбинаций, передаваемых из одного и того же регистра блока памяти 16 при условии отсутствия искажений комбинаций, при необходимости передачи очередной комбинации передают комбинации «Покой. Благодаря тому, что при работе передающего устройства при переспросах в канал связи повторно передаются только запращиваемые комбинации, удается повысить эффективнсхгть использования канала связи и увеличить скорость передачи информации без передачи адресов комбинаций. Формула изобретения Передающее устройство системы с решаюЕНсй обратной связью с повторением только искаженных комбинаций, содержащее буферный накопитель, и последовательно соединенные датчик комбинации «Покой, первый и второй элементы ИЛИ, выход последнего объединен с первым входом повторителя и блок для кодирования, выход повторителя через элемент И соединен с другим входом второго элемента ИЛИ, а к второму входу элемента И подключен выход элемента НЕ, к входу которого подключен выход приемника сигналов обратной связи, отличающееся тем, что с целью повышения скорости передачи, введены третий элемент ИЛИ и последовательно соединенные распределитель записи, блок для управления записью, к второму входу которого подключен первый выход блока для установки емкости повторителя через блок для анализа занятости распределителей записи и считывания, первый блок ключей, блок памяти и второй блок ключей, к соответствующим п адресным входам которого подключены п датчиков циклических номеров, а к первому управляющему входу - выход распределителя считыв-ания, при этом первый вход и второй выход распределителя записи соединены соответственно с первыми выходом и входом буферного накопителя, второй выход которого подключен к сигнальному входу первого блока ключей, выход элемен- та НЕ подключен к входу блока для установки емкости повторителя, первый выход которого соединен с входом распределите считывания, вторым входом распределителя записи, вторым входом повторителя и управляющим входом блока памяти, выход приемника сигналов обратной связи соединен с третьими входами блока для управления записью и распределитепя записи, с вторым входом блока для анализа занятости распределителей записи и считывания и вторым управляющим входом второго блока ключей, выход распределителя считывания подключен к третьему входу блока для анализа занятости распределителей записи И считывания, четвертый вход которого динен с третьим входом распределителя записи, четвертый вход которого соединен с первым выходом блока для анализа занятости распределителей записи и считывания, второй выход которого подключен к входу датчика комбинации «Покой, а выход блока .для кодирования подключен к первому входу третьего элемента ИЛИ, к второму входу которого подключен второй выход блока для установки емкости повторителя. Источники информации, принятые во внимание при экспертизе 1. Власов В. А. и др. Аппаратура передачи данных «Кольцо .. К., Л., ВКАС, 1974, с. 16-32. .

От датчика информации

ycmpaucmSy

| название | год | авторы | номер документа |

|---|---|---|---|

| Передающее устройство системы с решающей обратной связью | 1984 |

|

SU1239875A1 |

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401468A1 |

| Устройство для сопряжения абонентов с каналами связи | 1984 |

|

SU1233158A1 |

| Устройство для определения заданной ординаты корреляционной функции | 1990 |

|

SU1777152A1 |

| Векторно-потоковое операционное устройство | 1989 |

|

SU1734100A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

Авторы

Даты

1979-01-15—Публикация

1976-02-10—Подача