(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Цифровой коррелятор | 1989 |

|

SU1711181A1 |

| Цифровой синтезатор сигналов | 1988 |

|

SU1525694A1 |

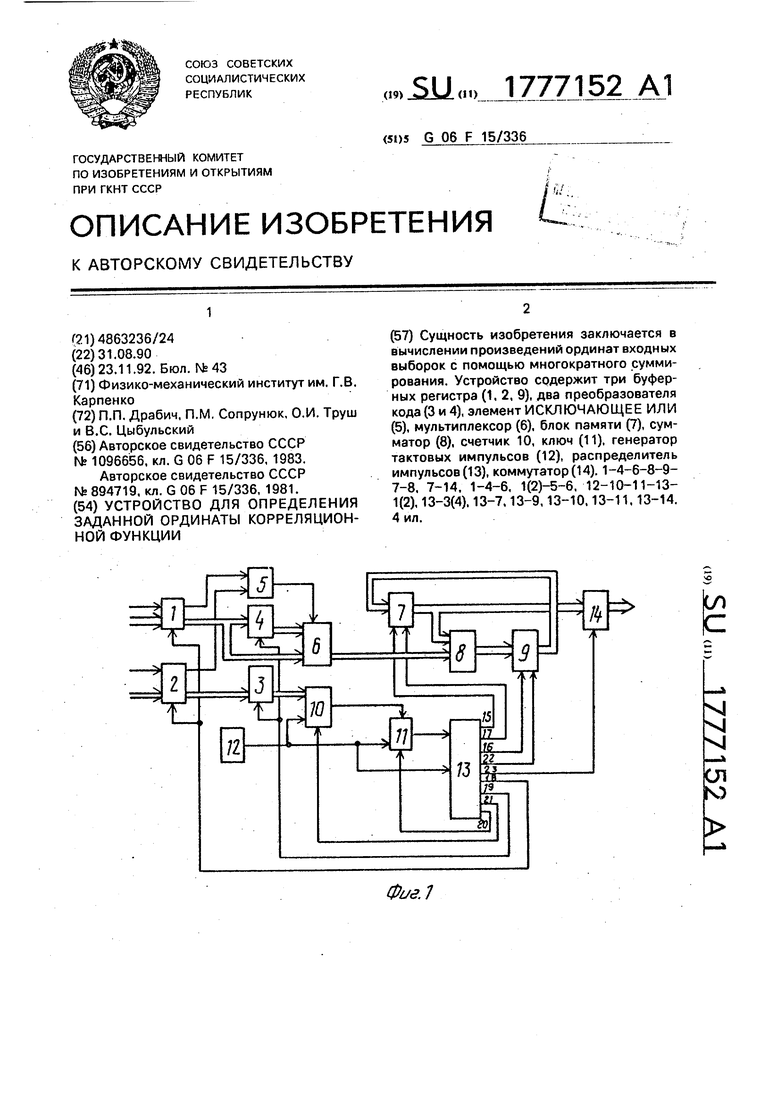

Сущность изобретения заключается в вычислении произведений ординат входных выборок с помощью многократного суммирования. Устройство срдержит три буферных регистра (1, 2, 9), два преобразователя кода(3 и 4), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

ФигЛ

Изобретение относится к вычислительной технике и может быть использовано для корреляционного анализа непрерывных случайных процессов.

Целью изобретения является упрощение устройства и снижение аппаратурных затрат.

Заявляемое устройство осуществляет определение ординат корреляционной функции в соответствии с алгоритмом

X );

V,

где Kxy{in At)- взаимокорреляционная функция процессов Ј{t), y(t);

N - число отсчетов;

К -1,2... N;

L- максимальная задержка;

m-1,2... L

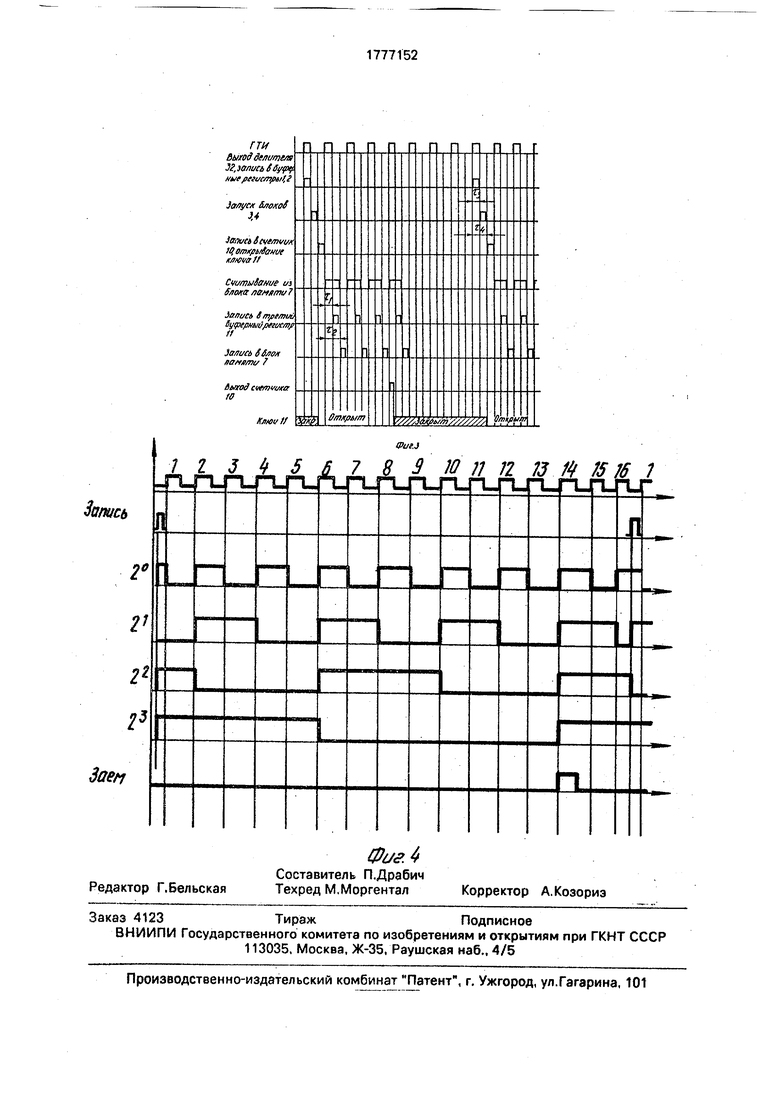

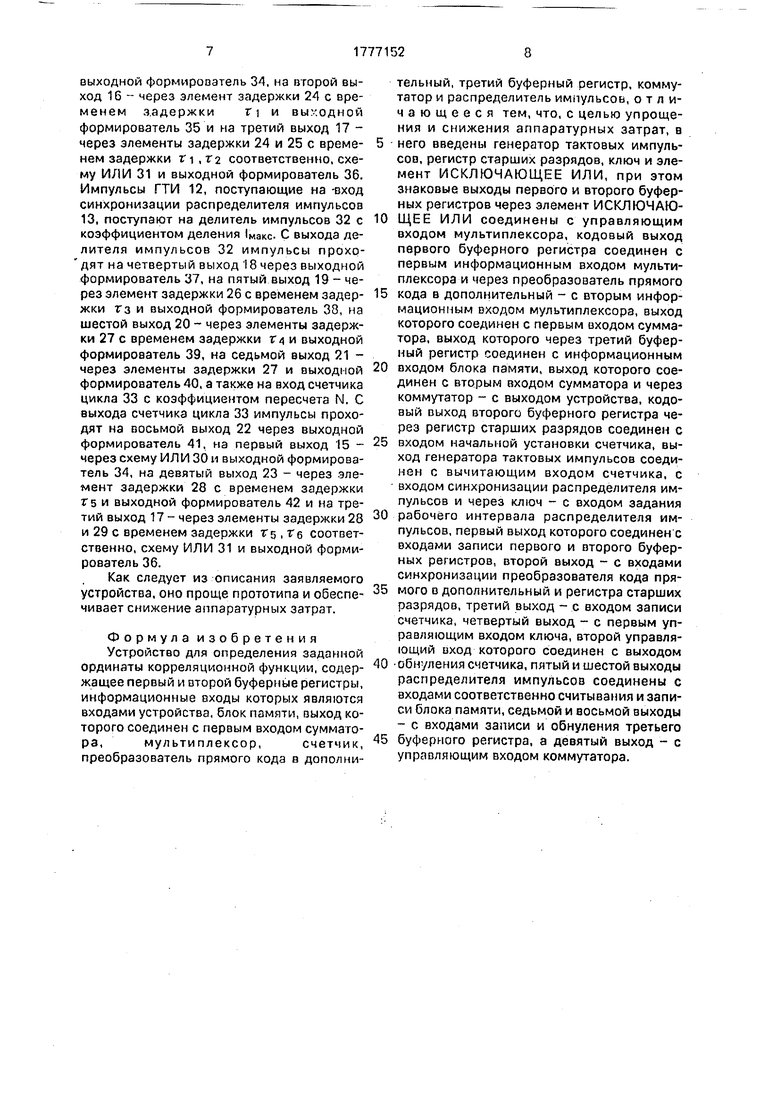

На фиг. 1 представлена блок-схема заявляемого устройства; на фиг. 2 - один из возможных вариантов построения распределителя импульсов; на фиг. 3 приведена временная диаграмма работы коррелятора при , на фиг. 4 показан пример работы счетчика при , .1махс 16.

Предлагаемый коррелятор содержит первый и второй буферные блоки К и 2, регистр старших разрядов 3, преобразователь прямого кода в дополнительный 4, схему ИСКЛЮЧАЮЩЕЕ ИЛИ 5, мультиплексор

6,блок памяти 7, сумматор 8, третий буферный регистр 9, счетчик 10, ключ 11, генератор тактовых импульсов (ГТИ) 12. распределитель импульсов 13 и коммутатор 14. Информационные (знаковые и кодовые) входы первого и второго буферных регистров 1 и 2 являются входами коррелятора, кодовый выход первого буферного регистра соединен с первым информационным входом мультиплексора 6 и через преобразователь прямого кода в дополнительный 4 -- с вторым информационным входом мультиплексора б, выход которого соединен с первым входом сумматора 8, второй вход которого соединен с выходом блока памяти

торого соединен с первым управляющим входом ключа 11, выход генератора тактовых импульсов 12 подключен к счетному входу счетчика 10, к входу синхронизации

5 распределителя импульсов 13 и через ключ 11 - к входу задания рабочего интервала распределителя импульсов 13. Вход коммутатора 14 соединен с выходом блока памяти 7, а выход является выходом коррелятора в

10 целом. Первый выход 15 распределителя импульсов 13 соединен с управляющим входом считывания блока памяти 7, второй выход 16 - с управляющим входом записи третьего буферного регистра 9, третий вы15 ход 17-суправляющим оходом записи блока памяти 7, четвертый выход 18 с управляющими входами первого и второго буферного регистров 1 и 2, пятый выход 19 - с управляющими входами регистра стар20 ших разрядов 3 и преобразователя прямого кода в дополнительный 4, шестой выход 20 -с вторым управляющим входом ключа 11, седьмой выход 21 - с управляющим входом счетчика 10, восьмой выход 22 - с управля25 ющим входом коммутатора 14 и девятый выход 23 - с входом обнуления третье/о буферного регистра 9./

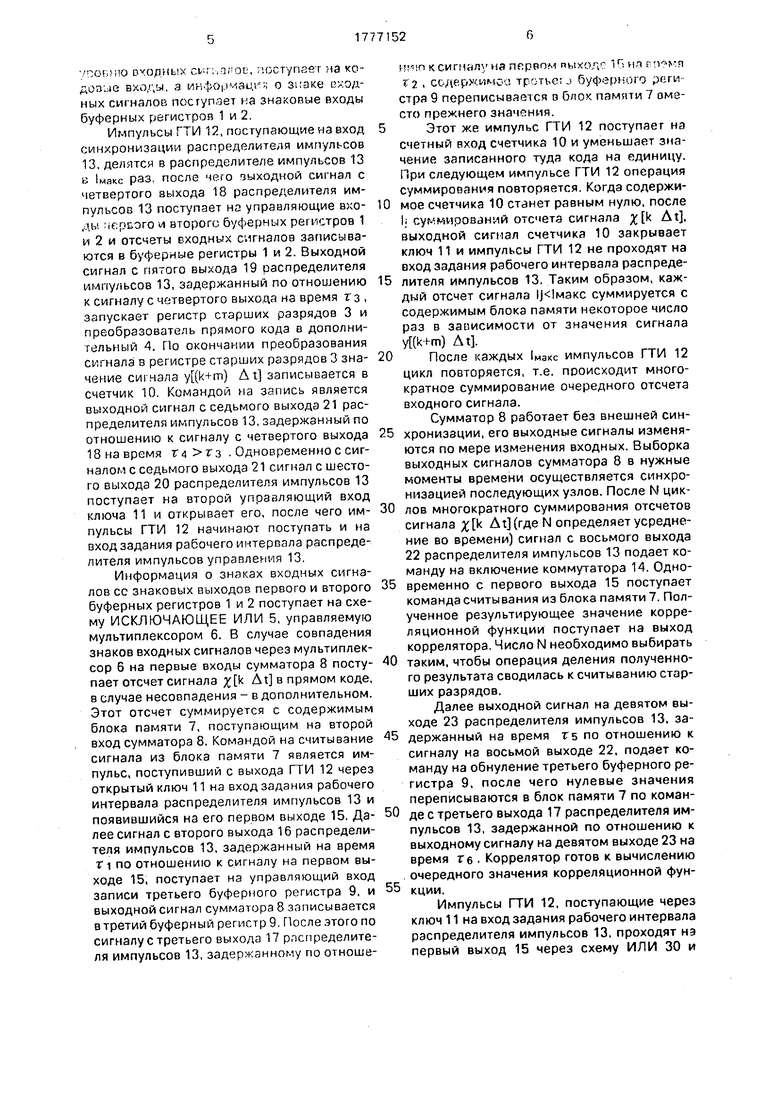

Один из возможных вариантов построения распределителя импульсов 13 приве30 деи на фиг, 2. Распределитель импульсов состоит из элементов задержки 24-29, схем ИЛИ 30 и 31, делителя импульсов 32, счетчика цикла 33, выходных формирователей 34-42. Выходные формирователи предназ35 начены для формирования управляющих сигналов с необходимыми параметрами.

Значение lj определяется уровнем сигнала y(k+m) A t и находится в пределах 0 j iMaKc. Необходимую точность определе40 ния корреляционной функции можно обеспечить даже при небольшом значении макс, при этом погрешность можно значительно уменьшить, если сигнал y(k+m) At будет кодирован нелинейно, а закон нели45 мейности поставить в зависимость от закона распределения значений входного сигнала 4. При этом устройство несколько упростится за сче г уменьшения числа разрядов, а также увеличится быстродействие ус50 тройства, Загрублемие входного сигнала, а также преобразование линейного кода сигнала y(k+m) At в нелинейный выполняет регистр старших разрядов 3.

Заявленное устройство работает следу55 ющим образом.

Отсчеты входных сигналов Д t и y(k+m) At поступают на информационные аходы первого и второго буферных регистре 1 и 2, при этом код, .соответствующий

.V

.vo сводных ci г,л; oi, лостумаег на кодовое входы, а ипфоцмацк;, о входных сигналов поступает на знаковые входы буферных регистров 1 и 2.

Импульсы ГТИ 12, поступающие из вход синхронизации распределителя импульсов 13, делятся в распределителе импульсов 13 в макс раз после чего выходной сигнал с четвертого выхода 18 распределителя импульсов 13 поступает на управляющие входы itpcoro и второго буферных регистров 1 и 2 и отсчеты входных сигналов записываются в буферные регистры 1 и 2. Выходной сигнал с пятого выхода 19 оаспределителя импульсов 13, задержанный по отношению к сигналу с четвертого выхода на время т з , запускает регистр старших разрядов 3 и преобразователь прямого кода в дополнительный 4. По окончании преобразования сигнала в регистре старших разрядов 3 значение CHI чала y(k+m) Atj записывается в счетчик 10. Командой на запись является выходной сигнал с седьмого выхода 21 распределителя импульсов 13, задержанный по отношению к сигналу с четвертого выхода 18 на время . Одновременное сигналом с седьмого выхода 21 сигнал с шестого выхода 20 распределителя импульсов 13 поступает на второй управляющий вход ключа 11 и открывает его, после чего импульсы ГТИ 12 начинают поступать и на вход задания рабочего интервала распределителя импульсов управления 13.

Информация о знаках входных сигналов со знаковых выходов первого и второго буферных регистров 1 и 2 поступает на схему ИСКЛЮЧАЮЩЕЕ ИЛИ 5, управляемую мультиплексором 6. В случае совпадения знаков входных сигналов через мультиплексор 6 на первые входы сумматора 8 поступает отсчет сигнала At в прямом коде, в случае несовпадения - в дополнительном. Этот отсчет суммируется с содержимым блока памяти 7, поступающим на второй вход сумматора 8, Командой на считывание сигнала из блока памяти 7 является импульс, поступивший с выхода ГТИ 12 через открытый ключ 11 на вход задания рабочего интервала распределителя импульсов 13 и появившийся на его первом выходе 15. Далее сигнал с второго выхода 16 распределителя импульсов 13, задержанный на время т по отношению к сигналу на первом выходе 15, поступает на управляющий вход записи третьего буферного регистра 9, и выходной сигнал сумматора 8 записывается в третий буферный регистр 9. После этого по сигналу с третьего выхода 17 распределителя импульсов 13, задержанному по отноше i n ксигмал 1 на первом пшхолг 1Г нл а г 2 . ссдеру имо третье; j буферного ре г и стра 9 переписывается в блок памяти 7 вместо прежнего значения.

Этот же импульс ГТИ 12 поступает на

счетный вход счетчика 10 и уменьшает значение записанного туда кода на единицу. При следующем импульсе ГТИ 12 операция суммирования повторяется. Когда содержимое счетчика 10 станет равным нулю, после I. суммирований отсчета сигнала k At, выходной сигнал счетчика 10 закрывает ключ 11 и импульсы ГТИ 12 не проходят на вход задания рабочего интервала распределителя импульсов 13. Таким образом, каждый отсчет сигнала суммируется с содержимым блока памяти некоторое число раз в зависимости от значения сигнала yt(kt-m) At.

После каждых макс импульсов ГТИ 12

цикл повторяется, т.е. происходит многократное суммирование очередного отсчета входного сигнала.

Сумматор 8 работает без внешней синхрониззции, его выходные сигналы изменяются по мере изменения входных. Выборка выходных сигналов сумматора 8 в нужные моменты времени осуществляется синхронизацией последующих узлов. После N циклов многократного суммирования отсчетов сигнала At (где N определяет усреднение во времени) сигнал с восьмого выхода 22 распределителя импульсов 13 подает команду на включение коммутатора 14. Одновременно с первого выхода 15 поступает команда считывания из блока памяти 7. Полученное результирующее значение корреляционной функции поступает на выход коррелятора. Число N необходимо выбирать

таким, чтобы операция деления полученного результата сводилась к считыванию старших разрядов.

Далее выходной сигнал на девятом выходе 23 распределителя импульсов 13, задержанный на время rs по отношению к сигналу на восьмой выходе 22, подает команду на обнуление третьего буферного регистра 9. после чего нулевые значения переписываются в блок памяти 7 по команде с третьего выхода 17 распределителя импульсов 13, задержанной по отношению к выходному сигналу на девятом выходе 23 на время г е . Коррелятор готов к вычислению очередного значения корреляционной функции.

Импульсы ГТИ 12, поступающие через ключ 11 на вход задания рабочего интервала распределителя импульсов 13, проходят нз первый выход 15 через схему ИЛИ 30 и

выходной формиропэтель 34, на второй выход 16 - через элемент задержки 24 с временем з.адержки г i и выходной формирователь 35 и на третий выход 17 - через элементы задержки 24 и 25 с временем задержки г ч , г 2 соответственно, схему ИЛИ 31 и выходной формирователь 36. Импульсы ГТИ 12, поступающие на -вход синхронизации распределителя импульсов 13, поступают на делитель импульсов 32 с коэффициентом деления 1Макс- С выхода делителя импульсов 32 импульсы прохо- дят на четвертый выход 18 через выходной формирователь 37, на пятый выход 19 - через элемент задержки 26 с временем задержки тз и выходной формирователь 38, на шестой выход 20 - через элементы задержки 27 с временем задержки г 4 и выходной формирователь 39, на седьмой выход 21 - через элементы задержки 27 и выходной формирователь 40, а также на вход счетчика цикла 33 с коэффициентом пересчета N. С выхода счетчика цикла 33 импульсы проходят на восьмой выход 22 через выходной формирователь 41. на первый выход 15 - через схему ИЛИ 30 и выходной формирователь 34, на девятый выход 23 - через -элемент задержки 28 с временем задержки г s и выходной формирователь 42 и на третий выход 17 - через элементы задержки 28 и 29 с временем задержки г 5 , т в соответственно, схему ИЛИ 31 и выходной формирователь 36.

Как следует из описания заявляемого устройства, оно проще прототипа и обеспечивает снижение аппаратурных затрат.

Формула изобретения Устройство для определения заданной ординаты корреляционной функции, содержащее первый и второй буферные регистры, информационные входы которых являются входами устройства, блок памяти, выход которого соединен с первым входом сумматора,мультиплексор,счетчик, преобразователь прямого кода в дополнительный, третий буферный регистр, коммутатор и распределитель импульсов, отличающееся тем, что, с целью упрощения и снижения аппаратурных затрат, в

него введены генератор тактовых импульсов, регистр старших разрядов, ключ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом знаковые выходы первого и второго буферных регистров через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с управляющим входом мультиплексора, кодовый выход первого буферного регистра соединен с первым информационным входом мультиплексора и через преобразователь прямого

кода в дополнительный - с вторым информационным входом мультиплексора, выход которого соединен с первым входом сумматора, выход которого через третий буферный регистр соединен с информационным

входом блока памяти, выход которого соединен с вторым входом сумматора и через коммутатор - с выходом устройства, кодовый выход второго буферного регистра через регистр старших разрядов соединен с

входом начальной установки счетчика, выход генератора тактовых импульсов соединен с вычитающим входом счетчика, с входом синхронизации распределителя импульсов и через ключ - с входом задания

рабочего интервала распределителя импульсов, первый выход которого соединен с входами записи первого и второго буферных регистров, второй выход - с входами синхронизации преобразователя кода прямого в дополнительный и регистра старших разрядов,третий выход - с входом записи счетчика, четвертый выход - с первым управляющим входом ключа, второй управляющий вход которого соединен с выходом

0 -обнуления счетчика, пятый и шестой выходы распределителя импульсов соединены с входами соответственно считывания и записи блока памяти, седьмой и восьмой выходы - с входами записи и обнуления третьего

5 буферного регистра, а девятый выход - с управляющим входом коммутатора.

«

3

-i

ЗВШЬ

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-23—Публикация

1990-08-31—Подача