4

О5 00

Изобретение относится к вычислительной технике и может быть использовано в системах обмена данными в качестве устройства буферной памяти.

Целью изобретения является повыше ние коэффициента готовности устройства за счет сокращения времени поиска неисправности.

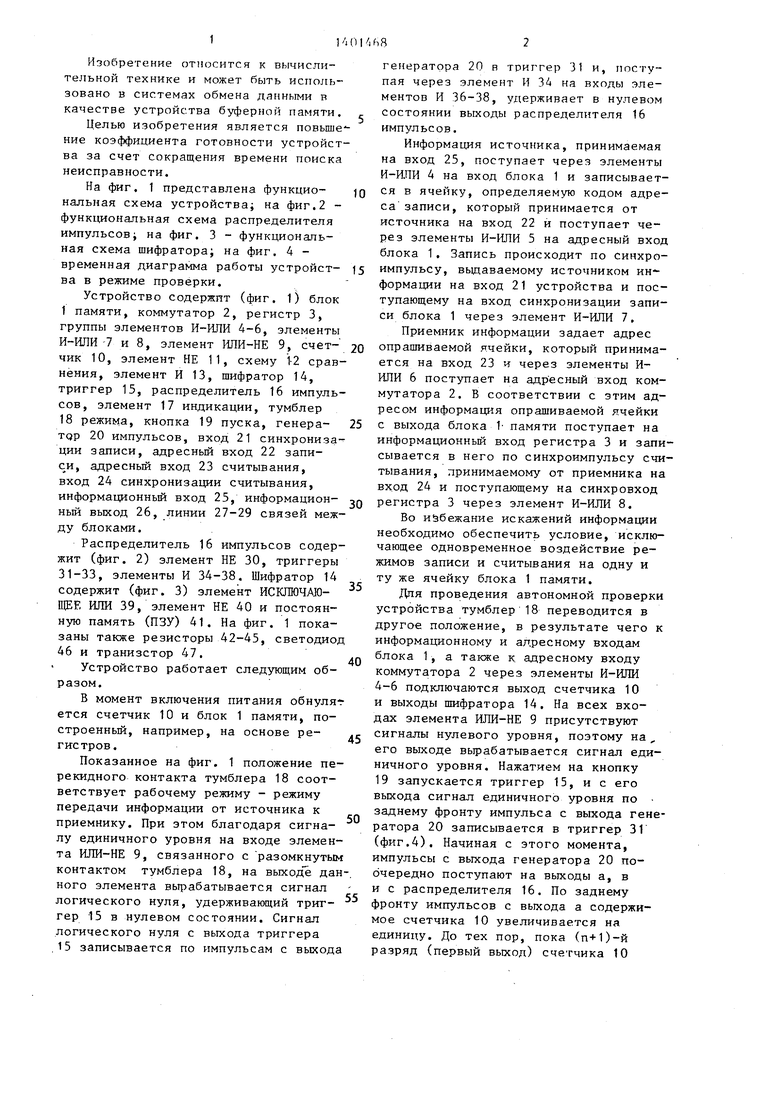

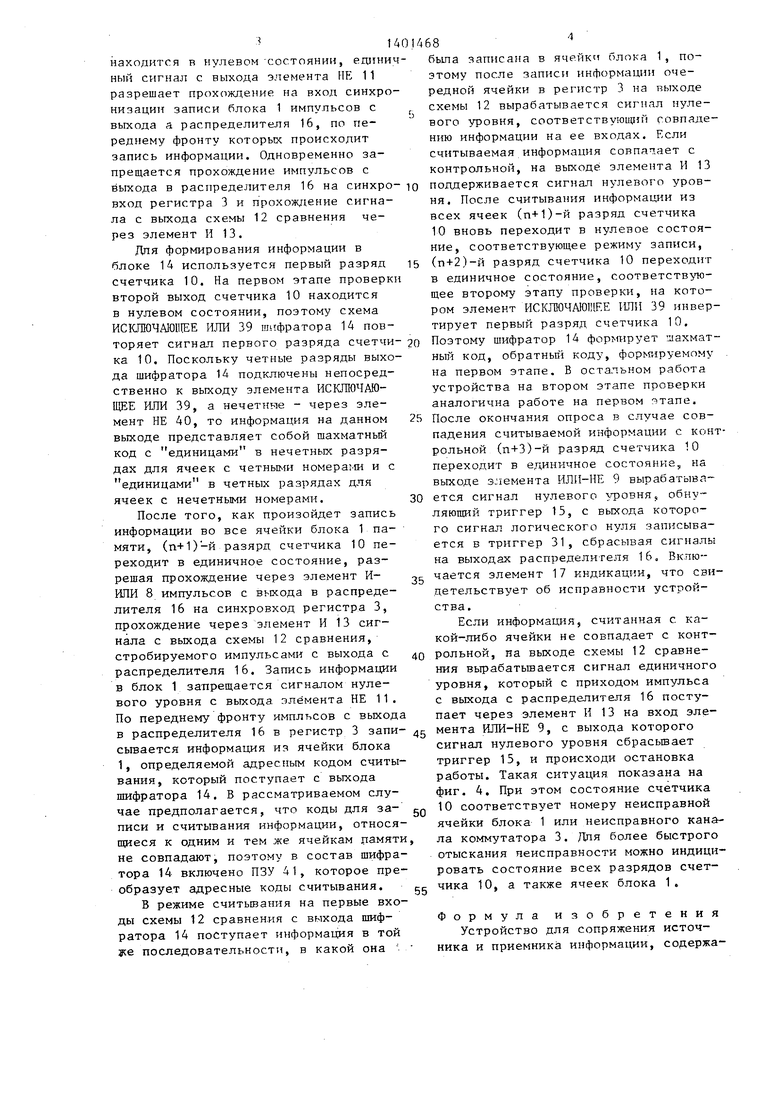

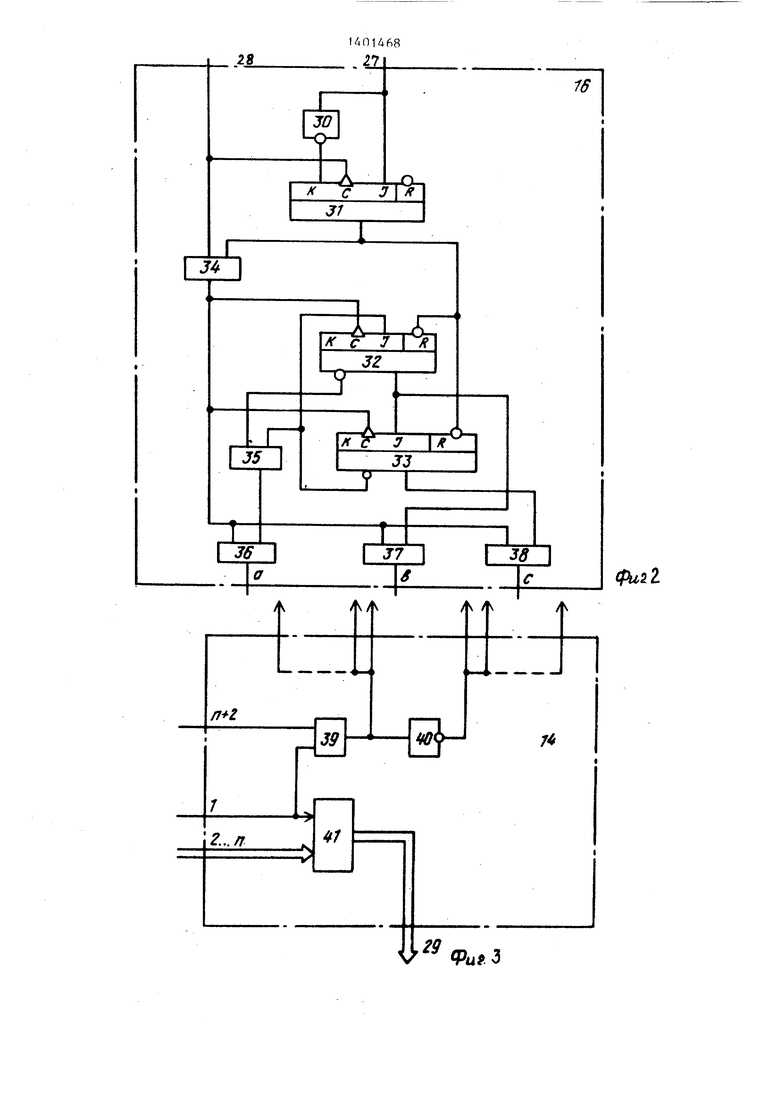

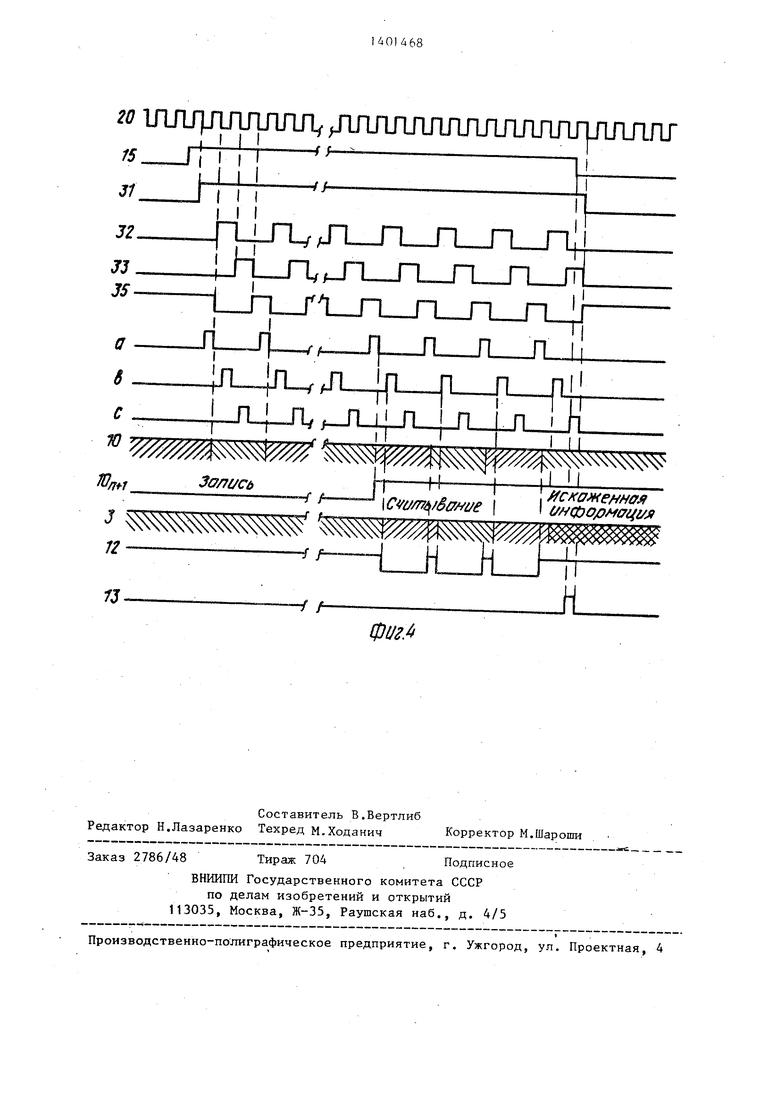

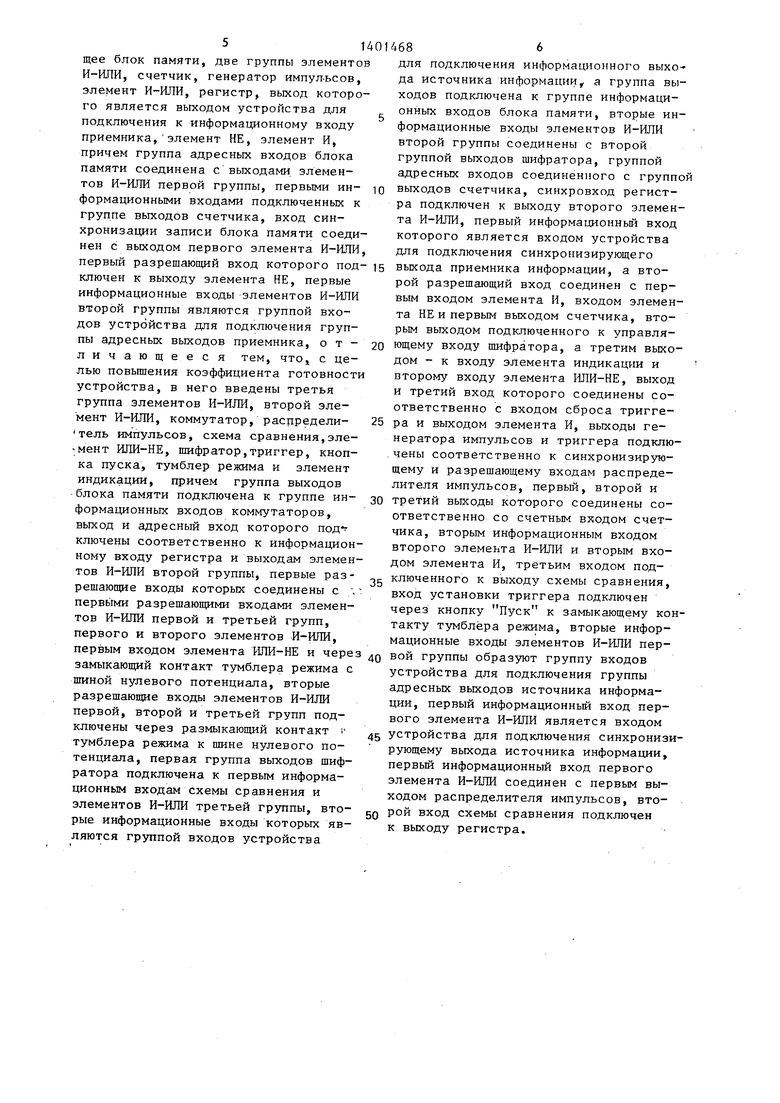

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - функ1Ц1ональная схема распределителя импульсов; на фиг. 3 - функциональная схема шифратора; на фиг. 4 - временная диаграмма работы устройства в режиме проверки.

Устройство содержит (фиг. 1) блок 1 памяти, коммутатор 2, регистр 3, группы элементов И-ИЛИ 4-6, элементы И-ИЛИ-7 и 8, элемент ИЛИ-НЕ 9, счетчик 10, элемент НЕ 11, схему 1-2 сравнения, элемент И 13, шифратор 14, триггер 15, распределитель 16 импульсов, элемент 17 индикации, тумблер 18 режима, кнопка 19 пуска, генера- TQP 20 импульсов, вход 21 синхронизации записи, адресный вход 22 записи, адресный вход 23 считывания, вход 24 синхронизации считывания, информационньй вход 25, информацион- ньй выход 26, линии 27-29 связей между блоками.

Распределитель 16 импульсов содержит (фиг. 2) элемент НЕ 30, триггеры 31-33, элементы И 34-38. Шифратор 14 содержит (фиг. 3) элемент ИСКЛЮЧАЮЩЕЕ ШШ 39, элемент НЕ 40 и постоянную память (ПЗУ) 41. На фиг. 1 показаны также резисторы 42-45, светодиод 46 и транизстор 47.

Устройство работает следующим образом.

В момент включения питания обнуляв ется счетчик 10 и блок 1 памяти, построенный, например, на основе регистров.

Показанное на фиг. 1 положение перекидного контакта тумблера 18 соответствует рабочему режиму - режиму передачи информации от источника к приемнику. При этом благодаря сигналу единичного уровня на входе элемента ИЛИ-НЕ 9, связанного с разомкнутым контактом тумблера 18, на выход е дан ного элемента вьфабатывается сигнал логического нуля, удерживающий триггер 15 в нулевом состоянии. Сигнал логического нуля с выхода триггера 15 записывается по импульсам с вькод

0

5

0

5

0

5

0

5

0

5

генератора 20 в триггер 31 и, поступая через элемент И 34 на входы элементов И 36-38, удерживает в нулевом состоянии выходы распределителя 16 импульсов.

Информация источника, принимаемая на вход 25, поступает через элементы И-ИПИ 4 на вход блока 1 и записывается в ячейку, определяемую кодом адреса записи, который принимается от источника на вход 22 и поступает через элементы И-РШИ 5 на адресный вход блока 1. Запись происходит по синхроимпульсу, вьщаваемому источником ин формации на вход 21 устройства и поступающему на вход синхронизации записи блока 1 через элемент И-ИЛИ 7.

Приемник информации задает адрес опрашиваемой ячейки, который принимается на вход 23 и через элементы И- ИЛИ 6 поступает на адресный вход коммутатора 2. В соответствии с этим адресом информация опрашиваемой ячейки с выхода блока 1- памяти поступает на информационный вход регистра 3 и записывается в него по синхроимпульсу считывания, принимаемому от приемника на вход 24 и поступающему на синхровход регистра 3 через элемент И-ИЛИ 8.

Во избежание искажений информации необходимо обеспечить условие, исключающее одновременное воздействие режимов записи и считывания на одну и ту же ячейку блока 1 памяти.

Для проведения автономной проверки устройства тумблер 18 переводится в другое положение, в результате чего к информационному и адресному входам блока 1, а также к адресному входу коммутатора 2 через элементы И-ШШ 4-6 подключаются выход счетчика 10 и выходы шифратора 14. На всех входах элемента ИЛИ-НЕ 9 присутствуют сигналы нулевого уровня, поэтому на, его выходе вьфабатывается сигнал единичного уровня. Нажатием на кнопку 19 запускается триггер 15, и с его выхода сигнал единичного уровня по заднему фронту импульса с выхода генератора 20 записывается в триггер 31 (фиг.4). Начиная с этого момента, импульсы с выхода генератора 20 поочередно поступают на выходы а, в и с распределителя 16. По заднему фронту импульсов с выхода а содержимое счетчика 10 увеличивается на единицу. До тех пор, пока (п+1)-й разряд (первый выход) счетчика 10

находится в нулевом состоянии, единичный сигнал с выхода элемента Ш 11 разрешает прохождение на вход синхронизации записи блока 1 импульсов с

выхода а распределителя 16, по переднему фронту которых происходит запись информации. Одновременно запрещается прохождение импульсов с выхода в распределителя 16 на синхро- вход регистра 3 и прохождение сигнала с выхода схемы 12 сравнения через элемент И 13.

Дпя формирования информации в блоке 14 используется первый разряд счетчика 10. На первом этапе проверки второй выход счетчика 10 находится в нулевом состоянии, поэтому схема ИСКЛЮЧАЮ111ЕЕ И.ПИ 39 шифратора 14 пов

была записана в ячейки блока 1, поэтому после записи информации очередной ячейки в регистр 3 на выходе схемы 12 вырабатывается сигнал нулевого уровня, соответствуюид1й совпадению информации на ее входах. Если считываемая информация совпадает с контрольной, на вьгходё элемента И 13 поддерживается сигнал нулевого уровня. После считывания информации из всех ячеек (п+1)-й разряд счетчика 10 вновь переходит в нулевое состояние, соответствующее режиму записи, (п+2)-й разряд счетчика 10 переходит в единичное состояние, соответствующее второму этапу проверки, на котором элемент ИСКЛЮЧАЮЩЕЕ 1ШИ 39 инвертирует первый разряд счетчика 10.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для организации очередности приема информации | 1983 |

|

SU1128255A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Устройство для проверки полноты тестирования программ | 1989 |

|

SU1693607A1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1686432A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1166125A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1580383A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обмена данными в качестве устройства буферной памяти. Устройство обеспечивает прием цифровой информации от источника, хранение ее в блоке памяти и передачу в приемник информации. Целью изобретения является повышение коэффициента готовности устройства. Это достигается путем обеспечения автономной проверки работоспособности устройства за счет имитации работы источника и приемника информации, сравнения считываемой информации, записанной в блок памяти, и индикаи1ии результата проверки. Устройство содержит блок 1 памяти, коммутатор 2, регистр 3, три группы злементов И-ИЛИ 4, 5 и 6, злементы И-1ШИ 7 и 8, ИЛИ-НЕ 9, счетчик 10, злемент НЕ 11, схему 12 сравнения, элемент И 13, шифратор 14, триггер 15, расцределитель 16 импуль- § сов, злемент 17 индикации, тумблер 18 режима, кнопку 19 пуска, генера- f) тор 20 импульсов, 4 ил.

торяет сигнал первого разряда счетчи- 20 Поэтому шифратор 14 формирует шахмат- ка 10. Поскольку четные разряды выхо- ный код, обратньп1 коду, форьыруемому

да шифратора 14 подключены непосредственно к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 39, а нечетные - через элемент НЕ 40, то информация на данном выходе представляет собой шахматный код с единицами в нечетных разрядах для ячеек с четными номераг-ш и с единицами в четных разрядах для ячеек с нечетными номерами.

После того, как произойдет запись информации во все ячейки блока 1 памяти, (п+1)-й разярд счетчика 10 пе

реходит в единичное состояние, разрешая прохождение через элемент И- ИПИ 8 импульсов с выхода в распределителя 16 на синхровход регистра 3, прохождение через элемент И 13 сигнала с выхода схемы 12 сравнения, стробируемого импульсами с выхода с распределителя 16. Запись информации в блок 1 запрещается сигналом нулевого уровня с выхода элемента НЕ 11. По переднему фронту импльсов с выхода в распределителя 16 в регистр 3 запи- сьгеается информация из ячейки блока 1, определяемой адресным кодом считывания, который поступает с выхода шифратора 14. В рассматриваемом случае предполагается, что коды для за- писи и считывания информации, относящиеся к одним и тем же ячейкам рамяти не совпадают, поэтому в состав шифратора 14 включено ПЗУ 41, которое преобразует адресные коды считывания.

В режиме считьшания на первые входы схемы 12 сравнения с выхода шифратора 14 поступает информация в той же последовательности, в какой она

на первом этапе. В остальном работа устройства на втором этапе проверки аналогична работе на первом этапе.

После окончания опроса в случае совпадения считываемой информации с контрольной {п+3)-й разряд счетчика 10 переходит в единичное состояние, на выходе элемента ИЛИ-НЕ 9 вырабатывается сигнал нулевого уровня, обнуляющий триггер 15, с выхода которого сигнал логического нуля записывается в триггер 31, сбрасывая сигналы на выходах распределителя 16. Включается элемент 17 индикации, что свидетельствует об исправности устройства.

Если информация, считанная с какой-либо ячейки не совпадает с контрольной, па выходе схемы 12 сравнения вырабатьшается сигнал единичного уровня, который с приходом импульса с выхода с распределителя 16 поступает через элемент И 13 на вход элемента ЙЛИ-НЕ 9, с выхода которого сигнал нулевого уровня сбрасьшает триггер 15, и происходи остановка работы. Такая ситуация показана на фиг. 4, При этом состояние счетчика 10 соответствует номеру неисправной ячейки блока 1 или неисправного канала коммутатора 3. Для более быстрого отыскания неисправности можно индицировать состояние всех разрядов счетчика 10, а также ячеек блока 1.

Формула изобретения

Устройство для сопряжения источника и приемника информации, содержащее блок памяти, две группы элементо И-ИЛИ, счетчик, генератор импул-ьсов, элемент И-ИЛИ, регистр, выход которого является выходом устройства для подключения к информационному входу приемника, элемент НЕ, элемент И, причем группа адресных входов блока памяти соединена с выходами элементов И-ИЛИ первой группы, первыми ин- формационными входами подключенных к группе выходов счетчика, вход синхронизации записи блока памяти соединен с выходом первого элемента И-ИЛИ первый разрешающий вход которого под ключен к выходу элемента НЕ, первые информационные входы элементов И-ИЛИ второй группы являются группой входов устройства для подключения группы адресных выходов приемника, о т - личающееся тем, что с целью повьппения коэффициента готовност устройства, в него введены третья группа элементов И-ИЛИ, второй элемент И-ИЛИ, коммутатор, распредели- тель импульсов, схема сравнения,эле- -мент ИЛИ-НЕ, шифратор,триггер, кнопка пуска, тумблер режима и элемент индикации, причем группа выходов блока памяти подключена к группе ин- формационньпс входов коммутаторов, выход и адресный вход которого под ключены соответственно к информационному входу регистра и выходам элементов И-ИЛИ второй группы, первые разрешающие входы которых соединены с ;. первыми разрешающими входами элементов И-ШШ первой и третьей групп, первого и второго элементов И-ИЛИ, первым входом элемента ИЛИ-НЕ и чере замыкающий контакт тумблера режима с шиной нулевого потенциала, вторые разрешающие входы элементов И-ИЛИ первой, второй и третьей групп подключены через размыкающий контакт ; тумблера режима к шине нулевого потенциала, первая группа выходов шифратора подключена к первым информационным входам схемы сравнения и элементов И-ИЛИ третьей группы, вто- рые информационные входы которых являются группой входов устройства

5 о Q g л

5

для подключения информационного выхода источника информации,, а группа выходов подключена к группе информационных входов блока памяти, вторые информационные входы элементов И-ИЛИ второй группы соединены с второй группой выходов шифратора, группой адресных входов соединенного с группой выходов счетчика, синхровход регистра подключен к выходу второго элемента И-ИЛИ, первый информационньй вход которого является входом устройства для подключения синхронизирующего выхода приемника информации, а второй разрешающий вход соединен с первым входом элемента И, входом элемента НЕ и первым выходом счетчика, вторым выходом подключенного к управляющему входу шифратора, а третим выходом - к входу элемента индикации и второму входу элемента ИЛИ-НЕ, выход и третий вход которого соединены соответственно с входом сброса триггера и выходом элемента И, вькоды генератора импульсов и триггера подключены соответственно к синхронизирующему и разрешающему входам распределителя импульсов, первый, второй и третий выходы которого соединены соответственно со счетным входом счетчика, вторым информационным входом второго элемента И-ИЛИ и вторым входом элемента И, третьим входом подключенного к выходу схемы сравнения, вход установки триггера подключен через кнопку Луск к замыкающему контакту тумблера режима, вторые информационные входы элементов И-ИЛИ первой группы образуют группу входов устройства для подключения группы адресных выходов источника информации, первый информационньй вход первого элемента И-ИЛИ является входом устройства для подключения синхронизирующему выхода источника информации, первьй информационный вход первого элемента И-ИЛИ соединен с первым выходом распределителя импульсов, второй вход схемы сравнения подключен к выходу регистра.

lЛJuyшяллл дл/и

15

Л....../.

п I П ii П, I п I

Золась

-f f- h

(

.

12 /J

f.

-/

(

1/нфо мац1/л

ФигА

| Устройство для сопряжения разноскоростных вычислительных устройств | 1984 |

|

SU1183975A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1275454A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1986-11-27—Подача