Входы Входы тегов данных ®«г. 7

7 буферной памяти признаков операции (тегов), К регистров 8 тегов, К преобразователей 9 тегов, селектор тегов 10 и К распределителей 11 тегов. Введенные блоки соединены между собой и указанными выше функциональными элементами соответствующими связями. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для обработки данных | 1987 |

|

SU1536396A1 |

| Программируемый процессор спектральной обработки сигналов | 1982 |

|

SU1092517A1 |

| АСИНХРОННАЯ СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2198422C2 |

Изобретение относится к цифровой вычислительной технике. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит К регистров 1 данных, где К - число компонентов обрабатываемого вектора данных, К блоков 2 буферной памяти данных, селектор 3 данных и К арифметико-логических блоков 4 первой группы, К арифметико-логических блоков 5 второй группы, К коммутаторов 6, К блоков

Изобретение относится к вычислительной технике и может быть применено при построении высокопроизводительных ЭВМ, работающих по принципу потоковой организации процесса обработки информации.

Известно устройство векторной обработки данных, состоящее из векторных процессоров, каждый из которых содержит векторные регистры, распределитель и селектор, соединенные между собой и с векторными регистрами для перемещения векторных элементов данных внутри процессора, другие распределитель и селектор, соединенные с векторными регистрами и между собой через общий распределитель для перемещения векторных элементов между процессорами под управлением команды перемещения векторов.

Устройство реализует потоковую обработку векторных данных под управлением соответствующих команд, записанных заранее в ЗУ. Необходимость вызова кода команды из ЗУ, расшифровка этого кода и формирование последовательности управляющих воздействий при выполнении операций резко снижает эквивалентное быстродействие системы. Кроме того, глубокая конвейеризация процесса обработки информации в таком устройстве затруднена и малоэффективна, так как селекторы и распределители для передачи информации внутри .процессора, а также селекторы и распределители для передачи информации между процессорами соединены с одними и теми же векторными регистрами. Это также снижает производительность устройства.

Известно устройство поточной обработки данных, содержащее два независимых конвейера: исполнительный и командный, который считывает команды из памяти и формирует коды адресов для исполнительного конвейера. Оба конвейера работают синхронно под управлением специального блока управления поточной обработкой. В таком устройстве обеспечена возможность совмещения операций каждого каскада конвейера для каждой отдельной команды. Однако при этом командный конвейер полностью загружен на обработку командной и адресной информации для исполнительного конвейера, который всегда будет отрабатывать адрес или команду только после их получения (формирования), соответствующего вызова из памяти и анализа. Тем самым, несмотря на наличие командного конвейера, потери устройства на формирование и обработку адресной информации не исключены, что снижает производительность системы. Кроме того, имеющийся способ организации поточной обработки информации с помощью исполнительного и командного конвейеров поддержан общим для обоих конвейеров микропрограммным устройством управления, что приводит к дополнительным затратам аппаратуры и снижает гибкость архитектуры устройства при переходе на решение новых классов задач, так как для обеспечения совмещения работы блоков конвейеров потребуется разработка (доработка) новых микропрограмм.

Существенным недостатком указанных устройств является то, что на скалярных участках решения задач их эффективность резко падает, что является одним из основных

факторов, ограничивающих фактическую производительность ЭВМ.

Наиболее близким к предлагаемому является устройство, содержащее набор векторных регистров с адресными счетчиками,

подключенный к соответствующим выходам устройства управления записью, входной селектор, выходы которого подключены к соответствующим входам векторных регистров, выходной селектор, входы которого

подключены к соответствующим выходам векторных регистров, а выходы - к входам сумматора и умножителя поточной обработки, выходы которых соединены с соответствующими входами входного селектора.

Устройство выполняет быстрые операции над данными, записанными в векторные регистры и считываемые с них под действием соответствующей векторной команды. Устройство управления записью

обеспечивает запись исходных данных (результатов) в несколько векторных регистров в зависимости от содержания векторной команды.

В устройстве-прототипе так же, как и в

устройствах-аналогах, реализовано программное (микропрограммное) управление

процессом обработки информации, что сопряжено с потерями времени на вызов команды (микрокоманды) из памяти программ (микропрограмм), ее расшифровку и формирование адресов операндов. Это приводит к изменению в целом быстродействия устройства и снижению в конечном итоге производительности.

Кроме того, архитектура и структура такого операционного устройства, ориентированные на обработку векторных данных, резко снижают свою эффективность на скалярных участках алгоритма решения задачи, что в целом снижает производительность устройства.

Целью изобретения является повышение быстродействия устройства за счет распараллеливания процессов обработки информации и одновременно формирования сигналов, управляющих процессом обработки, а также за счет повышения эффективности реализации унарных операций и скалярных участков реализуемого алгоритма.

Поставленная цель достигается тем, что в векторно-потоковое устройство, содержащее К регистров данных (К - число компонентов обрабатываемого вектора данных), К блоков буферной па.ияти данных, селектор данных и К арифметико-логических блоков первой группы, соединенных соответствующими связями, введены К арифметико-логических блоков второй группы, К коммутаторов, К блоков буферной памяти признаков операции (тегов), К регистров признаков операции (тегов), К преобразователей признаков операции (тегов), селектор признаков операции и К распределителей признаков операции (тегов), соединенные между собой и с указанными выше блоками соответствующими связями. При этом вторые выходы регистров данных с первого по К-й подключены соответственно к информационным входам арифметико-логических блоков с первого по К-й второй группы, первые выходы которых подключены соответственно к вторым информационным входам регистров данных с первого по К-й. Вторые выходы арифметико-логических блоков с первого по К-й второй группы подключены соответственно к вторым информационным входам блоков буферной памяти данных с первого по К-й. Выходы арифметико-логических блоков с первого по К-й первой группы подключены соответственно к информационным входам коммутаторов с первого по К-й, первые выходы которых подключены соответственно к третьим информационным входам регистров данных с первого по К-й. Вторые выходы коммутаторов с первого

по К-й подключены соответственно к третьим информационным входам блоков буферной памяти данных с первого по К-й. Третьи

5 выходы коммутаторов с первого по К-й подключены соответственно к выходам результатов с первого по К-й устройства, с первого по К-й входы признаков операции (тегов) устройства подключены соответственно к первым информационным входам блоков буферной памяти признаков операции (тегов) с первого по К-й, выходы которых под- ключены соответственно к первым информационным входам регистров признаков операции (тегов) с первого по К-й, первые выходы которых подключены соответственно к первым информационным входам преобразователей признаков операции (тегов) с первого по К-й, первые выходы ко0 торых подключены соответственно к вторым информационным входам регистров признаков операции (тегов) с первого по К-й, вторые выходы которых подключены к информационным входам селектора при5 знаков операции (тегов), выходы первой группы которого подключены соответственно к управляющим входам селектора данных. Выходы с первого по К-й второй группы селектора признаков операции (тегов) под0 ключены соответственно к первым информационным входам распределителей признаков операции (тегов) с первого по К-й, первые выходы которых подключены соответственно к третьим информацион5 ным входам регистров признаков операции (тегов) с первого по К-й. Вторые выходы распределителей признаков операции (тегов) с первого по К-й подключены соответственно к вторым информационным входам блоков

0 буферной памяти признаков операции (тегов) с первого по К-й. Третьи выходы распределителей признаков операции (тегов) с первого по К-й подключены соответственно к управляющим входам коммутаторов с пер5 вого по К-й. Четвертые выходы распределителей признаков операции (тегов) с первого по К-й подключены соответственно к входам кода операции арифметико-логических блоков с первого по К-й первой группы, пятые

0 выходы распределителей признаков операции (тегов) с первого по К-й подключены соответственно к выходам с первого по К-й признаков операции (тегов) устройства, входы констант с первого по К-й первой группы

5 которого подключены соответственно к вторым информационным входам распределителей признаков операции (тегов) с первого по К-й. Входы констант с первого по К-й второй группы устройства подключены со0 ответственно к вторым информационным входам преобразователей признаков oneрации (тегов) с первого по К-й, вторые выходы которых подключены соответственно к третьим информационным входам блоков буферной памяти признаков операции (тегов) с первого по К-й. Третьи выходы преобразователей признаков операции (тегов) с первого по К-й подключены соответственно к входам кода операции арифметико-логических блоков с первого по К-й второй груп- пы, вход синхронизации устройства подключен к входам записи/считывания блоков буферной памяти признаков операции (тегов), к входам записи/считывания регистров признаков операции (тегов) и к входам синхронизации преобразователей признаков операции.

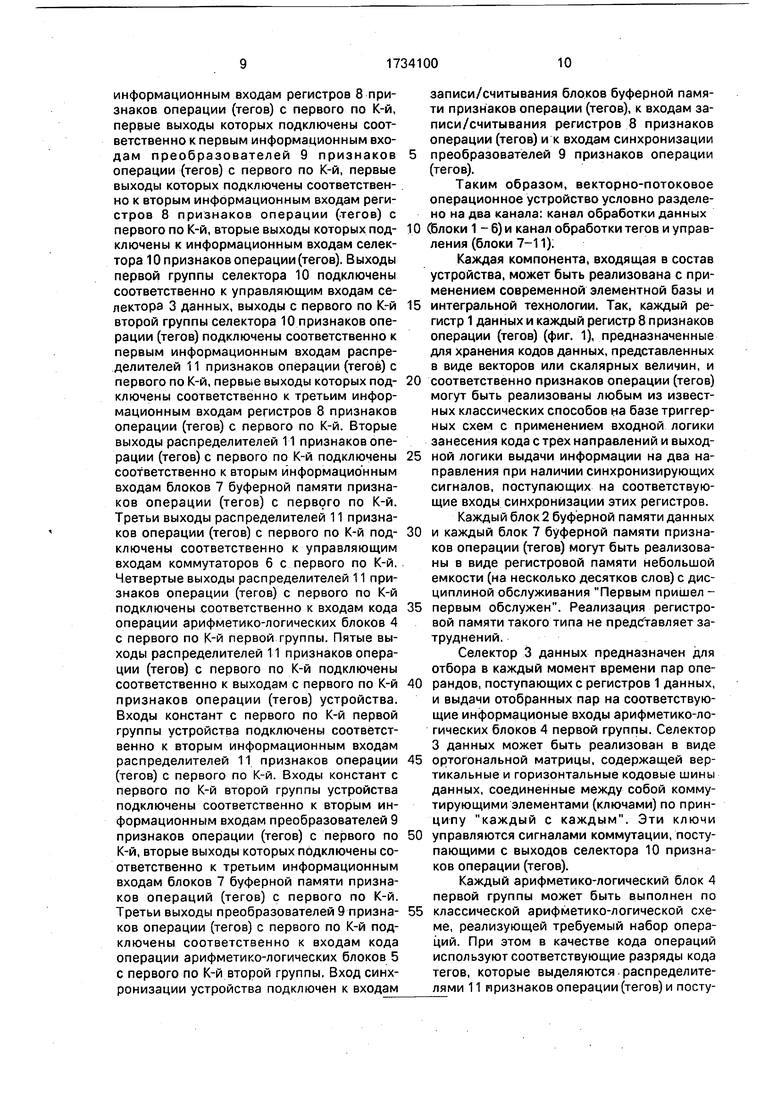

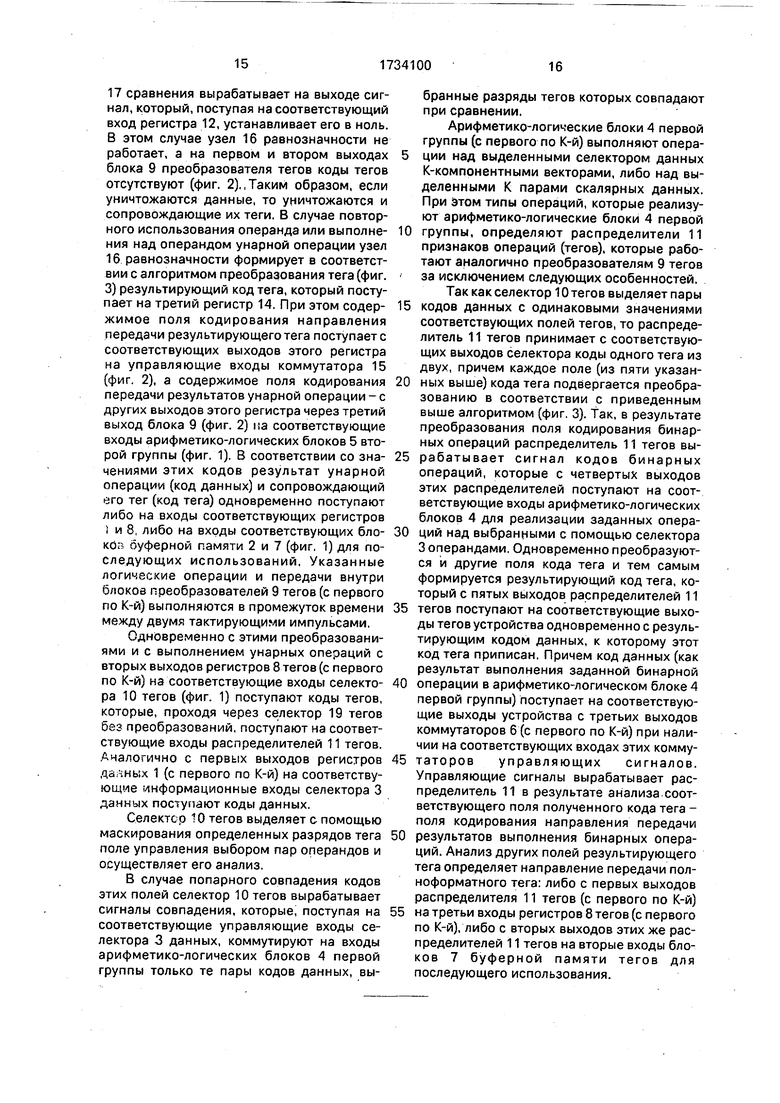

Каждый преобразователь признаков операции (тегов) содержит три регистра, коммутатор, узел равнозначности и узел сравнения со значением признака уничтожения данных. При этом в каждом преобразователе признаков операции (тегов) первый и второй информационные входы преобразователя признаков операции (тегов) подключены соответственно к информационным входам первого и второго регистров. Первый выход первого регистра и выход второго регистра подключены соответственно к первому и второму-входам узла разнозначности, выход которого подключен к информационному входу третьего регистра, первый и второй выходы которого подключены соответственно к информационному и управляющему входам коммутатора, первый и второй выходы которого подключены соответственно к первому и второму выходам преобразователя признаков операции (тегов). Второй выход первого регистра подключен к входу узла сравнения с признаком уничтожения данных, соединен с вторым выходом третьего регистра и подключен к третьему выходу преобразователя признаков операции (тегов), вход синхронизации которого подключен к входам записи/считывания первого, второго и третьего регистров. Выход узла сравнения с признаком уничтожения данных подключен к входу установки в ноль первого регистра.

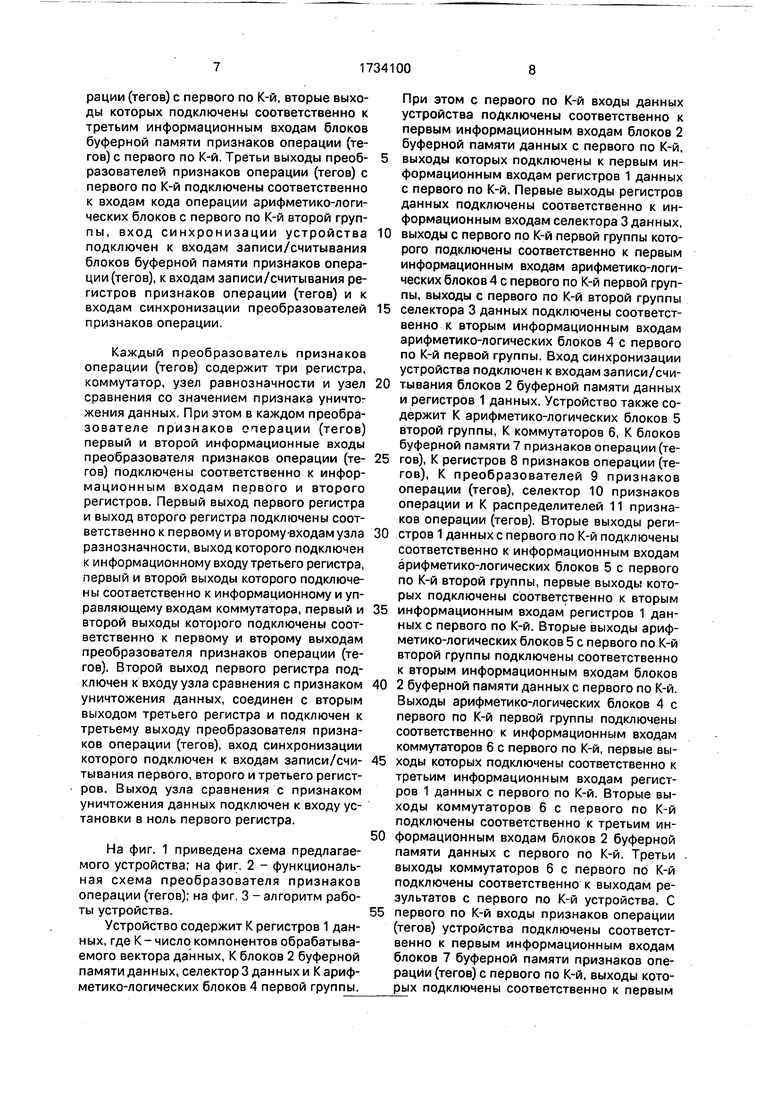

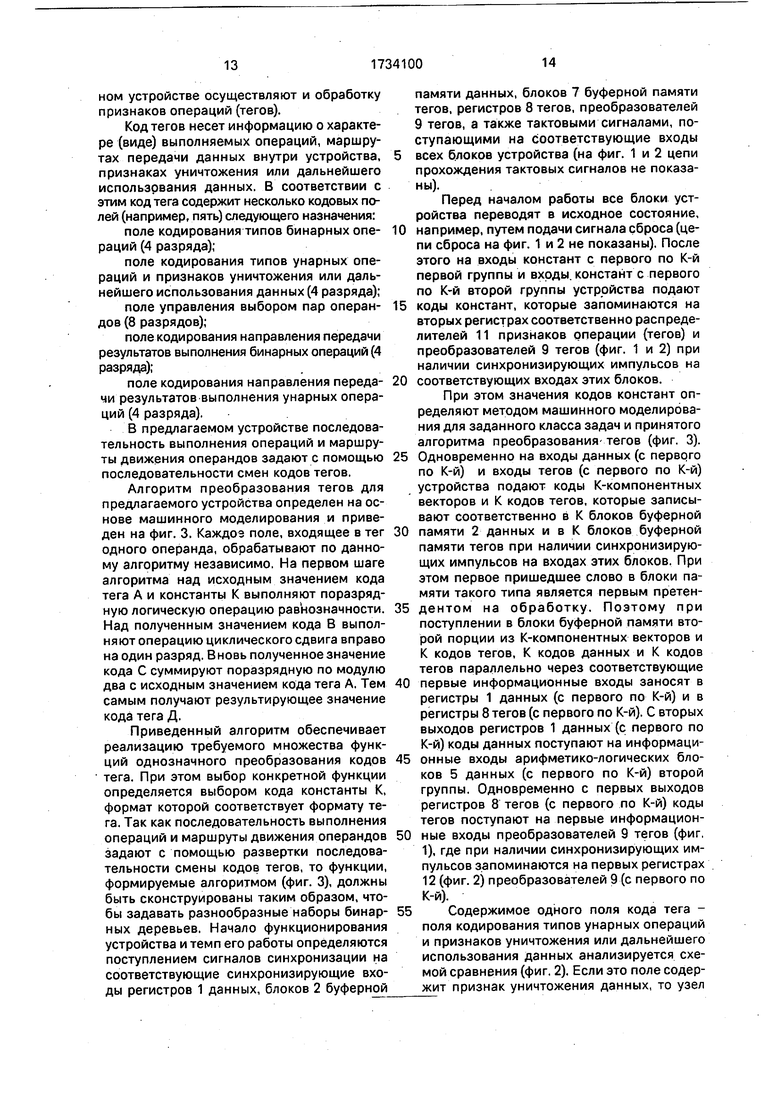

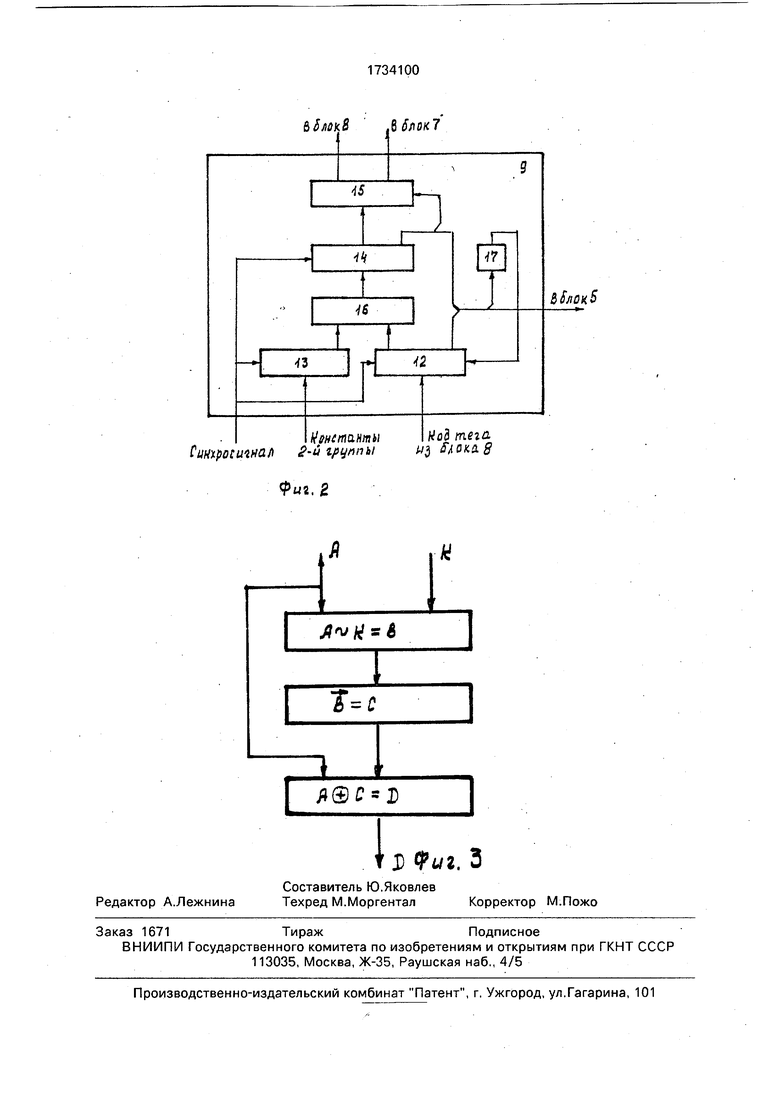

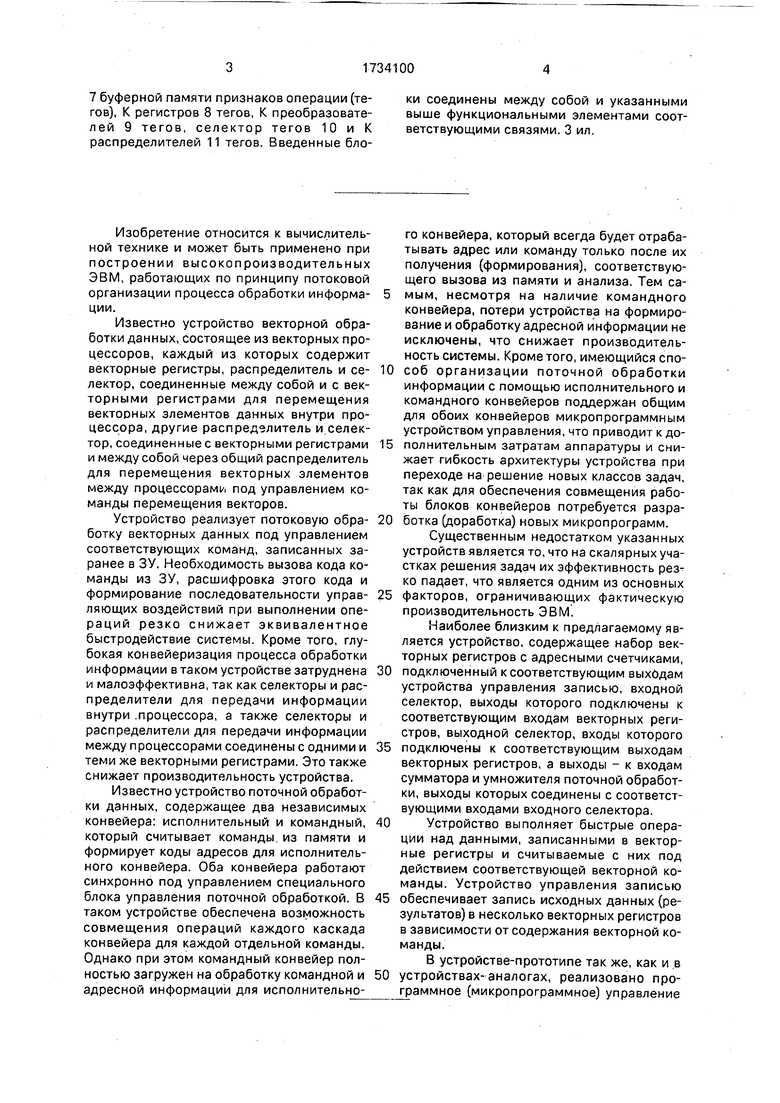

На фиг. 1 приведена схема предлагаемого устройства; на фиг, 2 - функциональная схема преобразователя признаков операции (тегов); на фиг 3 - алгоритм работы устройства.

Устройство содержит К регистров 1 данных, где К-число компонентов обрабатываемого вектора данных, К блоков 2 буферной памяти данных, селектор 3 данных и К арифметико-логических блоков 4 первой группы.

При этом с первого по К-й входы данных устройства подключены соответственно к первым информационным входам блоков 2 буферной памяти данных с первого по К-й,

выходы которых подключены к первым информационным входам регистров 1 данных с первого по К-й. Первые выходы регистров данных подключены соответственно к информационным входам селектора 3 данных,

0 выходы с первого по К-й первой группы которого подключены соответственно к первым информационным входам арифметико-логических блоков 4 с первого по К-й первой группы, выходы с первого по К-й второй группы

5 селектора 3 данных подключены соответственно к вторым информационным входам арифметико-логических блоков 4 с первого по К-й первой группы. Вход синхронизации устройства подключен к входам записи/счи0 тывания блоков 2 буферной памяти данных и регистров 1 данных. Устройство также содержит К арифметико-логических блоков 5 второй группы, К коммутаторов б, К блоков буферной памяти 7 признаков операции (те5 гов), К регистров 8 признаков операции (тегов), К преобразователей 9 признаков операции (тегов), селектор 10 признаков операции и К распределителей 11 признаков операции (тегов). Вторые выходы реги0 строе 1 данных с первого по К-й подключены соответственно к информационным входам арифметико-логических блоков 5 с первого по К-й второй группы, первые выходы которых подключены соответственно к вторым

5 информационным входам регистров 1 данных с первого по К-й. Вторые выходы арифметико-логических блоков 5 с первого по К-й второй группы подключены соответственно к вторым информационным входам блоков

0 2 буферной памяти данных с первого по К-й. Выходы арифметико-логических блоков 4 с первого по К-й первой группы подключены соответственно к информационным входам коммутаторов 6 с первого по К-й, первые вы5 ходы которых подключены соответственно к третьим информационным входам регистров 1 данных с первого по К-й. Вторые выходы коммутаторов б с первого по К-й подключены соответственно к третьим ин0 формационным входам блоков 2 буферной памяти данных с первого по К-й. Третьи выходы коммутаторов 6 с первого по К-й подключены соответственно к выходам результатов с первого по К-й устройства. С

5 первого по К-й входы признаков операции (тегов) устройства подключены соответственно к первым информационным входам блоков 7 буферной памяти признаков операции (тегов) с первого по К-й, выходы кото- рых подключены соответственно к первым

информационным входам регистров 8 признаков операции (тегов) с первого по К-й, перэые выходы которых подключены соответственно к первым информационным входам преобразователей 9 признаков операции (тегов) с первого по К-й, первые выходы которых подключены соответственно к вторым информационным входам регистров 8 признаков операции (тегов) с первого по К-й, вторые выходы которых подключены к информационным входам селектора 10 признаков операции (тегов). Выходы первой группы селектора 10 подключены соответственно к управляющим входам селектора 3 данных, выходы с первого по К-й второй группы селектора 10 признаков операции (тегов) подключены соответственно к первым информационным входам распределителей 11 признаков операции (тегов) с первого по К-й, первые выходы которых подключены соответственно к третьим информационным входам регистров 8 признаков операции (тегов) с первого по К-й. Вторые выходы распределителей 11 признаков операции (тегов) с первого по К-й подключены соответственно к вторым информационным входам блоков 7 буферной памяти признаков операции (тегов) с первого по К-й. Третьи выходы распределителей 11 признаков операции (тегов) с первого по К-й подключены соответственно к управляющим входам коммутаторов 6 с первого по К-й. Четвертые выходы распределителей 11 признаков операции (тегов) с первого по К-й подключены соответственно к входам кода операции арифметико-логических блоков 4 с первого по К-й первой группы. Пятые выходы распределителей 11 признаков операции (тегов) с первого по К-й подключены соответственно к выходам с первого по К-й признаков операции (тегов) устройства. Входы констант с первого по К-й первой группы устройства подключены соответственно к вторым информационным входам распределителей 11 признаков операции (тегов) с первого по К-й. Входы констант с первого по К-й второй группы устройства подключены соответственно к вторым информационным входам преобразователей 9 признаков операции (тегов) с первого по К-й, вторые выходы которых подключены соответственно к третьим информационным входам блоков 7 буферной памяти признаков операций (тегов) с первого по К-й. Третьи выходы преобразователей 9 признаков операции (тегов) с первого по К-й подключены соответственно к входам кода операции арифметико-логических блоков 5 с первого по К-й второй группы, Вход синхронизации устройства подключен к входам

записи/считывания блоков буферной памяти признаков операции (тегов), к входам записи/считывания регистров 8 признаков операции (тегов) и к входам синхронизации

преобразователей 9 признаков операции (тегов).

Таким образом, векторно-потоковое операционное устройство условно разделено на два канала: канал обработки данных

0 (блоки 1 - 6) и канал обработки тегов и управления (блоки 7-11).

Каждая компонента, входящая в состав устройства, может быть реализована с применением современной элементной базы и

5 интегральной технологии. Так, каждый регистр 1 данных и каждый регистр 8 признаков операции (тегов) (фиг. 1), предназначенные для хранения кодов данных, представленных в виде векторов или скалярных величин, и

0 соответственно признаков операции (тегов) могут быть реализованы любым из известных классических способов на базе триггер- ных схем с применением входной логики занесения кода с трех направлений и выход5 ной логики выдачи информации на два направления при наличии синхронизирующих сигналов, поступающих на соответствующие входы синхронизации этих регистров. Каждый блок 2 буферной памяти данных

0 и каждый блок 7 буферной памяти признаков операции (тегов) могут быть реализованы в виде регистровой памяти небольшой емкости (на несколько десятков слов) с дисциплиной обслуживания Первым пришел 5 первым обслужен. Реализация регистровой памяти такого типа не представляет затруднений.

Селектор 3 данных предназначен для отбора в каждый момент времени пар опе0 рандов, поступающих с регистров 1 данных, и выдачи отобранных пар на соответствующие информационые входы арифметико-логических блоков 4 первой группы. Селектор 3 данных может быть реализован в виде

5 ортогональной матрицы, содержащей вертикальные и горизонтальные кодовые шины данных, соединенные между собой коммутирующими элементами (ключами) по принципу каждый с каждым. Эти ключи

0 управляются сигналами коммутации, поступающими с выходов селектора 10 признаков операции (тегов).

Каждый арифметико-логический блок 4 первой группы может быть выполнен по

5 классической арифметико-логической схеме, реализующей требуемый набор операций. При этом в качестве кода операций используют соответствующие разряды кода тегов, которые выделяются распределителями 11 признаков операции (тегов) и поступают на входы кодов операций арифметико- логических блоков 4.

Каждый арифметико-логический блок 5 второй группы предназначен для выполнения унарных операций над данными (например, сдвиг, инверсия и т.д.).

Блок 5 может быть выполнен в виде классического арифметико-логического блока, реализующего усеченный набор операций и имеющего выходные логические схемы на два направления. Тип реализуемой операции и выбор направления выдачи результата с блока 5 определяет код, поступающий на управляющие входы блока 5 с соответствующих выходов преобразователей 9 признаков операций (тегов).

Преобразователи 9 признаков операции (тегов) предназначены для анализа и модификации тегов и принятия решения о дальнейшем использовании соответствующих данных (уничтожить, изменить значение, сохранить неизменным, переслать в регистр и т.д.). Тип функций, реализуемых преобразователем 9, определяется константой, поступающей на соответствующие входы констант этого преобразователя.

Преобразователь 9 признаков операции (тегов) содержит (фиг. 2) первый регистр

12исходного значения кода тега, второй регистр 13 констант, третий регистр 14 результирующего значения тега, коммутатор 15, узел 16 равнозначности и узел 17 сравнения со значением признака уничтожения данных. При этом первый и второй информационные входы преобразователя 9 признаков операции (тегов) подключены соответственно к информационным входам первого 12 и второго 13 регистров. Первый выход первого регистра 12 и выход второго регистра 13 подключены соответственно к первому и второму входам узла 16 разно- значности, выход которого подключен к информационному входу третьего регистра 14, первый и второй выходы которого подключены соответственно к информационному и управляющему входам коммутатора 15, первый и второй выходы которого подключены соответственно к первому и второму выходам преобразователя признаков операции (тегов). Второй выход первого регистра 12 подключен к входу узла 17 сравнения с признаком уничтожения данных, а также соединен с вторым выходом третьего регистра 14 и подключен к третьему выходу преобразователя 9 признаков операции (тегов), вход синхронизации которого подключен к входам записи/считывания первого 12, второго

13и третьего 14 регистров. Выход узла 17 сравнения с признаком уничтожения данных подключен к входу установки в ноль первого регистра 12.

Таким образом, преобразователь 9 признаков операции представляет собой (с точки зрения его технической реализации) простую схему, содержащую классические регистры с входами синхронизации, подключенные к логическим схемам, функционирование которых может быть описано

системой булевых выражений.

Селектор 10 признаков операции (тегов) представляет собой коммутатор, содержащий горизонтальные и вертикальные кодовые шины тегов, на каждом пересечении

которых реализована логическая схема, фиксирующая совпадение определенных разрядов кодов тегов двух операндов. При совпадении этих разрядов кодов пары тегов селектор 10 вырабатывает на соответствующих выходах сигналы коммутации. Эти сигналы, поступая на управляющие входы селектора 3 данных, открывают соответствующие ключи, пропуская на входы арифметико-логического блока 4 первой группы

выбранную пару операндов, которым принадлежат совпадающие теги. Техническая реализация селектора такого типа не вызывает затруднений.

Распределитель 11 признаков операции (тегов) предназначен для анализа и преобразования тегов, выбора направления передачи тегов, а также для выбора направления передачи результирующих данных. При этом вид преобразований тегов определяется кодом константы, поступающей на входы констант второй группы устройства. Распределитель 11 признаков операции тегов по виду функциональной схемы и технической реализацией во многом совпадает с функциональной схемой и технической реализацией преобразователя 9 тегов. Он также содержит три регистра, коммутатор и узел равнозначности, соединенные соответствующими связями. При этом узел 17

сравнения (фиг. 2) в распределителе 11 отсутствует, а узел 16 равнозначности выполняет те же функции, что и в преобразователе 9.

Векторно потоковое операционное устройство работает следующим образом.

В устройстве принят потоковый принцип организации процесса обработки информации, т.е. по готовности данных. При этом слова, с которыми оперирует устройство, содержат две части: данные и признаки операций (тегов). Эти две части связаны неразрывно, существуют и перемещаются только совместно как одно слово. Параллельно с обработкой данных в операционном устройстве осуществляют и обработку признаков операций (тегов).

Код тегов несет информацию о характере (виде) выполняемых операций, маршрутах передачи данных внутри устройства, признаках уничтожения или дальнейшего использрвания данных. В соответствии с этим код тега содержит несколько кодовых полей (например, пять) следующего назначения:

поле кодирования типов бинарных операций (4 разряда);

поле кодирования типов унарных операций и признаков уничтожения или дальнейшего использования данных (4 разряда);

поле управления выбором пар операндов (8 разрядов);

поле кодирования направления передачи результатов выполнения бинарных операций (4 разряда);

поле кодирования направления передачи результатов выполнения унарных операций (4 разряда).

В предлагаемом устройстве последовательность выполнения операций и маршруты движения операндов задают с помощью последовательности смен кодов тегов.

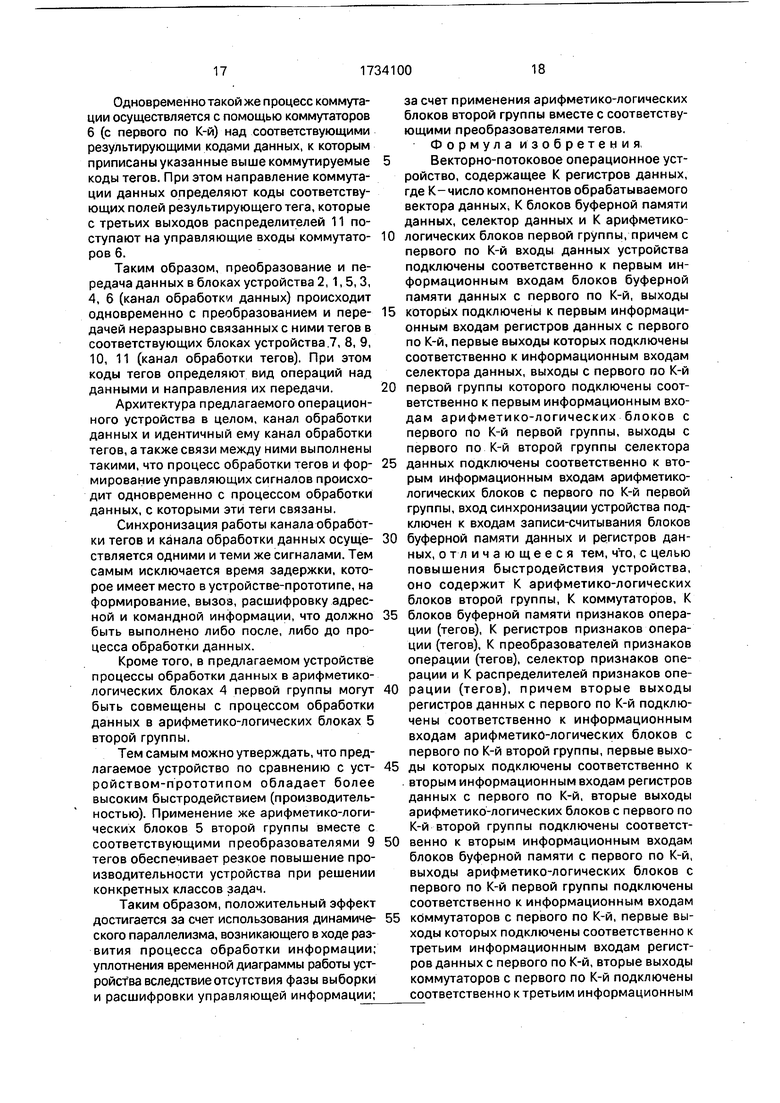

Алгоритм преобразования тегов для предлагаемого устройства определен на основе машинного моделирования и приведен на фиг. 3. Каждоз поле, входящее в тег одного операнда, обрабатывают по данному алгоритму независимо. На первом шаге алгоритма над исходным значением кода тега А и константы К выполняют поразрядную логическую операцию рав нозначности. Над полученным значением кода В выполняют операцию циклического сдвига вправо на один разряд. Вновь полученное значение кода С суммируют поразрядную по модулю два с исходным значением кода тега А. Тем самым получают результирующее значение кода тега Д.

Приведенный алгоритм обеспечивает реализацию требуемого множества функций однозначного преобразования кодов тега. При этом выбор конкретной функции определяется выбором кода константы К, формат которой соответствует формату тега. Так как последовательность выполнения операций и маршруты движения операндов задают с помощью развертки последовательности смены кодов тегов, то функции, формируемые алгоритмом (фиг. 3), должны быть сконструированы таким образом, чтобы задавать разнообразные наборы бинарных деревьев. Начало функционирования устройства и темп его работы определяются поступлением сигналов синхронизации на соответствующие синхронизирующие входы регистров 1 данных, блоков 2 буферной

памяти данных, блоков 7 буферной памяти тегов, регистров 8 тегов, преобразователей 9 тегов, а также тактовыми сигналами, поступающими на соответствующие входы

всех блоков устройства (на фиг. 1 и 2 цепи прохождения тактовых сигналов не показаны).

Перед началом работы все блоки устройства переводят в исходное состояние,

0 например, путем подачи сигнала сброса (цепи сброса на фиг. 1 и 2 не показаны). После этого на входы констант с первого по К-й первой группы и входы, констант с первого по К-й второй группы устройства подают

5 коды констант, которые запоминаются на вторых регистрах соответственно распределителей 11 признаков операции (тегов) и преобразователей 9 тегов (фиг. 1 и 2) при наличии синхронизирующих импульсов на

0 соответствующих входах этих блоков.

При этом значения кодов констант определяют методом машинного моделирования для заданного класса задач и принятого алгоритма преобразования- тегов (фиг. 3).

5 Одновременно на входы данных (с первого по К-й) и входы тегов (с первого по К-й) устройства подают коды К-компонентных векторов и К кодов тегов, которые записывают соответственно в К блоков буферной

0 памяти 2 данных и в К блоков буферной памяти тегов при наличии синхронизирующих импульсов на входах этих блоков. При этом первое пришедшее слово в блоки памяти такого типа является первым претен5 дентом на обработку. Поэтому при поступлении в блоки буферной памяти второй порции из К-компонентных векторов и К кодов тегов, К кодов данных и К кодов тегов параллельно через соответствующие

0 первые информационные входы заносят в регистры 1 данных (с первого по К-й) и в регистры 8 тегов (с первого по К-й). С вторых выходов регистров 1 данных (с первого по К-й) коды данных поступают на информаци5 онные входы арифметико-логических блоков 5 данных (с первого по К-й) второй группы. Одновременно с первых выходов регистров 8 тегов (с первого по К-й) коды тегов поступают на первые информацион0 ные входы преобразователей 9 тегов (фиг, 1), где при наличии синхронизирующих импульсов запоминаются на первых регистрах 12 (фиг. 2) преобразователей 9 (с первого по К-й).

5 Содержимое одного поля кода тега - поля кодирования типов унарных операций и признаков уничтожения или дальнейшего использования данных анализируется схемой сравнения (фиг. 2). Если это поле содержит признак уничтожения данных, то узел

17 сравнения вырабатывает на выходе сигнал, который, поступая на соответствующий вход регистра 12, устанавливает его в ноль. В этом случае узел 16 равнозначности не работает, а на первом и втором выходах блока 9 преобразователя тегов коды тегов отсутствуют (фиг. 2).,Таким образом, если уничтожаются данные, то уничтожаются и сопровождающие их теги. В случае повторного использования операнда или выполнения над операндом унарной операции узел 16 равнозначности формирует в соответствии с алгоритмом преобразования тега (фиг. 3) результирующий код тега, который поступает на третий регистр 14. При этом содержимое поля кодирования направления передачи результирующего тега поступаете соответствующих выходов этого регистра на управляющие входы коммутатора 15 (фиг. 2), а содержимое поля кодирования передачи результатов унарной операции - с других выходов этого регистра через третий выход блока 9 (фиг. 2) па соответствующие входы арифметико-логических блоков 5 второй группы (фиг. 1). В соответствии со значениями этих кодов результат унарной операции (код данных) и сопровождающий его тег (код тега) одновременно поступают либо на входы соответствующих регистров ) и 8 либо на входы соответствующих блоков буферной памяти 2 и 7 (фиг. 1) для последующих использований. Указанные логические операции и передачи внутри блоков преобразователей 9 тегов (с первого по К-й) выполняются в промежуток времени между двумя тактирующими импульсами.

Одновременно с этими преобразованиями и с выполнением унарных операций с вторых выходов регистров 8 тегов (с первого по К-й) на соответствующие входы селектора 10 тегов (фиг. 1) поступают коды тегов, которые, проходя через селектор 19 тегов без преобразований, поступают на соответствующие входы распределителей 11 тегов. Аналогично с первых выходов регистров да iHbix 1 (с первого по К-й) на соответствующие информационные входы селектора 3 данных поступают коды данных.

Селектор О тегов выделяет с помощью маскирования определенных разрядов тега поле управления выбором пар операндов и осуществляет его анализ.

В случае попарного совпадения кодов этих полей селектор 10 тегов вырабатывает сигналы совпадения, которые, поступая на соответствующие управляющие входы селектора 3 данных, коммутируют на входы арифметико-логических блоков 4 первой группы только те пары кодов данных, выбранные разряды тегов которых совпадают при сравнении.

Арифметико-логические блоки 4 первой группы (с первого по К-й) выполняют операции над выделенными селектором данных К-компонентными векторами, либо над выделенными К парами скалярных данных. При этом типы операций, которые реализуют арифметико-логические блоки 4 первой

группы, определяют распределители 11 признаков операций (тегов), которые работают аналогично преобразователям 9 тегов за исключением следующих особенностей. Так как селектор 10 тегов выделяет пары

кодов данных с одинаковыми значениями соответствующих полей тегов, то распределитель 11 тегов принимает с соответствующих выходов селектора коды одного тега из двух, причем каждое поле (из пяти указанных выше) кода тега подвергается преобразованию в соответствии с приведенным выше алгоритмом (фиг. 3). Так, в результате преобразования поля кодирования бинарных операций распределитель 11 тегов вырабатывает сигнал кодов бинарных операций, которые с четвертых выходов этих распределителей поступают на соответствующие входы арифметико-логических блоков 4 для реализации заданных операций над выбранными с помощью селектора 3 операндами. Одновременно преобразуются и другие поля кода тега и тем самым формируется результирующий код тега, который с пятых выходов распределителей 11

тегов поступают на соответствующие выходы тегов устройства одновременно с результирующим кодом данных, к которому этот код тега приписан. Причем код данных (как результат выполнения заданной бинарной

операции в арифметико-логическом блоке 4 первой группы) поступает на соответствующие выходы устройства с третьих выходов коммутаторов 6 (с первого по К-й) при наличии на соответствующих входах этих коммутаторов управляющих сигналов. Управляющие сигналы вырабатывает распределитель 11 в результате анализа соответствующего поля полученного кода тега - поля кодирования направления передачи

результатов выполнения бинарных операций. Анализ других полей результирующего тега определяет направление передачи полноформатного тега: либо с первых выходов распределителя 11 тегов (с первого по К-й)

на третьи входы регистров 8 тегов (с первого по К-й), либо с вторых выходов этих же распределителей 11 тегов на вторые входы блоков 7 буферной памяти тегов для последующего использования.

Одновременно такой же процесс коммутации осуществляется с помощью коммутаторов 6 (с первого по К-й) над соответствующими результирующими кодами данных, к которым приписаны указанные выше коммутируемые коды тегов. При этом направление коммутации данных определяют коды соответствующих полей результирующего тега, которые с третьих выходов распределителей 11 поступают на управляющие входы коммутаторов 6.

Таким образом, преобразование и передача данных в блоках устройства 2,1, 5,3, 4, 6 (канал обработки данных) происходит одновременно с преобразованием и передачей неразрывно связанных с ними тегов в соответствующих блоках устройства .7, 8, 9, 10, 11 (канал обработки тегов). При этом коды тегов определяют вид операций над данными и направления их передачи.

Архитектура предлагаемого операционного устройства в целом, канал обработки данных и идентичный ему канал обработки тегов, а также связи между ними выполнены такими, что процесс обработки тегов и формирование управляющих сигналов происходит одновременно с процессом обработки данных, с которыми эти теги связаны.

Синхронизация работы канала обработки тегов и канала обработки данных осуществляется одними и теми же сигналами. Тем самым исключается время задержки, которое имеет место в устройстве-прототипе, на формирование, вызоз, расшифровку адресной и командной информации, что должно быть выполнено либо после, либо до процесса обработки данных.

Кроме того, в предлагаемом устройстве процессы обработки данных в арифметико- логических блоках 4 первой группы могут быть совмещены с процессом обработки данных в арифметико-логических блоках 5 второй группы.

Тем самым можно утверждать, что предлагаемое устройство по сравнению с устройством-прототипом обладает более высоким быстродействием (производительностью). Применение же арифметико-логических блоков 5 второй группы вместе с соответствующими преобразователями 9 тегов обеспечивает резкое повышение производительности устройства при решении конкретных классов задач.

Таким образом, положительный эффект достигается за счет использования динамического параллелизма, возникающего в ходе развития процесса обработки информации; уплотнения временной диаграммы работы устройства вследствие отсутствия фазы выборки и расшифровки управляющей информации;

за счет применения арифметико-логических блоков второй группы вместе с соответствующими преобразователями тегов. Формула изобретения

Векторно-потоковое операционное устройство, содержащее К регистров данных, где К- число компонентов обрабатываемого вектора данных, К блоков буферной памяти данных, селектор данных и К арифметико0 логических блоков первой группы, причем с первого по К-й входы данных устройства подключены соответственно к первым информационным входам блоков буферной памяти данных с первого по К-й, выходы

5 которых подключены к первым информационным входам регистров данных с первого по К-й, первые выходы которых подключены соответственно к информационным входам селектора данных, выходы с первого по К-й

0 первой группы которого подключены соответственно к первым информационным входам арифметико-логических блоков с первого по К-й первой группы, выходы с первого по К-й второй группы селектора

5 данных подключены соответственно к вторым информационным входам арифметико- логических блоков с первого по К-й первой группы, вход синхронизации устройства подключен к входам записи-считывания блоков

0 буферной памяти данных и регистров данных, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит К арифметико-логических блоков второй группы, К коммутаторов, К

5 блоков буферной памяти признаков операции (тегов), К регистров признаков операции (тегов), К преобразователей признаков операции (тегов), селектор признаков операции и К распределителей признаков опе0 рации (тегов), причем вторые выходы регистров данных с первого по К-й подключены соответственно к информационным входам арифметико-логических блоков с первого по К-й второй группы, первые выхо5 ды которых подключены соответственно к вторым информационным входам регистров данных с первого по К-й, вторые выходы арифметико-логических блоков с первого по К-й второй группы подключены соответст0 венно к вторым информационным входам блоков буферной памяти с первого по К-й, выходы арифметико-логических блоков с первого по К-й первой группы подключены соответственно к информационным входам

5 коммутаторов с первого по К-й, первые выходы которых подключены соответственно к третьим информационным входам регистров данных с первого по К-й, вторые выходы коммутаторов с первого по К-й подключены соответственно к третьим информационным

входам блоков буферной памяти данных с первого по К-й, третьи выходы коммутаторов с первого по К-й подключены соответственно к выходам результатов с первого по К-й устройства, с первого по К-й входы признаков операции (тегов) устройства подключены соответственно к первым информационным входам блоков буферной памяти признаков операции (тегов) с первого по К-й, выходы которых подключены соответственно к первым информационным входам регистров признаков операции (тегов) с первого по К-й, первые выходы которых подключены соответственно к первым информационным входам преобразователей признаков операции (тегов) с первого по К-й, первые выходы которых подключены соответственно к вторым информационным входам регистров признаков операции (тегов) с первого по К-й, вторые выходы которых подключены к информационным входам селектора признаков операции (тегов), выходы первой группы которого подключены соответственно к управляющим входам селектора данных, выходы с первого по К-й второй группы селектора признаков операции (тегов) подключены соответственно к первым информационным входам распределителей признаков операции (тегов) с первого по К-й, первые выходы которых подключены соответственно к третьим информационным входам регистра признаков операции (тегов) с первого по К-й, вторые выходы распределителей признаков операции (тегов) с первого по К-й подключены соответственно к вторым информационным входам блоков буферной памяти признаков операции (тегов) с первого по К-й, третьи выходы распределителей признаков операции (тегов) с первого по К-й подключены соответственно к управляющим входам коммутаторов с первого по К-й, четвертые выходы распределителей признаков операции (тегов) с первого по К-й подключены соответственно к входам кода операции арифметико-логических блоков с первого по К-й первой группы, пятые выходы распределителей признаков операции (тегов) с первого по К-й подключены соответственно к выходам с первого по К-й признаков операций (те го в) устройства, входы константе первого по К-й первой группы которого подключены соответственно к вторым информационным входам распределителей признаков операции (тегов) с первого по К-й, входы констант с первого по К-й второй группы устройства подключены соответственно к вторым информационным входам преобразователей признаков операции (тегов) с первого по К-й, вторые выходы которых подключены соответственно к третьим информационным входам блоков буферной памяти признаков операции (тегов) с первого по К-й, третьи выходы преобразователей признаков операции (тегов) с первого по К-й подключены соответственно к входам кода операции арифметико-логических блоков с первого по К-й второй группы, вход синхронизации устройства подключен к входам записи-считывания блоков буферной памяти признаков операции (тегов), к входам записи-считывания регистров признаков операции (тегов) и к входам синхронизации преобразователей признаков операции (тегов), причем каждый преобразователь признаков операции (тегов) содержит три регистра, коммутатор, узел равнозначности и узел сравнения со значением признака уничтожения данных, при этом в каждом преобразователе признаков операции (тегов) первый и второй информационные входы преобразователя признаков операции (тегов) подключены соответственно к информационным входам первого и второго регистров, первый выход первого регистра и выход второго регистра подключены соответственно к первому и второму входам узла равнозначности, выход которого подключен к информационному входу третьего регистра, первый и второй выходы которого подключены соответственно к информационному и уп- равляющему входам коммутатора, первый и второй выходы которого подключены соответственно к первому и второму выходам преобразователя признаков операции (тегов), второй выход первого регистра подключен к входу узла сравнения с признаком уничтожения данных, соединен с вторым выходом третьего регистра и подключен к третьему выходу преобразователя признаков операции (тегов), вход синхронизации которого подключен к входам записи-считывания первого, второго и третьего регистров, выход узла сравнения с признаком уничтожения данных подключен к входу установки в О первого регистра.

Фыг. 2

i

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| Термопарный сигнализатор о пожаре | 1960 |

|

SU137422A1 |

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

Авторы

Даты

1992-05-15—Публикация

1989-10-26—Подача