гистра предсказания, причем i-ый выход регистра исходного кода и (1-1)-й выход регистра предсказания подключены к парафазны.м входам (i - 1)-го разряда логического блока эквивалентности, а каждый выход блока совпадения подключен к соответствующим счетным входам регистра исходного кода и регистра предсказания.

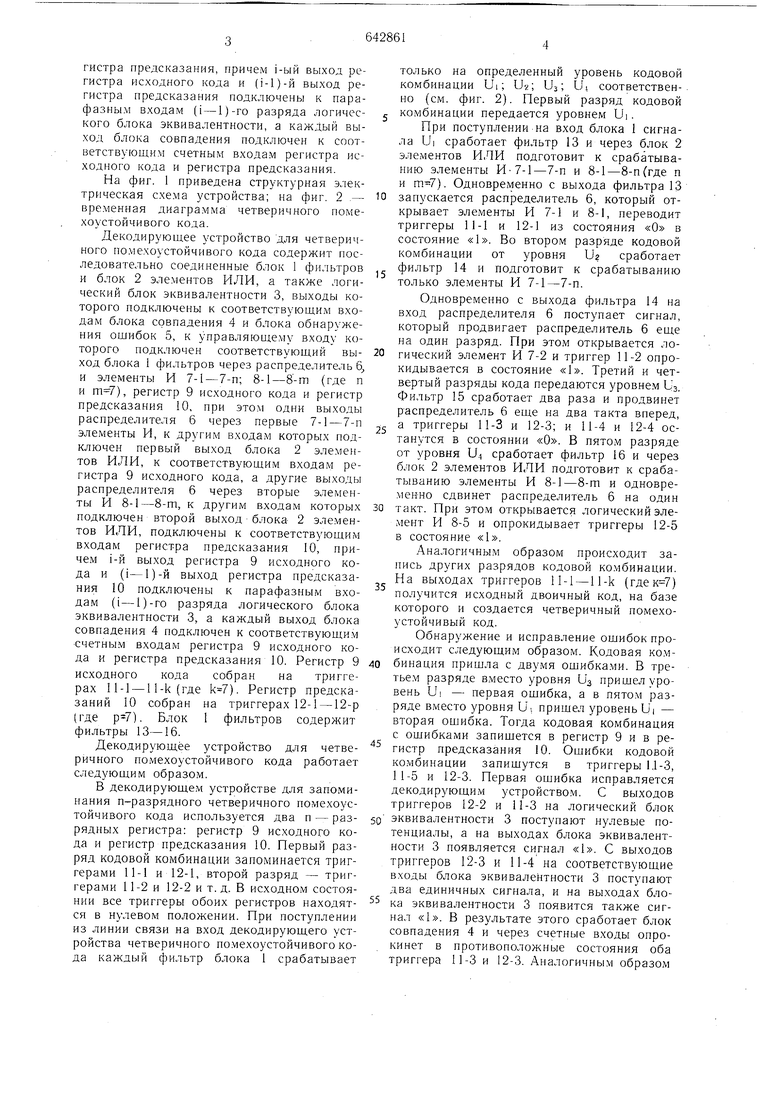

На фиг. 1 приведена структурная электрическая схе.ма устройства; на фиг. 2 ,- вре.менная диаграмма четверичного помехоустойчивого кода.

Декодирующее устройство для четверичного по.мехоустойчивого кода содержит последовательно соединенные блок 1 фильтров и блок 2 элементов ИЛИ, а также логический блок эквивалентности 3, выходы которого подключены к соответствующим входам блока совпадения 4 и блока обнарул ения ошибок 5, к управляюп ему входу которого подключен соответствующий выход блока 1 фильтров через распределитель 6 и элементы И 7-1-7-п; 8-1-8-гп (где п и ), регистр 9 исходного кода и регистр предсказания 10, при этом одни выходы распределителя 6 через первые 7-1-7-п элементы И, к другим входам которых подключен первый выход блока 2 элементов ИЛИ, к соответствующим входам регистра 9 исходного кода, а другие выходы распределителя 6 через вторые элементы И 8-1-8-ш, к другим входам которых подключен второй выход блока 2 элементов ИЛИ, подключены к соответствующим входам регистра предсказания 10, причем i-й выход регистра 9 исходного кода и (i-1)-и выход регистра предсказания 10 подключены к парафазны.м входам (i-1)-го разряда логического блока эквивалентности 3, а каждый выход блока совпадения 4 подключен к соответствующим счетным входам регистра 9 исходного кода и регистра предсказания 10. Регистр 9 исходного кода собран на триггерах 11-1 - 11-К(где ). Регистр предсказаний 10 собран на триггерах 12-1 - 12-р (где ). Блок 1 фильтров содержит фильтры 13-16.

Декодирующее устройство для четверичного помехоустойчивого кода работает следующим образом.

В декодирующем устройстве для запоминания п-разрядного четверичного помехоустойчивого кода используется два п - разрядных регистра: регистр 9 исходного кода и регистр предсказания 10. Первый разряд кодовой комбинации запоминается триггерами 11-1 и 12-1, второй разряд - триггерами 11-2 и 12-2 и т.д. В исходном состоянии все триггеры обоих регистров находятся в нулевом положении. При поступлении из линии связи на вход декодирующего устройства четверичного помехоустойчивого кода каждый фильтр блока 1 срабатывает

ТОЛЬКО на определенный уровень кодовой комбинации Ui; Ux; Us; Ui соответствен-, но (с.м. фиг. 2). Первый разряд кодовой J ко.мбинации передается уровнем Ui.

При поступлении на вход блока 1 сигнала Ui сработает фильтр 13 и через блок 2 элементов ИЛИ подготовит к срабатыванию элементы И-7-1-7-п и 8-1-8-п(где п и ). Одновре.менно с выхода фильтра 13 запускается распределитель 6, который открывает элементы И 7-1 и 8-1, переводит триггеры 11-1 и 12-1 из состояния «О в состояние «1. Во втором разряде кодовой комбинации от уровня U сработает фильтр 14 и подготовит к срабатыванию только элементы И 7-1-7-п.

Одновременно с выхода фильтра 14 на вход распределителя 6 поступает сигнал, который продвигает распределитель 6 еще на один разряд. При это.м открывается логический элемент И 7-2 и триггер 11-2 опрокидывается в состояние «1. Третий и четвертый разряды кода передаются уровнем Us. Фильтр 15 сработает два раза и продвинет распределитель 6 еще на два такта вперед, 5 а триггеры 11-3 и 12-3; и 11-4 и 12-4 останутся в состоянии «О. В пятом разряде от уровня U4 сработает фильтр 16 и через блок 2 элементов ИЛИ подготовит к срабатыванию элементы И 8-1-8-т и одновременно сдвинет распределитель 6 на один 0 такт. При этом открывается логический элемент И 8-5 и опрокидывает триггеры 12-5 в состояние «1.

Аналогичным образом происходит запись других разрядов кодовой комбинации. На выходах триггеров 11-1 - 11-k () получится исходный двоичный код, на базе которого и создается четверичный помехоустойчивый код.

Обнаружение и исправление ощибок происходит следующим образом. Кодовая комбинация прищла с двумя ощибка.ми. В третьем разряде вместо уровня УЗ прищел уровень Ui - первая ощибка, а в пятом разряде вместо уровня Ui прищел уровень U| - вторая ощибка. Тогда кодовая комбинация с ощибками запишется в регистр 9 и в ре гистр предсказания 10. Ощибки кодовой комбинации запишутся в триггеры 1.1-3, 11-5 и 12-3. Первая ошибка исправляется декодирующи.м устройством. С выходов триггеров 12-2 и 11-3 на логический блок о эквивалентности 3 поступают нулевые потенциалы, а на выходах блока эквивалентности 3 появляется сигнал «1. С выходов триггеров 12-3 и 11-4 на соответствующие входы блока эквивалеЦтности 3 поступают два единичных сигнала, и на выходах блока эквивалентности 3 появится также сигнал «I. В результате этого сработает блок совпадения 4 и через счетные входы опрокинет в противоположные состояния оба триггера 11-3 и 12-3. Аналогичным образом

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1985 |

|

SU1349009A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Устройство для выделения экстремумов временных интервалов | 1979 |

|

SU864533A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

Авторы

Даты

1979-01-15—Публикация

1976-06-07—Подача