Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах помехоустойчивой передачи информации с трехкратным повторением.

Цель изобретения - повышение быстродействия устройства.

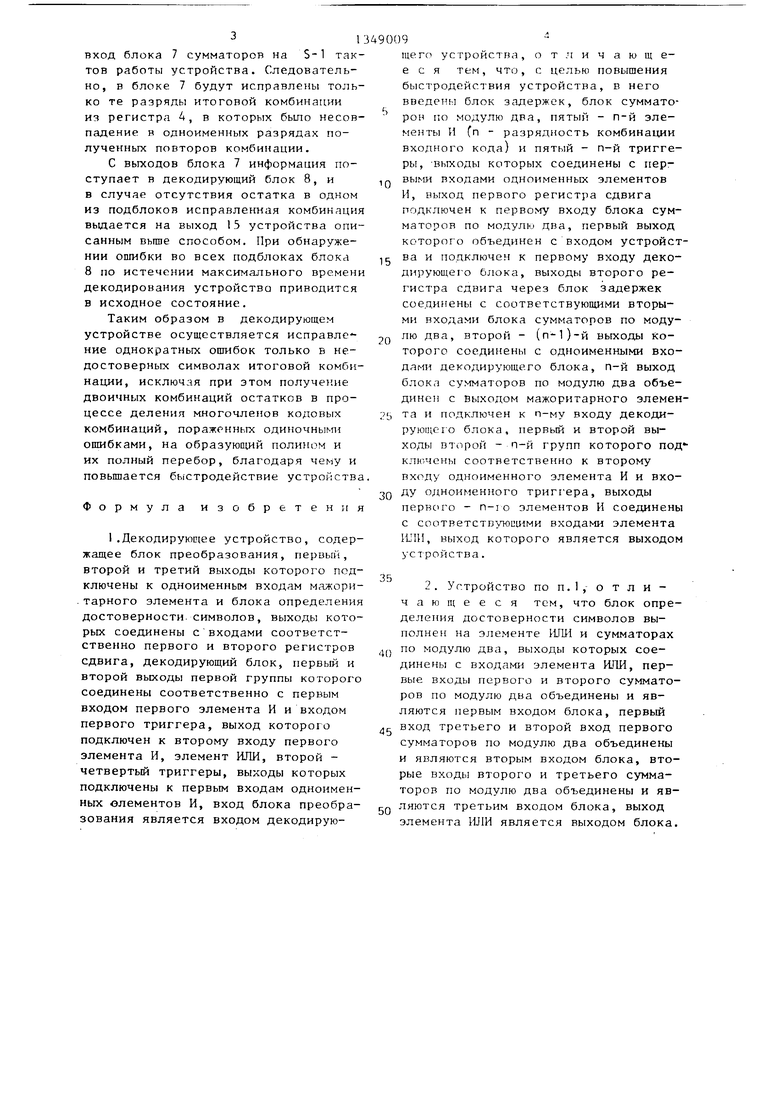

Блок-схема декодирующего устройства приведена на чертеже.

Декодирующее устройство содержит блок 1 преобразования, мажоритарный элемент 2, блок 3 определения достоверности символов, первый и второй

10

символов и в мажоритарный элемент 2. Кроме того, информация поступает и в декодирующий блок 8, где осуществляется проверка комбинации на соответствие циклическому коду. В случае, ког да хотя бы один из трех повторов комбинации окажется неискаженным, что свидетельствует об отсутствии ос.татка в схеме деления какого-либо 1-го подблока из блока 8, на соответствующий триггер 9.J выдается импульс, переводящий его в единичное состояние, обеспечивая тем

регистры 4,5 сдвига, блок 6 задержек, 15 самым прохождение информации из это- блок 7 сумматоров по модулю два, декодирующий блок 8, п триггеров 9 (п - разрядность комбинации входного кода), п элементов И 10 и элемент ИЛИ 11. Блок 3 состоит из трех сумматоров 12 по модулю два и элемента ИЛИ 13. На чертеже обозначены вход 14 и выход 15 устройства. Цепи синхронизации и начальной установки не показаны.

Блок 1 преобразования служит для записи каждого повтора принимаемой комбинации в свой регистр и последующего одновременного поэлементного вывода всех трех повторов на соответствующие выходы блока 1.

Блок 7 представляет собой п сумматоров по модулю два, первые входы которых объединены и являются первым входом блока 7, а вторые входы - вторыми входами этого блока.

Декодирующий блок В представляет собой совокупность однотипных независимых декодеров, построенных на основе регистра сдвига с обратными связями по схеме деления на образующий полином входного кода. Этот блок 8 служит для проверки комбинации на соответствие используемому циклическому коду.

Декодирующее устройство работает следующим образом.

Перед приемом информации триггеры 10.1-10.П и вся остальная память переводится в нулевое состояние. Информация, закодированная циклическим кодом в виде трех повторов п-эле- ментной кодовой комбинации, поступает с входа 14 устройства в блок 1 преобразования, осуществляющий выделение из кодовой посылки и запись каждого повтора в свой регистр с последующей их параллельной выдачей в блок 3 обнаружения достоверности

го подблока на выход 15 устройства посредством подготовленного триггером 9.1 соответствующего элемента И 10.1 и элемент ИЛИ 11. С прохожде20 нием последнего импульса выходной комбина1;ии устройство приводится в исходное состояние.

Если все повторы комбинации будут искажены, то одноименные разряды по25 вторяемс й комбинации (трех повторов) из блока. 1 преобразования поступают в мажоритарный элемент 2, который формирует из них символы итоговой комбина1,иИ по принципу больщинства

30 и в блор; 3 обнаружения достоверности СИМВОЛОЕ:, реализующий логическую функцию

,X,V Xj}J,Y Х,Х.

Итоговая комбинация с выхода эле25 мента 2 поступает в п-разрядный первый регистр 4 сдвига и на п-й вход блока 8., из которого в случае отсутствия оиибок выдается на выход 15 устройс ва аналогично рассмотрен40 ному. Одновременно с этим блок 3 обнаружения достоверности символов осуществляет выдачу на запись во второй регистр 5 сдвига информации в виде последовательности нулей и

45 единиц (комбинации несовпадений), причем единицы находятся только на трех позициях, где имело место хотя бы одно несовпадение в одноименных разрядах полученных повторов комбинации. Если в процессе обработки декодирующим блоком 8 итоговой комбинации обнаруживается ощибка, то информация из регистров 4,5 поступает в блок 7 сумматоров. Комбинации

55 несовпадений из регистра 5 поступает на входы блока 7 через блок 6 задержки, осуществляющий задержку в выдаче информации с S-ro выхода () регистра 5 на соответствуклций

50

символов и в мажоритарный элемент 2. Кроме того, информация поступает и в декодирующий блок 8, где осуществляется проверка комбинации на соответствие циклическому коду. В случае, ког да хотя бы один из трех повторов комбинации окажется неискаженным, что свидетельствует об отсутствии ос.татка в схеме деления какого-либо 1-го подблока из блока 8, на соответствующий триггер 9.J выдается импульс, переводящий его в единичное состояние, обеспечивая тем

самым прохождение информации из это-

го подблока на выход 15 устройства посредством подготовленного триггером 9.1 соответствующего элемента И 10.1 и элемент ИЛИ 11. С прохождением последнего импульса выходной комбина1;ии устройство приводится в исходное состояние.

Если все повторы комбинации будут искажены, то одноименные разряды повторяемс й комбинации (трех повторов) из блока. 1 преобразования поступают в мажоритарный элемент 2, который формирует из них символы итоговой комбина1,иИ по принципу больщинства

и в блор; 3 обнаружения достоверности СИМВОЛОЕ:, реализующий логическую функцию

,X,V Xj}J,Y Х,Х.

Итоговая комбинация с выхода элемента 2 поступает в п-разрядный первый регистр 4 сдвига и на п-й вход блока 8., из которого в случае отсутствия оиибок выдается на выход 15 устройс ва аналогично рассмотренному. Одновременно с этим блок 3 обнаружения достоверности символов осуществляет выдачу на запись во второй регистр 5 сдвига информации в виде последовательности нулей и

единиц (комбинации несовпадений), причем единицы находятся только на трех позициях, где имело место хотя бы одно несовпадение в одноименных разрядах полученных повторов комбинации. Если в процессе обработки декодирующим блоком 8 итоговой комбинации обнаруживается ощибка, то информация из регистров 4,5 поступает в блок 7 сумматоров. Комбинации

несовпадений из регистра 5 поступает на входы блока 7 через блок 6 задержки, осуществляющий задержку в выдаче информации с S-ro выхода () регистра 5 на соответствуклций

вход блока 7 сумматоров на S-1 тактов работы устройства. Следовательно, в блоке 7 будут исправлены только те разряды итоговой комбинации из регистра 4, в которых было несовпадение в одноименных разрядах полученных повторов комбинации.

С выходов блока 7 информация поступает в декодирующий блок 8, и в случае отсутствия остатка в одном из подблоков исправленная комбинация выдается на выход 15 устройства описанным выше способом. При обнаружении ошибки во всех подблоках блока 8 по истечении максимального времени декодирования устройство приводится в исходное состояние.

Таким образом в декодирующем устройстве осуществляется исправло-- ине однократньгх ошибок только в не- достоверньгх символах итоговой комбинации, исключая при этом получение двоичных комбинаций остатков в процессе деления многочленов кодовых комбинаций, пораженных одиночныьш ошибками, на образуюпрчй полином и их полный перебор, благодаря чему и повьш ается бы стродействие устройства

Формула изобретения

1 .Декодируюп1ее устройство, содержащее блок преобразования, первый, второй и третий выходы которого подключены к одноименным входам мажори- .тарного элемента и блока определения достоверности символов, выходы которых соединены с входами соответст- ственно первого и второго регистров сдвига, декодирующий блок, первый и второй выходы первой группы которого соединены соответственно с первым входом первого элемента И и входом первого триггера, выход которого подключен к второму входу первого элемента И, элемент ИЛИ, второй - четвертый триггеры, выходы которых подключены к первым входам одноименных олементов И, вход блока преобразования является входом декодирую

5

0

щегр устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок задержек, блок сумматоров по модулю два, пятый - п-й элементы И fn - разрядность комбинации входного кода) и пятый - п-й триггеры, -выходы которых соединены с первыми входами одноименных элементов И, выход первого регистра сдвига подключен к первому входу блока сумматоров по модулю два, первый выход которого объединен с входом устройства и подключен к первому входу декодирующего блока, выходы второго регистра сдвига через блок задержек соединены с соответствующими вторыми входами блока сумматоров по модулю два, второй - (п-1)-й выходы которого соединены с одноименными входами декодирующего блока, п-й выход блока сумматоров по модулю два объединен с Выходом мажоритарного элемента и подключен к п-му входу декодирующего блока, первый и второй выходы второй - п-й групп которого ключены соответственно к второму входу одноименного элемента И и входу одноименного триггера, выходы первс го - п-го элементов И соединены с соответствующими входами элемента , выход которого является выходом устройства.

2. Устройство по п., о т л и - чающееся тем, что блок определения достоверности символов выполнен на элементе HJUi и сумматорах по модулю два, выходы которых соединены с входами элемента ИЛИ, первые входы первого и второго сумматоров по модулю два объединены и являются первым входом блока, первый g вход третьего и второй вход первого сумматоров по модулю два объединены и являются вторым входом блока, вторые входы второго и третьего сумматоров по модулю два объединены и являются третьим входом блока, выход элемента ИЛИ является выходом блока.

0

5

0

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок | 1984 |

|

SU1243100A1 |

| Устройство приема многократно передаваемых комбинаций | 1979 |

|

SU866763A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для декодирования модулярного кода | 1987 |

|

SU1411980A1 |

| Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации | 1984 |

|

SU1246380A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ СИГНАЛА СТИРАНИЯ | 2001 |

|

RU2208907C2 |

| Устройство для обнаружения и исправления ошибок | 1989 |

|

SU1640814A1 |

| Устройство для мажоритарного декодирования кодов с повторением | 1978 |

|

SU767989A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах помехоустойчивой передачи информация с трехкратным повторением позволяет повысить быстродействие устройства. Декодирующее устройство содержит блок 1 преобразования, мажоритарный элемент 2, блок 3 определения достоверности символов, состоящий из с умма ikjpOB l2-12j по модулю два и Э ;емента ИЛИ 13, регистры 4,5, декодирующий блок 8,триггеры 9-9„,элементы И 10,-10п и элемент ИЛИ 11. Благодаря введению блока 6 задержки н блока 7 сумматоров по модулю два, а также п триггеров 9 и п элементов И 10 (п-разрядность входной комбинации) исправление однократных оши- Ьок производится без получения дво- ич;;ых комбинаций остатков от деления на образующий полином цикличееного кода н без полного перебора этих осггтков. I з.п. ф-лы, 1 ил. i (Л :о 4 СО со

| Касами Т | |||

| и др | |||

| Теория кодирования | |||

| М.: Мир,1978, с | |||

| Ситценабивная машина | 1922 |

|

SU391A1 |

| Устройство для обнаружения и исправления ошибок | 1984 |

|

SU1243100A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-10-30—Публикация

1985-11-04—Подача