1

Изобретение относится к вычислительной технике я может быть использовано в управл$оошнх 1зычислительных машинах для передаче данных между центральной памятью и перифери&хымн системами.

Известно устройство для передачи данных, содержащее запомвнаюшяй блок, связанный через буферншсй накопитель с периферийным блоком, блок управления, перШ11й выход которого подключен к управляющему входу буферного накопителя, а второй выход - через блок фор)- мнрования текущего адреса подкшочен к управляющему входу запоминающего блока, причем управляющий выход периферийного блока подключен к первому входу блока управления, к второму входу которого подключен другой выход блсжа формирования текущего адреса, к инф(ч мадионному входу которого и к третьему ВХОДУ блока управления подключен выход процессора .

Однако известное устройство не обеспечивает передачу данных без выцачи управл51ющих команд процессором.

Целью изобретения 5шляется устранение перерывов в передаче данных при возникновении отказов процессора.

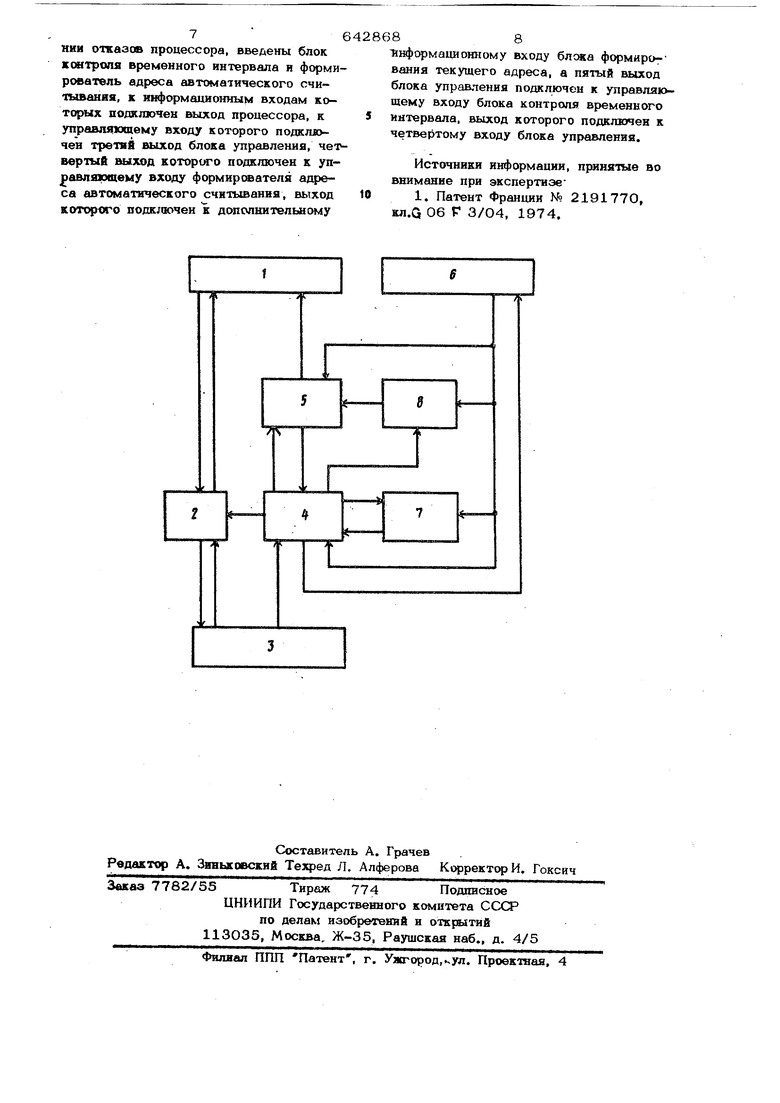

Для этого в устройство для передачи данных, содержащее запоминающий блок, связанный через буфершый накопитель с периферийным блоком блок управления, первый выход которого подключен к управляющему входу буферного накопителя, а второй выход - через блок формирования текущего адреса подключен к управляющему входу запоминающего блока, причем управляющий выход периферийного блока подключен к первому входу блока управления, к второму входу которого по подключен другой выход блока формирования текущего адреса, к информационному входу которого и к третьему входу бАока управления подключен выход процессора, введены блок контроля временного интервала и формирователь peca автоматического считывания, к информационным входам которых подключен выход процессора, к управляющему входу которого подключен третий выход блока управлення, четвертый выход которого подключен к управляюшему входу формирователя адреса автоматического вчйтъшания, выход которого подключен к дополнительному информационному вхо ду блшса формирования текущего адреса а пятый выход блока управления подключен к управляющему входу блока контроля временного интервала, выход которого подключен к четвертсл у входу блока управления. . В таком устройстве перерьшов в передаче данных при отказах процессора не наблюдается. На чертеже приведена структурная электрическая схема устройства. Устройство для передачи данных содержит запоминающий блок 1, связанны через буферный накопитель 2 с периферийным блоком 3, блок управления 4, первый Еялход которого подключен к управляющему входу буферного накопителя 2, а второй выхой - через блок формирования 5 текущего адреса подключен к управляющему входу запоминающего блока 1, причем управл5ооший выход периферийного блока 3 подшшчен к первому входу блока управления 4, к второму входу которого подключен другой выход блока формирования 5 текущего адреса, к информационному входу которого н к третьему входу блока управления 4JIOДключeн выход процессора 6, введенные блок контроля 7 временного интервала и формирователь 8 адреса автоматаческого считъшания, к информационным входам которых подклю чен выход процессора 6, к управляющему входу которого подключен третий вы ход блока управления 4, четвертый выход которого подключен к управляющем входу формирователя 8 адреса автоматического считывания, выход которого подключен к дополнительному информационному входу блока формирования 5 текущего адреса, а пятый выход блока управления 4 подключен к управляющему входу блока контроля 7 временного интв{тала, выход которого подключен к четвертому входу блока управления 4. Устройство для передачи данных работает следующим обраэ 1. Устройство для передачи даввых работает в двух режимах: в режиме пере8дачи данных по командам процессора и в режиме автоматического списывания. В режиме передачи данных работа начинается с посылки процессором 6 последовательности команд поочередно: -в блок управления 4 посылается информация о виде обмена и номера периферийного блока 3; - в блок формирования 5 записывается адрес зоны запоминающего блока 1, выделенной для передачи или приема данных;. -в блок контроля 7 записывается контрольный интервал времени; -в формирователь 8 адреса вводятся данные о начальном адресе и размере массива, подлежащего выводу в периферийное устройство 3 в автоматическом режиме. После получения информации о виде обмена блок управления 4 посылает признак обращения к запомщ1ающему блоку 1 в процессор бив блок формирования 5. Блок формирования 5 вырабатьтает и посылает в запоминающий блок 1 сигналы обращения и код адреса. Между буферным накопителем 2 и запоминающим блоком 1 происходит пе редача данных, после чего блок управления 4 снимает признак обращения к запоминающему блоку 1, К этому моменту буферный накопитель 2 содержит данные для передачи в периферийный блок 3, В зависимости от вида обмена, заданного блоку управления 4, передача в периферийный блок 3 и списывание данных из него пр(жсходит по сигналу запроса, поступающему из периферийного блока 3 или по сигналу, формируемому блоком управления 4. Блок управления 4 посылает в буферный накопитель 2 команду, по которой происходит обмен между буферным накопителем 2 н периферийньлм блоком 3. Затем блок управления 4 посылает в процессор бив блок формирования 5 признак обращения к запоминающему блоку 1, по которому текущий адрес изменяется на единицу и вырабатываются сигналы обращения в код адреса, т.е производится очередной цикл обмена аналогично описанному вьпие. После окончания последнего цикла передачи заданной зоны блок формирования 5 посылает в блок управления 4 признак последнего слова массива, по которому блок управления 4 прекращает .формировать призвакн обращения к запо 5 минаюшему блоку 1 и посылать команды в буферный накопитель 2. Устройство для передачи данных пер ходит в состояние ожидания следующей посьшки последсжательности команд из процессора 6, после получения которой режим обмена повторяется. Для разрешения конфликтной ситуации одновременного обращения к запоминающему блоку 1 и к процессору 6, прсщес сор 6, после получения из блока управления 4 признака обращения к запомина щему блоку 1 блокирует собственное об щение к запоминающему блоку 1. Для этого в процессоре 6 может, например, приостанавливаться на время обрашення формирование последовательности синхроимпульсов или же задерживаться вы полнение микрооперации обращения к за поминающему блоку 1, если признак об ращения устройства для передачи данны совпадает с данной микрооперацией. Одновременно с передачей данных между запоминающим блоком 1 и периферийным блоком 3, блок контроля 7 п меткам времени, поступающим из блока управления 4, считает контрольный вре менной интервал, счет продолжается и в состоянии ожидания, При правильной работе процессора 6 заданная длительность контрольного временного интервала заведомо больше интервала времени между обращениями процессора 6 к устройству для передачи данных. В режим автоматического списывания устройство переходит по сигналу конца временного интервала посланного блоком контроля 7 в блок управления, 4. Этот сигнал вырабатывается, если интервал времени между соседними обращениями процессора 6 к устройству для передачи данных превышает длительность заданного временного йн-тервала. Первый контрольный интервал формируется блоком контроля 7 схемно, при включении системы. В даль нейщем его значение может заменяться кодом, посылаемым процессором 6 в блсж контроля 7 при обращении к устройству для передачи данных. При получении сигнала на переход в режим автоматического списывания блок управления 4 посылает в формирователь 8 адреса признак передачи адреса. Формирователь 8 адреса вырабатывает код и передает его в блок формирования 5. Первоначальный адрес форми8руется схемно привключении устрсЛства и может затем заменяться кодом, посылаемым процессором 6 в формирователь 8 адреса. После Передачи адреса автоматического списывания блок управления 4 посылает в блок формирования 5 и в процессор 6 признак обрашения Е запсадинающему блоку 1 и весь цикл обмена проводится аналогично режиму передачи данных по командам процессора. После окончания передачи в периферийный блок 3 содержимого зоны автоматического списывания, блок фор мирования 5 посылает в блок управления 4 признак последнего слова массива. При совпадении этого признака с физнаком конца контрольного интервала времени режим повторяется. После получения от процессора 6 соответствующей последователыостк команд устройство переходит в режим п едачи данных по командам процессора. Использование предложенчого устройства для передачи данных позволяет передавать информашио из запоминающего блока вычислительной машины в периферийный блок в автоматическом режиме без управления со процессора. Это позволяет выпсшнить ряд дополнительных задач, например контроля и диагностики отказов процессора. Решение подобных задач является особенно важным при отработка управл$пощих систем с ограниченным доступом или без доступа к оборудованию. Формула изобретения Устройство для передачи данных, содержащее запоминающий блок, связанный через буферный накопитель с нертферийным блоком, бл1ж управления, первый выход которого подклхпен к управляющему входу буферного накопителя, а второй выход - через блок формирования текущего адреса подключен к управляющему входу запоминающего блока, причем управляющий выход периферийного блока подключен к первому входу блоке управления, к второму входу которого подключен другой выход блока формирования текущего адреса, к информадиониому входу которого и к третьему входу блока управления подключен выход процессора, отличаюшееся тем, что, с пелью устранения nepe &iвов в передаче данных при возникновеНИИ отказов процессора, введены блок кштроля временного интервала и формирователь адреса автоматического счиоываняя, к информаиионным входам которых подключен выход процессора, к управлякхцему входу которого подключен третий выход блока управления, четвертый выход которслго подключен к управляюшему входу формирсжателя адреса автоматического считывания, выход подключен к дсшолнительному

Информационному входу блсжа формирования текущего адреса, а пятый выход блока управления подключен к управляющему входу блока контроля временного интервала, выход которого подключен к четвертому входу блока управления.

Источники информации, принятые во внимание при экспертизе

1. Патент Франции № 2191770, Ел.а 06 Г 3/04, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2011 |

|

RU2444052C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| Устройство для отладки программ | 1979 |

|

SU849218A1 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство оперативной связи с управляющими программами | 1981 |

|

SU970351A1 |

| УСТРОЙСТВО ДЛЯ СБОРА, ОБРАБОТКИ И ПАКЕТНОЙ ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2080653C1 |

| Отказоустойчивая вычислительная система | 1981 |

|

SU1077070A1 |

| УСТРОЙСТВО СБОРА, ПРЕОБРАЗОВАНИЯ И ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2079882C1 |

Авторы

Даты

1979-01-15—Публикация

1976-05-03—Подача