второго процессора, третья группа управляющих выходов которого подклю чема к управляющим входам блока связи, адресный выход второго процессора подключен к первому входу третьего мажсфитарного элемента, выход которого подключен к адресному входу второго блока памяти, соединенного инфсфмационным входом с инфс мационными входаки узла микропрограммного управления, блока связи и выходом четвертого мажоритарного элемента, первый вход которого подключен к информгщионному выходу второго процессора, синхронизирую&в1М выходом подключенного к синхронизирующему входу узла микропрограммного управления, вторые и третьи входы мажоритарных элементов соединены соответственно с первы1«а1 входами одноименных мажоритарных элементов соседнего блока управления,

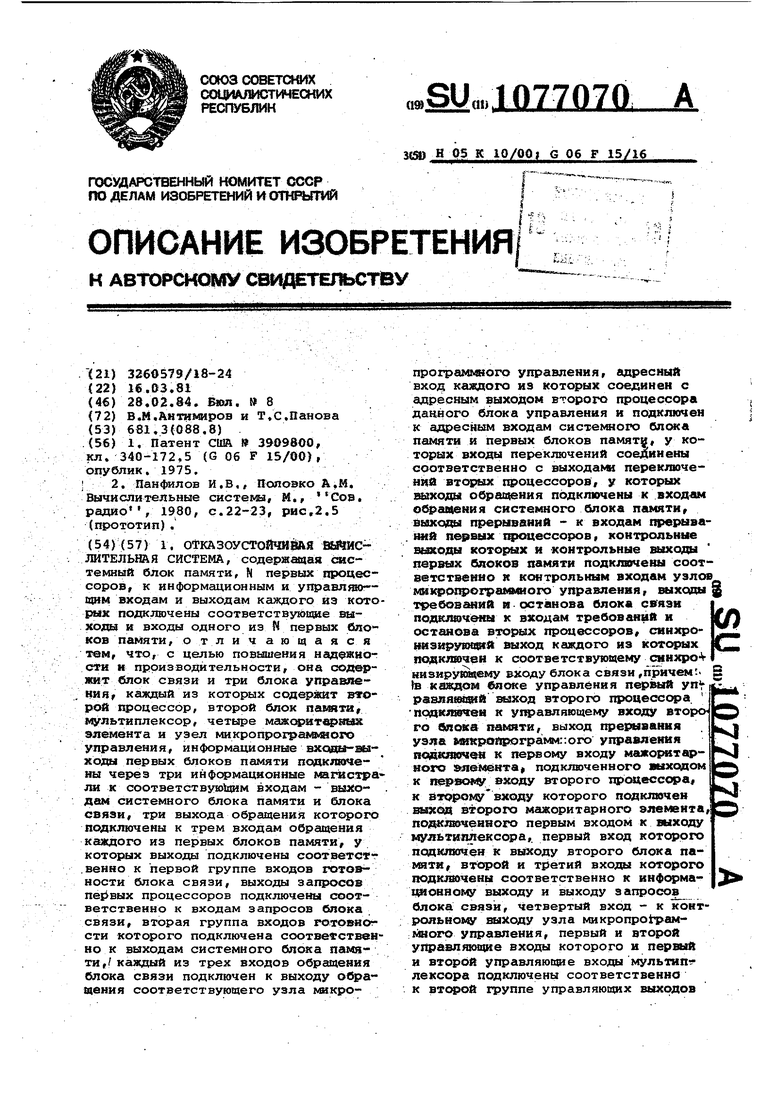

2. Система по п. 1, отличающаяся тем, что узел микропрограммного управления содержит блок оперативной памяти, элемент ИЛИ-НЕ, элемент НЕ, два счетчика, регистр неисправности, регистр сдвига, элемент ИЛИ, элемент И-НЁ, три элемента И и бло( долговременной памяти, причем первый вход первого элемента И, управляющие входы блоков оперативйой и долговременной памяти и стробирующий вход регистра сдвига подк. Лючены соответственно к первым управляющим входам узла, входы обнуления счетчиков, регистра неисправности и регистра сдвига подключены к вторым управляю щим входам узла микропрогра1Ф4ного управления, выход обращения которого является выходом первого элемента И, второй вход которого соединен с выходом блока долговременной памяти, адресный вход которого соединен с выходом блока оперативной памяти и выходами первого и второго счетчиков, стробирующие входа которых соединены соответственно с выходс1ми второго и третьего элементов И, первые входы KOTOfo x соединены со стробирующим входом регистра сдвига, второй вход .третьего элемента И соединен с выходом элемента НЕ, вход которого соединен с вторым входом второго элемента И и выходом регистра сдвига, информационный вход которого соединен соответственно с выходом регистра неисправности и входом элемента ИЛИ, выход которого является выходом прерывания узла, контрольные входы которого соединены с входами элемента ИЛИ-НЕ, выход которого и инверсный выход регистра неисправности соединены с соответствующими вxoдa м элемента И-НЕ, выход которого соединен с информационным входом регистра неисправности и является контрольным выходом узла, синхронизирующий вход которого соединен со стробирующим входом регистра неисправности, а адресный и информационный входы - с соответствующик входами блока оперативней памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Процессор ввода-вывода | 1979 |

|

SU798782A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

1. ОТКА ЗОУСТОЯЧИ ЛЯ ИЙИСЛИТЕЛЬНАЯ СИСТЕМА, содержащая системный блок памяти, N первых процессоров, к информс1ционным и угфавлщо- щим входам и выходам каждого из котоF ut подключены соответствующие аыХоды и входы одного из f первых блоков пгичяти, о тличающаяся тем, что, с целью повышения надежности и производительности, она содержит блок связи и три блока управления каждый из которых содержит второй процессор, второй блок пав«яти мультиплексор, четыре мажоритарных элемента и узел микропрогра 1а4вого управления, информационные вхсщы-выходы первых блоков памяти подключены через три инфс мацяонные магистра jra к соответствую м входам - шахо- . дам системного блока памяти и блока связи, три выхода обращени;я которого подключены к трем входам обращения каждого из первых блоков памяти, у которых выходы подключены соответрстг .венно к первой группе входов готовности блока связи, выходы запросов процессоров подключены соответственно к входам запросов блока связи, вторая группа входов готрвног сти подключена соответственно к выходам системного блока памяти,/ каждый из трех входов обрёоцения блока связи подключен к выходу обращения соответствующего узла гдакроnpoxpaN04Horo управления, ащ есный вход каждого из которых соединен с адресным выходом второго процессора данного блока управления и подключен к адфесным входам cиcтe eIoгo блока памяти и первых блоков памят|;, у которых входы переключений соединены соответственно с выходами переключений процессоров, у которых 1ШХОДЫ обращения подключены к входам обращения системного блока памяти, Ёыходы прерываний - к входам прерыва. НИИ первых щюцессоров, контрольные выходы которых и контрольные ъахотл первых блоков памяти подключены соответственно и контрольным входам узлов микропрогршвшого управления, выходы § требований и останова блока связи подключены к входам требований и останова вторых процессоров, сиихро(шзирувяяий выход каждого из которых подключен к соответствующему сярнхро-У низиру ему вход у блок a с вязи, причем:te каждом же управления первый уп равля( выход второго процессора. подкяячеи к ущ авляющему входу второ го блока памяти, выход пресмвання 4 узла ввП{ройрогра1«м;:ого управления попкжочея к первому входу мажоритарО ного элемента« подключенного выходом к nis&jBoviy входу второго процессора, к входу которого подключен Овыхсш второго мажоритарного элемеита, подк;ше чеиного первым входом к выходу мульти1глексора, первый вход КОТОРОГО подключен к выходу второго блока памяти второй и третий входа которого подклаочены соответственно к инфс мас онному выходу и выходу запросов блока связи, четвертый вход - к контрольноьог выходу узла микропро11)ам:NBioro управления, первый и второй утфавляющие входы которого и первый и второй управляющие входы мультипг лексора подключены соответственно к втсфой группе управляющих выходов

; , Г

Изoбpeteниe ОТНОСИТСЯ К вычислительной технике и может быть испольбовано при построении цифровых вычислительных систем пов1Л11енной производительности и надежности,5

Известна система обработки иифорМгщии, содержащая процессор, соединенный с запоминающими устройствами 1 периферийным процессором, В этой Системе задачу передачи данных и их Yo ЧАСТИЧНОЙ обработки по командам от вентрального процессора выполняет 1ериферийный процессор ij.

Недостатком данной системы является узкая специализация периферий- е Мого и центрального процессоров, что Ох ешичивает повышение производительности при изменении состава задач, Роме того, отк-аз любого из блоковПриводит к отказу системы в цепом, снижает ее надежность, ..20

Известна вычислительная система, вОдержащая блоки оперативной памяти

и внешней памяти, ком татор и х процессоров, каждый из которых имеет свои блоки памяти. Обмен информацией между процессорами и общим блоком памяти, в известной системе осуществляется через коммутатор 2 .

Однако известная система характеризуется недостаточной надежностью, так как отказ кОммутатора приводит к отказу системы, Кроме того, связь процессоров с блока|ии оперативной и внешней памяти через коммутатор с организацией режима ожидания очередного обслуживания снижает производительность систе «.

Цель изобретения - рш:1шениё надежности и производительности вычислительной систекы.

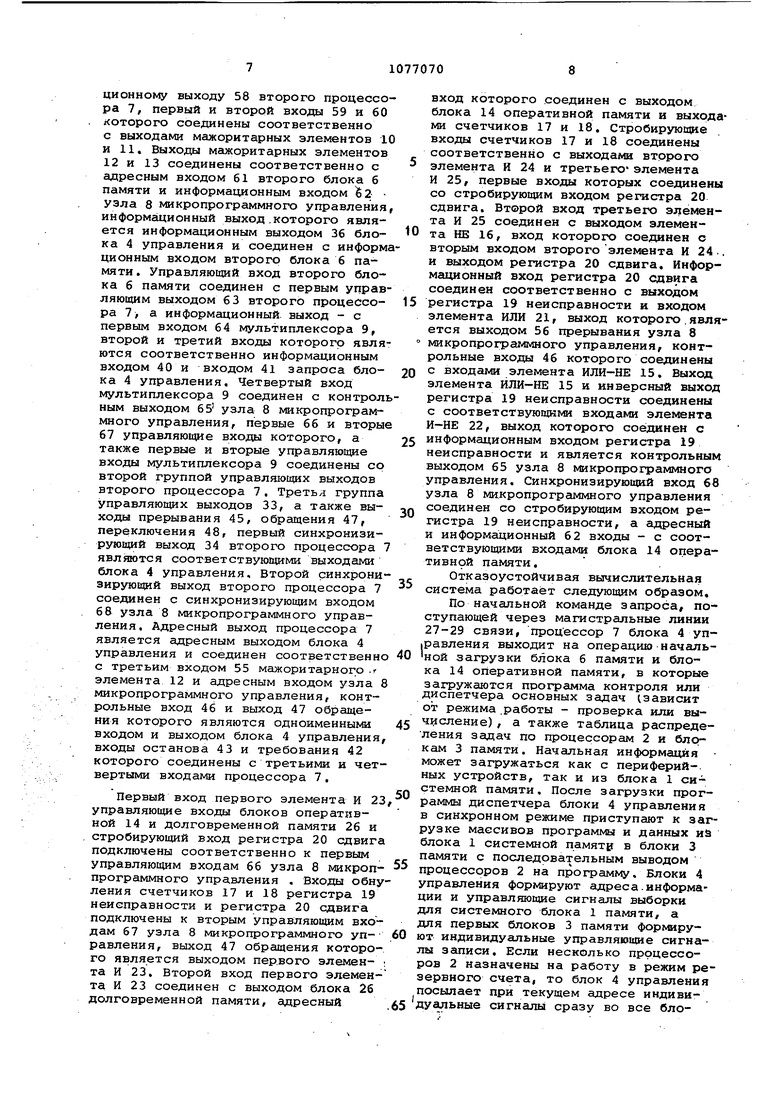

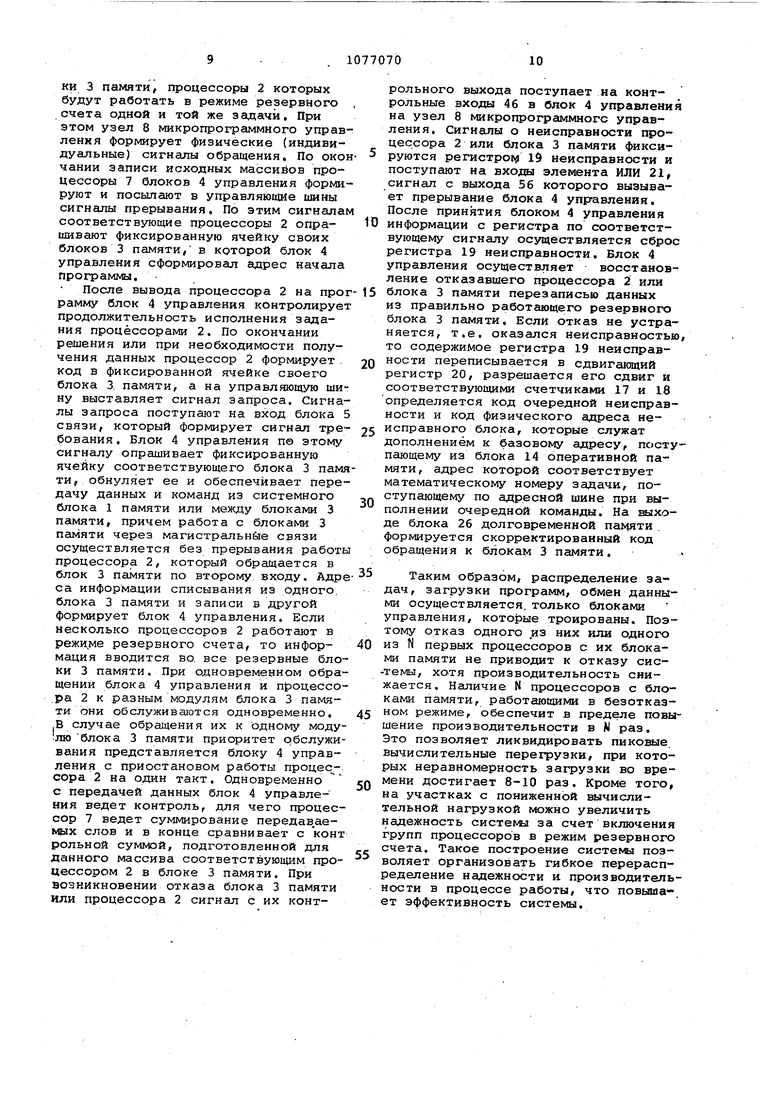

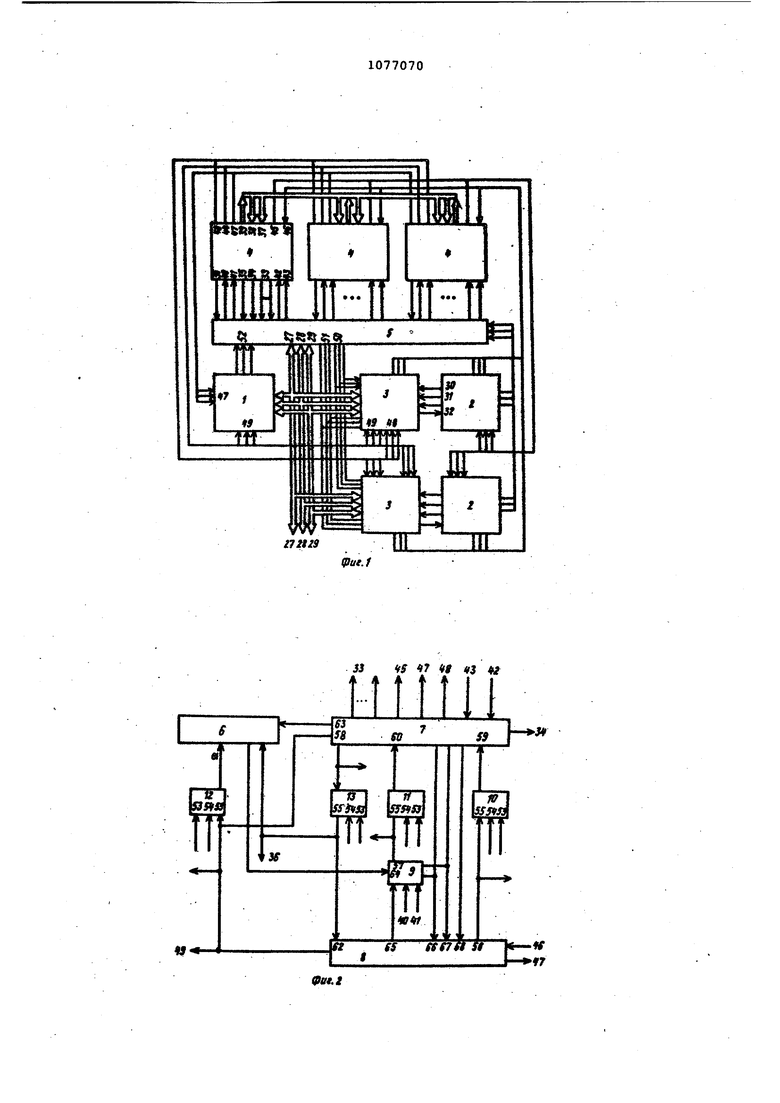

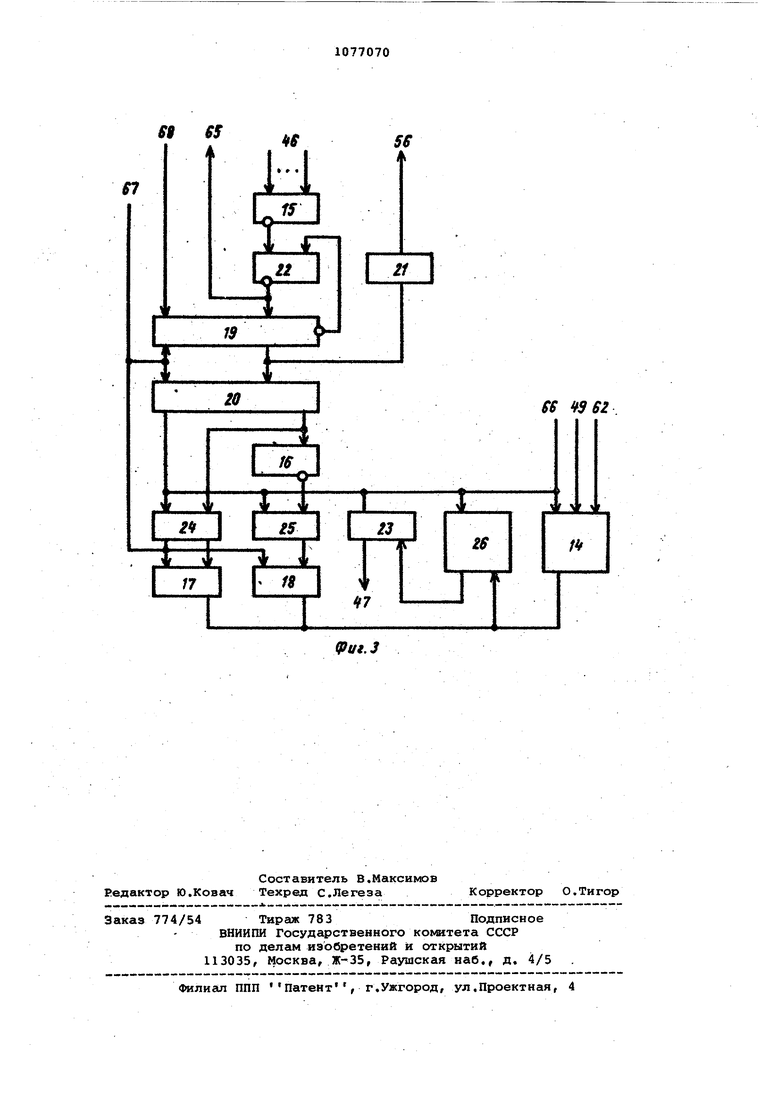

Поставленная цель достигается тем, что в вычислительную систему. Содержащую системный блок памяти,. N первых процессоров, к информационным и управляющим входам и выходам каждого из которых подключены соотйетствующие выходы и входы одного из W первых блоков памяти, введены блок связи и три блока управления, каждый из которых содержит второй процессор, второй блок памяти, муль типлексор, четыре мажоритарных элемента я узел микропрограммного упра лени я, ин формационные входам-выходы первых блоков памяти подключены через три информадисмные магистрали к соответствующим входам-выходам системного блока памяти и блока связи, три выхода обращения которого подключены к трем входам обращения каждо го из первых блоков памяти, у которых выходы подключены соответственно к первой группе входов готовности блока, связи, выходы запросов первых процессоров подключены соответственно к входам запросов блока связи, вторая группа входов готовности которого подключена соответственно к выходам системного блока памяти, каждый из трех входов обращения блока связи подключен к выходу обращения соответствующего узла микропрограммного управления, адресный вход каждого из которых соединен с адресным выходом второго процессора данно го блока управления и подключен к адресным входам системного блока памяти и первых блоков памяти, у ко торых входы переключений соединены соответственно с выходами переключений вторых процессоров, у которых выходы обращения подключены к входам обращения системного блока памяти, выходы прерываний - к входам прерываний первых процессоров, контрольные выходы которых и контрольные выходы первых блоков памяти подключены соответственно к контрольным входам узлов микропрограммного управления, выходы требований и останова блока связи подключены к входам требований и останова вторых процессоров, синхрониэируюидай таход каждого из которых подключен к соответствующему синхронизирующему входу блока связи, причем в каждом блоке ущ авления первый управляющий выход второго процессора подключен к управляющему входу второго блока памяти, выход пресшвания узла никропрограммного управления подключен к первому входу мажоритарного элемента, подключенного выходом к первому вхо ду второго процессора, к второму входу которого подключен выход второго мажоритарного элемента, подключенного первым входом к выходу мультиплексора, первый вход которого подключен к выходу второго блока памяти, второй и третий входы которого подключены соответственно к инфорМёщионному выходу и выходу запросов блока связи, четвертый вход - к конт рольному выходу узла микропрогргилмного управления, первый и второй управляющие входы которого и первый и второй управляюгцие входы мультйплексора подключены соответственно к второй группе управляющих выходов второго процессора, третья группа управляюооис выходов которого подключена к управляюошм входам блока связи, адресный выход второго процесссчра -подключен к первому входу третьего мажоритарного элемента, выход которого подключен к адресному входу второго блока памяти, соединенного информационным входом с информационными входами узла микропрограмАШрго управления, блока связи и выходом четвертого мажоритарного элемента, первый вход которого подключен к информационному выходу второго процессора, синхронизирующим выходом подключенного к синхронизирующему входу узла MHKponporpajvwHoro управления, вторые и третьи входы мажоритарных элементов соединены соответственно с первыми входалю одноименных мажоритарных элементов соседнего блока управления.«, Узел микропрограммного управления содержит блок оперативной памяти, элемент ИЛИ-НЕ, элемент НЕ, два счетчика, регистр неисправности, регистр сдвига, эпемеят ИЛИ, И-НЕ, три элемента И и блок долговременной памяти, причем первый вход первого элемента И, управляющие входы блоков оперативной и долговременной памяти и стробирующий вход регистра сдвига подключены соответственно к первым управляющим входам узла микропрограммного управления, входы обнуления счетчиков, регистра неисправности и регистра сдвига подключены к вторым управляющим входам узла микропрограммного управления, выход обращения которого является выходом первого элемента И,/второй вход которо1Ч соединен с выходом блока долговременной памяти,адресный вход которогосоединен с выходом оперативней памяти и выходами первого и второго счетчиков, стробирувэщие входы которых соединены соответственно с выходами второго и третьего элементов И, первые вхошл которых соединены со стробирующим входом регистра сдвига, второй вход третьего элемента И соединен с выходом элемента НЕ, вход которого соединен с вторым входом второго элемента И и выходом регистра сдвига, информационный вход которого соединен соответственно с выходом регистра неисправности и входом элемента ИЛИ, выход которого является выходом прерывания узла микропрограммного управления, контрольные , входы которого соединены с входами элемента ИЛИ-НЕ, выход которого и инверсный выход регистра неисправности соединены с соответствующими входами элемента И-НЕ,выход которого соединен с информационным входом регистра неисправности и является контрольным выходом .узла микропрограммного управления, синхронизирующий вход которого соединен со стробирующим входом регистра неисправно сти, а сщресный и .информационный ВХОДЫ- с соответствующими входами блока оперативной памяти. На фиг, 1 изображена структурная схема отказоустойчивой вычиещительйой системы; на фиг. 2 - структурна схема блока управления; на фиг.З структурная схема уэла микропрограм много управления. Отказоустойчивая ВЕЛчислительная система содержит блок. 1 системной памяти,.N первых процессоров 2, N первых блоков 3 памяти, три блока 4 управления и блок 5 связи. Блок 4 управления содержит второй блок б памяти, второй процессор 7, узел 8 микропрограммного управления мультиплексор 9 и четыре мажоритарных элемента 10-13. (. Узел 8 микpoпpoгpaм нoгo управления содержит блок 14 оперативной памяти, элемент ИЛИ-НЕ 15, элемент НЕ 16, первый 17 и второй 18 счетчики, регистр 19 неисправности, регистр 20 сдвига, элемент ИЛИ 21, элемент 22, первый 23, второй 24 и третий 25 элементы И и блок 26 долговременной памяти. Система содержит первую 27, вторую 28 Итретью 29 магистральные линий связи, информационную 30, адресную 31 и управляющие 32 шины процессоров 2; блоки 4 управления, содержащие группы управляющих выходов 33 выходы 34 синхронизации, выходы 35 обращения, информационные выходы 36 первые и вторые группы входов 37 и 38 мажоритации, группы выходов 39 мажоритадии, информационные входы 40 входы 41 запросов, входы 42 требований, входы 43 останова, адресные выходы 44, выходы 45 прерывания, контрольные входы 46, выходы 47 обращения, выходы 48 переключения, блок 5 связи,включающий троированные входы 49 запросов, выходы 50 обращения, входы 51 и 52 готовности, -первые 53 вторые 54 и третьи 55 входы мажоритарных элементов 10-13, выход 56 прерывания узла 3 микропрограммного управления, выход 57 прерывания мул типлексора 9, информационный вход 5 второго процесс.ора 7, первый 59 и второй 60 входы второго процессора адресный вход 61 второго блока памяти, информационный вход 62 угла микропрограммного управления, первый управляющий выход 6 3 второго процессора 7, первый вход 64 мультиплексора 9, контрольный выход 65 уэла 8 шкpoпpoгpaммнoгo управления, первые 66 и вторые 67 управляющие входы узла 8 микропрограммного уп- равления, синхронизирующий вход 68 узла 8 микропрограммного управления. Все первые блоки 3 памяти связаны между собой, а также с блоками 5 связи и блоком 1 системной памяти через три магистральные линии 27-29 связи, которые могут быть использованы для подключения дополнительных блоков памяти или внешних систем. Каждый первый блок 3 памяти связан с соответствующим первым процессором 2 через и-нформадионную 30, адресную 31 и управляющие 32 шины. Группы управляющих выходов 33 блоков 4 управления, а также выходы синхронизации 34, обращения 35 и информационные 36 соединены с соответствующими входами блока 5 связи, первые и вторые группы входов 37 и 38 и группы выходов 39 мажоритации блоков 4 управления связаны между собой. Информационные входы 40, входы запросов 41, требований 42 и останова 43 блоков 4 управления соединены с соответствующими выходами блока 5 Связи. Троированные входы 49 запросов, блока 5 связи соединены с соответствующими выходами каждого из первых процессоров 2, троированные входы прерывания которых соединены с выходами 45 прерывания блоков 4 управления. Троированные контрольные выходы первых процессоров 2 и каждого первого блока 3 памяти соединены с контрольными входами 46 блоков 4 управления, выходы обращения 47 которых соединены с соответствующими входами системного блока 1 памяти. Выходы 48 переключения каждого блока 4 управления соединены с соответствуюцщми входами переключения первых блоков 3 памяти. Адресный выход 44 каждого блока 4 управления соединен с соответствующими входами системного 1 и первого 3 блоков памяти. Выходы 50 обращения блока 5 связи соединены с соответствующими входами первых блоков 3 памяти, выходы сигналов готовности которых, а также выходы сигналов готовности системного блока 1 памяти соединены с соответствующими входами 51 и 52 блока 5 связи. Вторые и третьи входы 54 и 55 мажоритарных элементов 10-13 соединены со ответственно с первыми входами 53 одноименных мажоритарных элементов соседнего блока 4 управления. Третьи входы мажоритарных элементов 10, 11 и 13 подключены соответственно к выходу 56. прерывания узла 8 микропрограммного управления, выходу 57 прерывания мультиплексора 9 и информационному выходу 58 второго процессо ра 7, первый и второй входы 59 и 60 которого соединены соответственно с выходами мажоритарных элементов 10 и 11. Выходы мажоритарных элементов 12 и 13 соединены соответственно с адресным входом 61 второго блока б памяти и информационным входом 2- узла 8 микропрограммного управления информационный выход.которого является информационным выходом 36 блока 4 управления и соединен с информ ционным входом второго блока 6 памяти. Управляющий вход второго блока 6 памяти соединен с первым управ ляющим выходом 63 второго процессора 7 а информационный, выход - с первым входом 64 мультиплексора 9, второй и третий входы которого явля ются соответственно информационным входом 40 и входом 41 запроса блока 4 управления. Четвертый вход мультиплексора 9 соединен с контрол ным выходом 65 узла 8 микропрограммного управления, первые 66 и вторы 67управляющие входы которого, а также первые и вторые управляющее входы мультиплексора 9 соединены со второй группой управляющих выходов второго процессора 7. Третья группа управляющих выходов 33, а также выходы прерывания 45, обращения 47, переключения 48, первый синхронизирующий выход 34 второго процессора являются соответствующими выходами блока 4 управления. Второй синхрони зирующий выход второго процессора 7 соединен с синхронизирующим входом 68узла 8 микропрограммного управления. Адресный выход процессора 7 является адресным выходом блока 4 управления и соединен соответственно с третьим входом 55 мажоритарного . элемента 12 и адресным входом узла микропрограммного управления, контрольные вход 46 и; выход 47 обращения которого являются одноименными входом и выходом блока 4 управления входы останова 43 и требования 42 которого соединены с третьими и чет вертыми входами процессора 7, Первый вход первого элемента И 2 управляющие входы блоков оперативной 14 и долговременной памяти 26 и стробирующий вход регистра 20 сдвига подключены соответственно к первым управляющим входам 66 узла 8 микроппрограммного управления . Входы обну ления счетчиков 17 и 18 регистра 19 неисправности и регистра 20 сдвига подключены к вторым управляющим входам 67 узла 8 микропрограммного управления, выход 47 обращения которого является выходом первого элемента И 23, Второй вход первого элемента И 23 соединен с выходом блока 26 долговременной памяти, адресный вход которого соединен с выходом блока 14 оперативной памяти и выходами счетчиков 17 и 18, Стробирующие входы счетчиков 17 и 18 соединены соответственно с выходами второго элемента И 24 и третьего- элемента И 25, первые входы которых соединены со стробирующим входом регистра 20 сдвига. Второй вход третьего элемента И 25 соединен с выходом элемента НЕ 16, вход которого соединен о вторым входом второгоэлемента И 24,. и выходом регистра 20 сдвига. Информационный вход регистра 20 сдвига соединен соответственно с выходом регистра 19 неисправности и входом элемента ИЛИ 21, выход которого.является выходом 56 прерывания узла 8 микропрограммного управления, контрольные входы 46 которого соединены с входами элемента ИЛИ-НЕ 15. Выход элемента ИЛИ-НЕ 15 и инверсный выход регистра 19 неисправности соединены с соответствующими входами элемента И-НЕ 22, выход которого соединен с информационным входом регистра 19 неисправности и является контрольным выходом 65 узла 8 микропрограммного управления. Синхронизирующий вход 68 узла 8 микропрограммного управления соединен со стробирующим входом регистра 19 неисправности, а адресный и информационный 62 входы - с соответствующими входами блока 14 оперативной памяти, Отказоустойчивая вычислительная система работает следующим образом, По начальной команде запроса, поступающей через магистральные линии 27-29 связи, процессор 7 блока 4 уп.равления выходит на операцию начальной загрузки блока 6 памяти и блока 14 оперативной памяти, в которые загружаются программа контроля или диспетчера основных задач iзависит от режима.работы - проверка или вычр1сление) , а также таблица распределения задач по процессорам 2 и блокам 3 памяти. Начальная информация может загружаться как с периферий-, ных устройств, так и из блока 1 системной памяти. После загрузки программы диспетчера блоки 4 управления в синхронном режиме приступают к загрузке массивов Программы и данных из блока 1 системной памятр в блоки 3 памяти с последовательным выводом процессоров 2 на программу. Блоки 4 управления формируют адреса.информации и управляющие сигналы выборки для системного блока 1 памяти, а для первых блоков 3 памяти формируют индивидуальные управляющие сигналы записи. Если несколько процессоров 2 назначены на работу в режим ре зервного счета, то блок 4 управления посылает при текущем адресе индивидуальные сигналы сразу во все блоки 3 памяти, процессоры 2 которых будут работать в режиме резервного счета одной и той же задачи. При этом узел 8 микропрограммного управления формирует физические (индивидуальные) сигналы обращения. По окон чании записи исходных массивов процессоры 7 блоков 4 управления формируют и посылают в управляющие шины сигналы прерывания. По этим сигналам соответствующие процессоры 2 опрашивают фиксированную ячейку своих блоков 3 памяти, в которой блок 4 управления сформировал адрес начала программы. После вывода процессора 2 на прог рамму блок 4 управления контролирует продолжительность исполнения задания процессорами 2. По окончании решения или при необходимости получения данных процессор 2 формирует. код в фиксированной ячейке своего блока 3. памяти, а на управляющую шину выставляет сигнал запроса. Сигналы запроса поступают на вход блока 5 связи, который формирует сигнал требования. Блок 4 управления п© этому сигналу опрашивает фиксированную ячейку соответствующего блока 3 памя ти, обнуляет ее и обеспечивает пере дачу данных и команд из системного блока 1 памяти или между блоками 3 памяти, причем работа с блоками 3 памяти через магистральные связи осуществляется без прерывания работы процессора 2, который обращается в блок 3 памяти по второг 1у входу. Адр са информации списывания из одного, блока 3 памяти и записи в другой формирует блок 4 управления. Если несколько процессоров 2 работают в режи.ме резервного счета, то инфорМсщия вводится во. все резервные бло ки 3 памяти. При одновременном обра щении блока 4 управления и процессо .ра 2 к разным модулям блока 3 памяти они обслуживаются одновременно, В случае обращения их к одному моду лю блока 3 памяти приоритет обслужи вания представляется блоку 4 управления с приостановом работы процес сора 2 на один такт. Одновременно с передачей данных блок 4 управлеВИЯ ведет контроль, для чего процессор 7 ведет суммирование передав.аелвлх слов и в конце сравнивает с конт рольной суммой, подготовленной для данного массива соответствующим процессором 2 в блоке 3 памяти. При возникновении отказа блока 3 памяти или процессора 2 сигнал с их контрольного выхода поступает на контрольные входы 46 в блок 4 управления на узел 8 микропрограммного управления. Сигналы о неисправности процессора 2 или блока 3 памяти ксируются регистрои 19 неисправности и поступают на входаа элемента ИЛИ 21, сигнал с выхода 56 которого вызывает прерывание блока 4 управления. После принятия блоком 4 управления информации с регистра по соответствующему сигналу ос5лцествляется сброс регистра 19 неисправности. Блок 4 управления осуществляет восстановление отказавшего процессора 2 или блока 3 памяти перезаписью данных из правильно работающего резервного блока 3 Псшяти, Если отказ не устраняется, т.е. оказался неисправностью, то содержимое регистра 19 неисправности переписывается в сдвигающий регистр 20, разрешается его сдвиг и соответствующими счетчиками 17 и 18 определяется код очередной неисправности и код физического адреса неисправного блока, которые служат дополнением к базовому адресу, поступающему из блока 14 оперативной памяти, адрес которой соответствует математическому номеру задачи, поступающему по адресной шине при выполнении очередной команды. На ылходе блока 26 долговременной . формируется скорректированный код обращения к блокам 3 памяти. Таким образом, распределение задач, загрузки программ, обмен данными осуществляется, только блоками управления, которые троированы. Поэтому отказ одного из них или одного из N первых процессоров с их блоками памяти не приводит к отказу сис-темы, хотя производительность снижается. Нсшичие N процессоров с блоками памяти, работающими в безотказном режиме, обеспечит в пределе повышение производительности в N раз. Это позволяет ликвидировать пиковые вычислительные перегрузки, при которых неравномерность загрузки во времени достигает 8-10 раз. Кроме того, на участках с пониженной вычислительной нагрузкой можно увеличить надежность системы за счет включения групп процессоров в режим резервного счета. Такое построение системы позволяет организовать гибкое перераспределение надежности и производительности в процессе работы, что повыша. ет эффективность системы.

«7

«

3IL

Ж

3t

p:

Ж

ж

S3 f$ 47 W «J «

ttlllll

иг. 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Панфилов И.В., Половко A.M | |||

| Вычислительные системы, М., Cos, радио, 1980, с.22-23, рис.2.5 (прототип). | |||

Авторы

Даты

1984-02-28—Публикация

1981-03-16—Подача