I

Изобретение относится к радиотехнике и может быть исншьзовано в устройствах, обеспечивающих анализ адресной посылки в виде непрерывного кода на соответствие одному из нескол1: их абсшентов при использовании ошюй лвнвв для вызова нескольких абонентов на прнемнс сторсше.

Известно устройство для анализа адреснс посылки, содержашее регистр сдвига, выходы которого подключены к первым входам вентилей, втсфые входы кото{илх через дешифратор подключены к выходам первого делителя, вход которого через блсж синхроиизаиик подключен к первому входу регистра сдвига и к входу второго делителя, выходы которого через второй дешифратор подключены к первым входам ключей и к входам соответствующих адресных блоксйв, выходы которых подключены к третьим входам вентилей, а также последовательно соединенные триггер и блок сравнения, при этом донолнительный выход дешифратора подалю:чен S. второму входу регистра сдш1гаШ .

Однако взвестное устройство отлв4 №тса сложностью, так как для храве ния результат(мв сравненна необходимо вмеп отдел Ый т яггер и отдельный блок сравнения для каждого адреса.

Целью изобретения является уцрошенее }1с;тройства путем уменьшения количества трвггер(ш я блоков сравнение.

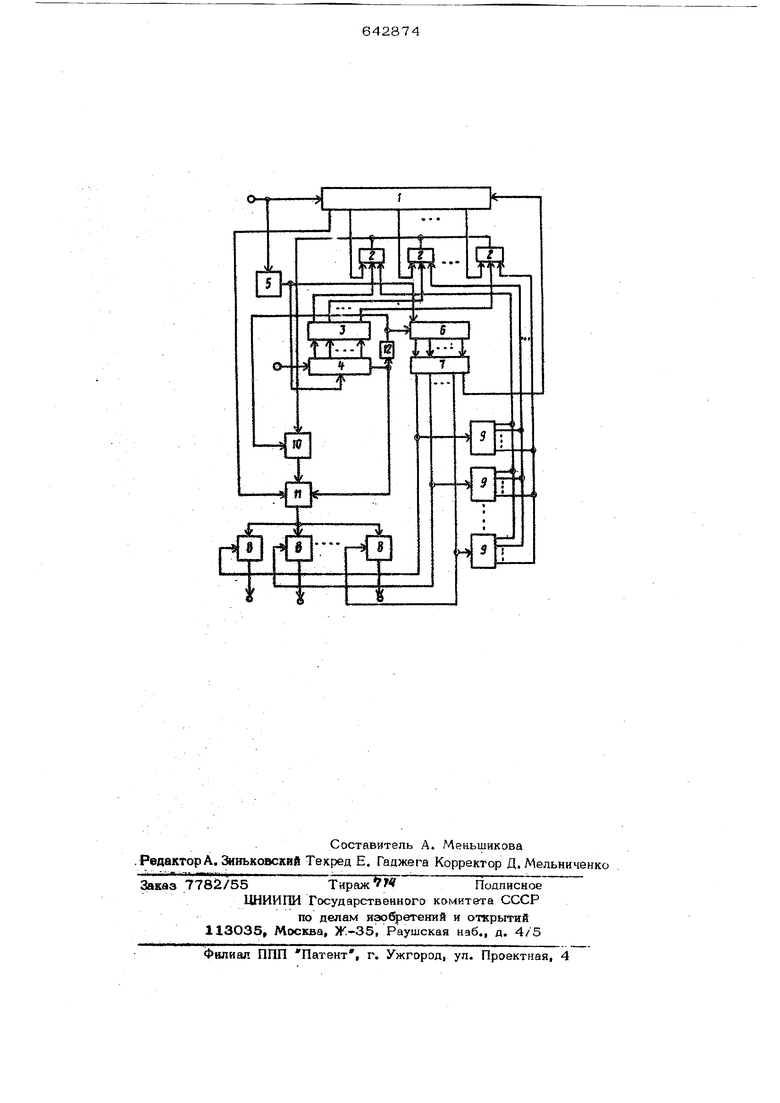

Для в устрс ство для анализа ащ}есной аосылки, содержашее регистр сдвнга, выходы которого подключены к вховам вентилей, вторые входы которых первый дешифратор подключены к выходам первого делителя, вход которого блок синхронизации подключен к первому входу регистра сдвига и к входу второго делителя, выходы которого через второй дешифратор подключены к первым входам ключей и к входам соответствующих адресных блоков, выходы которых подключены к третьим входам вентилей, а также после36довагельно соединетпле триггер и блок сревненвя, нри этом дополнительный второго дешифратора подключен к второму входу регистра сдвига, введено пнния задержки, при этом дополнительный выход первого делителя через линию задержки подключен к другому входу второго делителя и к первому входу триггера, второй вход которого соединен с выходами вентилей, дополнятельный в№яод регистра сдвига подключен к второму взюду &1ока сравнешш, третий вход которого соединен с входом линии задержки, а выход блока сравнения подключен к вторым входам ключей. На чертеже пpи.ieдeнa структурная элек Ррическая схема устройства. Устройство для анализа адресной посылки сйдержит регистр сдвйга 1, выходы которого подключены к перщдм вхо дам вентилей 2, вторые входил кот(яых через первый дешифратор 3 номера вентиля подключены к выходед нервсгго делителя 4, вход KOTOpcwo через блок сивхровнаадии 5 подключен к первому входу регистра сдвига 1 и к входу второго делителя 6, выходы которого через второй дешифратор 7 номера адресного блока подключены к первым входам ключей 8 и к входам соответствующих адресных блоков 9, выходы которых подключены к третьим входам вентилей 2, а также иосдедователшо соединенные триггер 1О и блок сравнения 11, при этом дополнительный выход второго дешифратора 7 подключен к второму входу регистра сдвига 1, введенную линию задержки 12 при &ТОМ дополни те льхный выход первого делителя 4 через линию задержки 12 подключен к другому входу второго дели теля 6 и к первому входу триггера 10, второй вход которого соединен с выхода ми вентилей 2, дсшолнительный выход ре гистра Сдвига 1 подключен к второму входу блока сравнения 11, третий вход которого соединен с входом пинии задержки 12, а выход блока сравнения 11 подключен к вторым входам ключей 8. Устройство работает следующим образом. Бходшые сигналы адресной посылки йоступают на вход регистра сдвига 1 и на блгас синхронизации 5. Псюле каждого импульса, поступившего в первый разряд регистра сдвига 1, записывается вновь поотуш1вший сигнал. Бяок синхронизации 5 осуществляет установку первого делителя- 4 и второго делителя 6. в исходное состояние. В исходном состоянии первый делитель 4 находится в нулевом состоянии и на выходе дешифратора 3 номера вентиля отсутствуют сигналы, а второй делитель 6 находится в первом состоянии и на первом выходе дешифратора 7 номера адресного блока имеется сигнал, который подается иа первый адресный блок 9 и на вход первого ключа 8. На делитель 4 поступают тактовыеимпульсы, которые прогзигают первый делитель 4 и через дешифратор 3 номера вентиля опрашивают все вентили 2. Так как сигнал с дешифратора 7 номера адресного блока поступает на первый адресный блок 9, то сравнение происходит н соответствие первому адресу. При опросе вентилей 2 по коду первого адарса импульсы, с выходов вентилей (при совпадении сигналов на всех трех входах вентиля) поступают на счет ный вход триггера Ю. Таким образом, после первого цикла первого делителя 4 обеспечивается сложение по модулю два тех N разрядов регистра сдвига 1 (кроме первого разряда), которые определены первым адресным блоком 9, и результат сложения записывается в триггер 10. Очередной тактовый импульс переведет делитель 4 в исходное положение и на его выхрде появляется сигнал, который поступает на вход линии задержки 12 и на управляющий вход блока сравнения 11. Происходит сравнение результата, записанйого в триггере Ю, с первым разрядом регистра и результат сравнения с выхода блока сравнения 11 через первый ключ 8 поступает на выходную шину, так как открыт только первый ключ 8 первым выходом деши||фатора 7 номера адресного блока. Следовательно, в первом цикле происходит сравнение N последних разрядов регистра сдвига 1 по коду первого адреса с содержимым первого разряда регистра сдвига 1. Далее импульс с линии задержки 12 переводит второй делитель 6 во второе состояние и на втором выходе дешифратора 7 появляется сигнал, который подается на второй адресный блок 9, открывает второй ключ 8 к устанавливает триггер 1О в нулевое ссх:тояние. Поступающие тактовые импульсы производят второй цикл сдвига первого да/1ителя 4, и происходит опрос вентилей 2 по коду второго адреса, результаты сложения по модулю два последних разрядов регистра сдвига 1, определенных вторым адресным блсжом 9, записываются в триггер 1О. После завершения второго цикла первым делителем 4 прсжсходит сравнение состояния триггера Ю с содержимым первого разряда регистра сдвига 1, результаты сравнения через открытый второй ключ 8 поступают на вторую выходную шину.

Далее устройство работает аналогичным образом: в каждом новом цикле проверяется соответствие содержимого первого разряда регистра сдвига 1 с результатом сложения по модулю два последних N разрядов регистра сдвига 1, еяределенкых соответствующим адресным блоком 9. До прихода нового входного сигнала осуществляется опрос всех адресов. После последнего цикла последним выходом дешифратора 7 производится сдвиг содержимого регистра сдвига 1 на один разряд вправо. В результате такого построения устройств ва необходимы один триггер 10 и один блок сравнения 11 при любом количестве одновременно анализируемых адресов. В прототипе же для каждого адреса необходим свой триггер и свой блок сравнения.

Следовательно, предложенное устройство упрощается по сравнению с прототипом при сохранении основных технических характеристик устройства.

Формула изобретения

Устройство для анализа адресной посылки, содержащее регистр сдвига, выходы которого подключены к первым входам вентилей, вторые входы которых через первый дешифратор подключены к иыходам первого делителя, вход котчзрого через блок синхронизации подключен к первому входу регистра сдвига и к входу второго делителя, выходы которого через второй дешифратор подключены к первым входам ключей и к входам соответствующих адресных бл1жов, выходы которых подключены к третьим входам вентилей, а также последовательно соединенные триггер и сравнения, при этом дополнительный выход второго дешифратора подключен к второму входу регистра сдвига, о т л ичаю щееся тем, что, с целью упрощения устройства путем уменьшения количества триггеров и блоков сравнения, введена линия задержки, при этом дополнительный выход первого делителя через линию задержвш подключен к другому входу второго делителя и к перйомУ входу триггера, второй вход которого соединен с выходами вентилей, ДСЯ10ЛНИтельный выход регистра сдвига подключен к второму входу блока сравнения, третий вход которого соединен с входом линии задержки, а выход блетса сравнения подключен к вторым входам ключей.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 403119, кл. Н 04 Q 5/16, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для сигнализации о состоянииРАССРЕдОТОчЕННыХ Об'ЕКТОВ | 1978 |

|

SU802981A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Электролидер плавательного бассейна | 1980 |

|

SU883941A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1136173A1 |

Авторы

Даты

1979-01-15—Публикация

1977-02-01—Подача