(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКОВ СООБЩЕНИЙ С ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНОЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1976 |

|

SU643861A1 |

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1980 |

|

SU920693A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1985 |

|

SU1322300A1 |

| Устройство для сопряжения основной и вспомагательных цифровых вычислительных машин | 1976 |

|

SU641438A1 |

| Устройство для сопряжения источников сообщения с цифровой вычислительной машиной | 1984 |

|

SU1196880A1 |

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1976 |

|

SU615472A1 |

| Устройство для сопряжения цифровой вычис-лиТЕльНОй МАшиНы C КАНАлАМи СВязи | 1979 |

|

SU840876A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

Изобретение относится к области вычислительной гехншш, в частности, к устройствам для сопряжения источников сообщений с ЦВМ и. может быть испрль- зовано в системах обработки данных.

Известно многоканальное устройство для сопряжения источников сообщений с ЦВМ rij содержащее блок формирова- кия кодов приоритетов, блок формирования адреса, блок памяти, блок управления, блок формирования номера позиции очереди, блок управления коммутацией, а в каждом канале тря KOMMyTaropia, регистр признака и регистр номера позиции очереди..

Недостаток устройства состоит в его значительной сложности и в необходимости затрат большого количества оборудования.

Наиболее близким к изобретению по технической сущности и достигаемому результату является многоканальное устройство для сопряжения источников сообщений с ЦВМ 21, содержащее блок

формирования адреса, первый вход которого соединен с входами устройства, блока памяти и блока управления, блок формирования номера позиции очереди, выход, которого соединен со вторым входом блока управления, выходной коммутатор, а в каждом канале регистр признака канала, вход которого соединен с выходом первого элемента ИЛИ канала, первый коммутатор, все каналы, кроме первого и последнего, содержат дополнительно вторые коммутаторы; причем выходы первого и второго ко гму-raTOjDOB канала соединены соответственно с первым и вторым входами первого элемента ИЛИ канала, вьхход блока формирования адреса соединен со BTOptiM входом блока памяти и с кодовыми входами первых коммутаторов каналов, каждый выход первой группы выходов блока управления соединен с управлякшшм входом первого коммутатора соответствующего канала, каждый выход второй группы выходов блока леШя соединен с управляющим входом iBfB BfD коммутатора соответствующего Шнапа, выходы регистров признака каналов соединены с первой группой вхо дов блока формирования номера позиции очереди, кодовый вход второго коммутаTopia канала соединен с выходом регист ра П ризнака предатдущего канаДа, выход регистра признака последнего канала сое диНёнс кодовым входом выходного коммутатора, управляющий вход и выход ко торого соединены соответственно с выxojDioM блока управления и третьим входо блока памяти, первый и, второйТвыходы которого соединены соответственно со вторым входом блока форййрбёаний адреса и с выходом устройства, а второй йсбд устрШстмсЪёотшн с входом блока управления, В известном устройстве не предусмот рена: возможность изМёнёнйя порядка расположения сообщений в зависимости от их срочности. Часто сообщения существенно, различаются по степени важности информации, а это необхо ЩмбуМтыёа гь при определений порядка выдачи сообщений в ЦВМ. Такая ситуа- « Ш 1бж т в5ёШМутГГТйГШ|)й1Иё1),-ТЁрй управлении несколькими объектами с помощью одной ЦВМ, когда невозможно отдать предпочтение какому-либо из объектов, но в каждый мШёнт ёремени необходимо в первую очередь оказывать управляющее воздействие на объект, находящийся в худщих, с точки зрения упрвёлёнйя, условиях:. Таким образом, недостаток устройства состоит в том, что сообщения в нем выдаются без учета срочности, а следовательно, на обслуживание срочных сообщений затрачивается Mkefб Времени. Цель изобретения - повыщение быстр действия. ПостЖЬйевйаГ Яёпь достигается тем, что устройство содержит блок фррмиро- Мния Кода Приоритета, а в каждом канале-регистр приоритета и второй элемент ИЛИ,в пёрёбм и пбслёднём кана n ei:: MifreWpa -aBr fOpomты и, в каждом канале, кроме первого и 1ШШсШё1 Ь, - 1:ШЩМто рйГ ; трётЬёГо по шестой кбдбвыё Входы второ- ро™й 4ё тйёрт ге ТсбКШутатбрОВ первого ШаШГ 1Гк6рГбШё Х8йь1- г-ретГёгб -и щестбго коммутаторов других каналов, кроме последнего, соединены с третьей груп пой выходов блока управления, кодовые входы второго и четвертого коммутат5 ров последнего канала соединены с выходами соответственно регистра дризнйка и регистра приоритета предыдущего канайа, управлятрщий вход второго коммутатора первого канала и управляющий вход третьего коммутатора кажрого Другого канала, кроме последнего, соединек С выходом регистра признака прследующего канала, управляющий вход четвертбго коммутатора первого канала и управл5пощий вход щестого коммутатора каждого другого канала, кроме последнего, соединен с выходом регистра приоритета последующего канала, кодовые входы третьих коммутаторов первого и последнего каналов и кодовые входы четвертых коммутаторов других каналов соединены с выходом блока формирова- ния кода приоритета, управляющий вход третьего коммутатора первого канала сбёдннен с управляющим входом первого коммутатора этого канала, управляющий вход четвертого коммутатора канала, кроме последнего, соединен с управляющим входом первого коммутатора канала, управляющий вход третьего коммутатора последнего канала соединен с управляющим вхбдом первого коммутатбра канала, управляпощий вход пятого коммутатора каждого канала, кроме первого и последнего, соединен с управляющим входом второго коммутатора канала, кодовый вход пятого коммутатора канала соединен с выходом регистра приоритета предыдущего канала, выход второго коммутатора первого канала соединен со вторьгм входом первого элемента ИЛИ первбго канала, выходы третьегб и четвёртого коммутаторов первого канала через второй элемент ИЛИ первого :кайала соединен со входом регистра приоритета первого канала, выход третьего коммутатора канала, кроме первого и последнего, соединен с третьим входом первого элемента ИЛИ канала, выходы четвертогог-щестого коммутаторов канала, кроме первого и последнего, через .второй элемент ИЛИ канала сое- динены со входом регистра приоритета Канала, выход второго коммутатора последнего канала соединен со вторым входом первого элемента ИЛИ последнего канала, третий и четвертый коммутаторы Последнего канала через второй элемент ИЛИ последнего канала соединены со входом регистра приоритета последнего канала, выходы регистров приоритета каналов соединены со второй группой

входов блока формирования номера позиции очереди, вход блока формирования кода приоритета соединен с первым входом устройства, а управляющие входы второго и четвертого коммутаторов последнего канала соединены с соответствующим выходом ВТОРОЙ группы выходов блока управления.

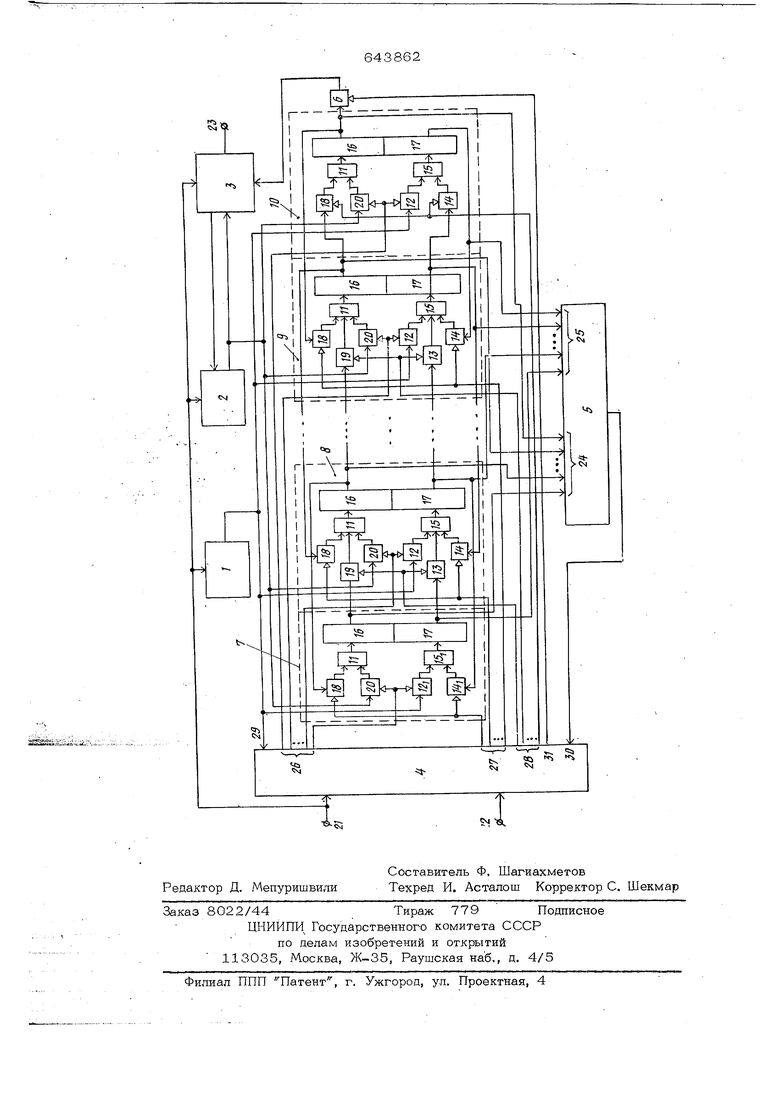

Структурная схема устройства представлена на чертеже.

Многоканальное устройство для сопряжения источников сообщений с ЦВМ содержит: блок 1 формирования кода приоритета, блок 2 формирования адреса, блок 3 памяти, блок 4 управления, блок 5 формирования номера позиции очереди, выходной коммутатор 6, первый канал 7, промежуточные каналы 8, 9 последний канал 10, каждый из каналов содержит элементы ИЛИ 11, коммутаторы 12-14, элементы ИЛИ 15, регистр 16 признака канала, регистр 17 приоритета, коммутаторы 18-20.

Кроме того, на чертеже обозначены 21, 22 входы устройства, 23 - выход устройства, 24, 25 - группы входов блока формирования номера позиции очереди, 26-28 - группы выходов блока управления, 29-30 - входы блока управления, 31 - выход блока управления.

Устройство работает следующим образом.

БЛОК 1 формирования кода приоритета в зависимости от содержания сообщения вырабатывает код приоритета, и может быть реализован в виде комбинационной схемы.

Блок 2 формирования адреса на основании адресной информации, поступающей из блока 3 памяти вырабатывает адрес свободной ячейки блока 3 памяти и может быть реализован как автомат с программным управлением или как функциональный автомат.

Блок 3 памяти выполняет функции оперативного запоминающего устройства для хранения поступающих сообщений.

Блок 4 управления вырабатывает операторы управления блоками устройства.

Блок 5 на основе анализа кодов приоритета, хранящихся в регистрах 17 каналов 7-10,и кодов номеров позиций очереди, хранящихся в регистрах 16 каналов 7-10, вырабатывает код номера позиции очереди.

Блок 5 может быть реализован на комбинационной схеме.

Для устройства характерны два режима работы.

Первый режим реализуется по приходе сообщения на вход 21 от источника и заключается в постановке признака прищедщего сообщегшя на позицию очереди в соответствии с состоянием очереди в момент его прихода. Состояние очереди определяется числом сообщений, стоящих в очереди, т.е. числом занятых регистров 16 каналов 7-10, а также приоритетами сообщений, стоящих в оче5реди. Постановка пршнедщего сообщения в очередь предполагает сдвиг в сторону последней позиции очереди (обратный сдвиг) всех признаков сообщений (а также соответствующих им пpиopитeтoв)

0 имеющих приоритеты меньще, чем у прощедшего сообщения, и запись признака прищедщего сообщения на освободивщееся место (в соответствующий регагстр 16 каналов 7-10).

5

Второй режим имеет место при поступлении служебного сигнала на вход 22. По этому сигналу ( конец обслуживания предыдущего сообщения) блок 4 управления вырабатывает последователь0но: на выходе 31 - сигнал выборки признака сообщения, CTosnnero на первой позиции очереди, в регистре 16 канала 10 и сигналы на выходах 28, назначение которых состоит в последовательной переписи признаков сообщений из регист ра 16 предыдущего канала в регистр 16 последующего канала (прямой сдвиг очереди ).

Рассмотрим функционирование устро.0ства в первом режиме.

Сообщение поступает на вход 21 устройства. Блок 2 формирования адреса вырабатывает код адреса ячейки блока 3 памяти, и поступивщее сообщение

5 записывается по этому адресу. Одновременно блок 1 формирования приоритета выдает код приоритета, соответствующий содержанию (важности) поступивщего сообщения. Поступившее сообщение воз0действует на блок 4 управления. В соответствии с сигналом от блока 5 и кодом приоритета постутгавшего сообщения от блока 1 формирования приоритета блок 4 управления на выходах 27 вырабаты5вает сначала сигналы, производ5пцие последовательную перепись приоритетов и признаков сообщений с приоритетами меньЩнми, чем у пришедщего сообщения. ИЗ регистра 16 одного канала в регистр 16преды душ его канала, через коммута торы 18 каналов 7-10 и одновременно перепись приоритета из регистра 17 прЕоригета одного канала в регистр 17 приоритета предыдущего канала через коммутатора 14, Затем вырабатывается один из сигналов на выходах 26, который производит запись кода адреса (признака) сообщения в регистр 16 признака через коммутаторы 20 и соответствующего кода приоритета в регистр 17приоритета через коммутатор 12. На этом постановка сообщения в очередь заканчивается. Рассмотрим функциошровааиё устройства во втором режиме. Поступает сигнал на вход 22. При этом блок 4 управления вырабатывает на выходе 31 сначала сигнал управлеНИЯ| который посылает адрес (признак) сообщения, стоящего на первой позишш очереди в регистре 16 канала 10 через выходной коммутатор-6 в блок 3 памяти. Затем блок 4 управления вырабатывает на выходах 28 посйейбвательно сигналы, осуществлякнцие посл:едовательную Перепись кодов прнзнако1в сообщений из регистров 16 одного из каналов 7-10 в регистры 16 последующего канала через соо5 вегствуклдне коммутаторы 19 и одновременно перепись кодов приоритетов из регистра 17 одного из каналов 7-10 в регистр 17 последующего канала через соответствующие коммутаторы 13 каналов 7-10. Изобретение позволяет сократить время обработки информации сокращения времени обслуживания сооб1пений, несущих более важную ниформаВИЮ. Например, в случае управления нес колькими объектами при помощи одной управлякхцей ЦВМ улучщается качество управления за счет уменьшения запаздатвання коррекции управляющего воз действия для объектов:, находящихся в зсудщях, с точки зрения управления, условиях. Либо при заданном качестве управления в роли управляющей ЦВМ может быть применена ЦВМ, обладающа меньщим быстродействием и, следовател нб меньщей стоимости. Формула Взоб ре тени Многоканальное устройство для соп ряжения источников сообщений с пифровой вычислительной машиной, содержащее блок формирования адреса, первый вход которого соединен с первыми входами устройства, блока памяти и блока упра-. вления, блок формирования номера позиции очереди, выход которого соединен со вторым входом блока управления, выводной коммутатор, а в каждом канале регистр признака канала, вход которого соединен с выходом первого элемента ИЛИ канала, первый коммутатор, все каналы, кроме первого и последнего, содержат дополнительно вторые коммутаторы, причем выходы первого и второго коммутаторов канала соединены соответственно с первым и вторым входами первого элемента ИЛИ канала, выход блока формирования адреса соединен со вторым входом блока памяти и с кодовыми входами первых коммутаторов каналов, каждый ВЫХОД первой группы выхо дов блока зправдетшя соединен с управляющим Ьходом первого коммутатора cooTBefствуктоего канала, каждый выход второй группы выходовблока управления соединен с управляющим входом второго коммутатора соответствующего канала, выходы регистров признака каналов соединены с первой группой входов блока форШфОЕ1ания номера позиции очереди, кодовый вход второго коммутатора канала сое дннен/с выходом регистра признака йредыдушего канала, выход регистра признака.последнего канала соединен с кодовьЫ входом выходного коммутатора, управлйющий вход и выход которого соединены соответственно с выходом блока-уйравйейия и третьим входомблока памяти, первый и второй выходы которого соединены соответственно со вторым входом блока формтфования адреса и с выходом устройства, а второй вход устройства соединён с третьим, входом блока управления, отличающ е и с я тем, что, с целью повышения быстродействия, оно содержит блок формирования кода приоритета, в каждом канале-регистр приоритета и второй элемент ИЛИ, в первом и последнем канала-коммутаторы со второго по четвертый, в каждом канале, кроме первого и юследнего, - коммутаторы с третьего по щестой причем кодовые входы второго и четвертого коммутаторов первого канала и кодовые входы третьего и щестого коммутаторов других каналов, кроме последнего, соединены с третьей группой выходов блока . управления, кодовые

входы второго и четвертого коммутаторов последнего канапа соединены с выходами соответственно регистра признака и регистра приоритета предыдущего канала, управляющий вход второго коммутатора первого канала и управпгпо- щий вход третьего коммутатора каждого другого канала, кроме последнего, соединен с выходом регистра признака последующего канала, управляющий вход четвертого коммутатора первого канала и управляющий вход шестого коммутатора каждого другого канала, кроме посленего соединен с выходом регистраприоритета последующего канала, кодовые входы третьих коммутаторов первого и последнего кайалов и кодовые входы четвертых коммутаторов других каналов соединены с выходом блока формирования кода приоритета, управляющий вход третьего коммутатора первого канала соединен с управляющим входом первого коммутатора этого канала, управляющий вход четвертого коммутатора канала, кроме последнего, соединен с управляющим входом первого коммутатора канала, управляющий вход третьего коммутатора последнего канала соединен с управляющим входом первого коммутатора этого канала, упраапяющий вход пятого коммутатора каждого канала, кроме первого и последнего, соединен с управляющим входом второго коммутатора канала, кодовый вход пятого коммутатора канала соединен с выходом регистра приоритета предыдущего канала выход второго коммутатора первого канапа соединен со вторым, входом первого элемента ИЛИ первого канала, выходы третьего и четвертого коммутаторов первого канала через второй элемент ИЛИ первого канала соединен со входом регистра приоритета первого канала, выход третьего коммутатора канала, кроме первого и последнего, соединен с третьим входом первого элемен-

та ИЛИ канала, выходы четвертого - щестого коммутаторов канала, кроме первого и последнего, через второй элемент ИЛИ канала соединены со входом регистра приоритета канала, выход второго коммутатора последнего канала соединен со вторым входом первого элемента ИЛИ последнего канала,, третий и чет. вертый коммутаторы последнето канала через второй элемент ИЛИ последнего канала соединены со входом регистра приоритета последнего канала, выходы регистров приоритета каналов соединены со второй группой входов блока формирования номера позиции очереди, вход блока формирования кода приоритета соединен с первым входом устройства, а управляющие входы второго и четвертого коммутаторов последнего канала соединены с соответствующим выходом второй группы выходов блока управления.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-01-25—Публикация

1976-11-09—Подача