1

Изобретение относится к области вычислительной техники и автоматики и может быть использовано при построении устройств вычитания и суммирования двух импульсных последовательностей, а также при построении импульснофазового преобразователя, основанного на принципе суммирования приращений кода.

Устройством, реализующим сложение и вычитаний импульсных последовательностей, являетоя импульсно-фазовый преобразователь Щ.

При использовании такого устройства возможны как неполное вычитание импульсов, так и слияние их при сложении что приводит к сбою устройства и появлению ложной информации на его выходе

Наиболее близким аналогом является вычислительное устройство, содержащее триггеры и элемент НЕ, причем вход элемента НЕ подключен к первой входной шине устройства, единичные входы первого и второго триггеров соединены

между собой, нулевой вход первого триггера подключен ко второй входной шине, а нулевой вход второго триггера - к нулевому выходу первого триггера Г2|.

Такое устройство реализует лишь вычитанир из текущего значения частоты ее начального значения.

Целью настоящего изобретения являет ся расширение функциональных возможностей, заключающееся в возможности сложения импульсных последовательностей.

Указанная цель достигается тем, что устройство дополнительно содержит формирователи импульсов, элементы И и ИЛИ, причем входы первого и второго формирователей импульсов подключены соответственно к первой входной шине и выходу элемента НЕ, выход второго формирователя импульсов подключен к нулевому входу третьего триггера и к первому входу первого элемента И, второй вход которого подключен к нулевому выходу второго триггера, а выход к первым входам второго и третьего элементов И, вторые входы которых подключены соответственно к первой и второй управляющим шинам, а выходы соответственно к первому входу элемента ИЛИ и единичному входу третьего триггера, нулевой выход которого соединен с первым входом четвертого элемента И, второй вход которого подключен к выходу первого формирователя импульсов и единичным вхбдам первого и второго триггеров, а выход - ко второму входу элемента ИЛИ, выход которого подключен к выходной шине устройства.

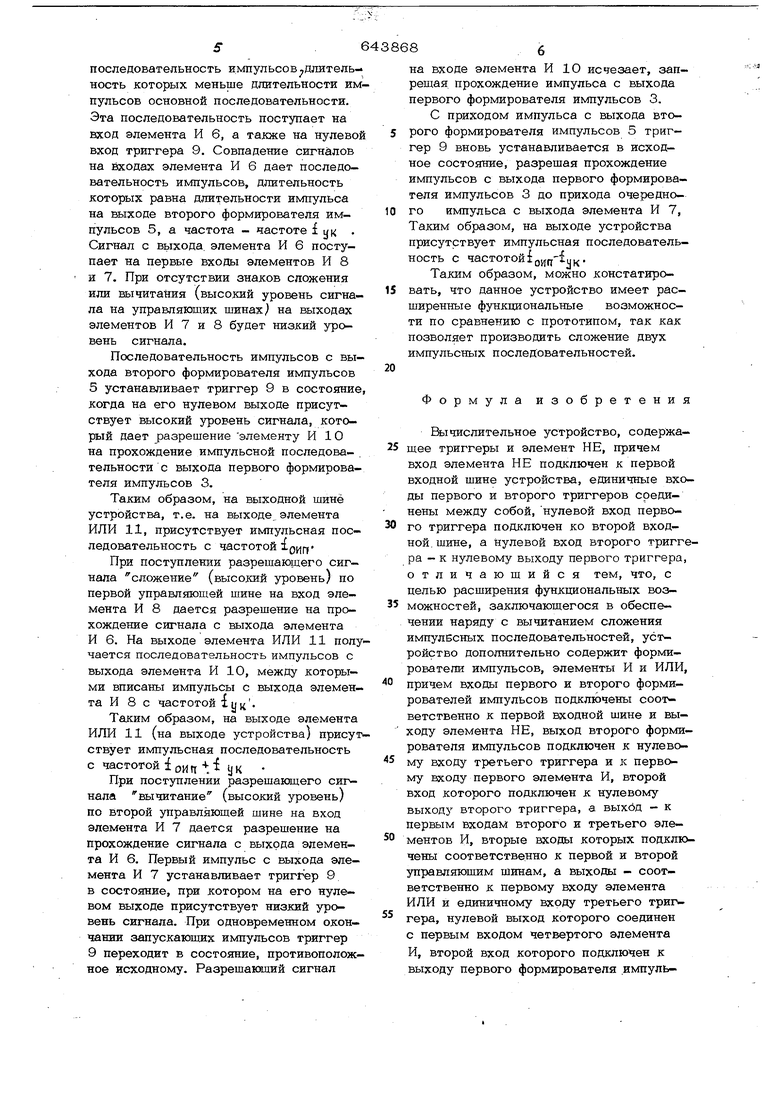

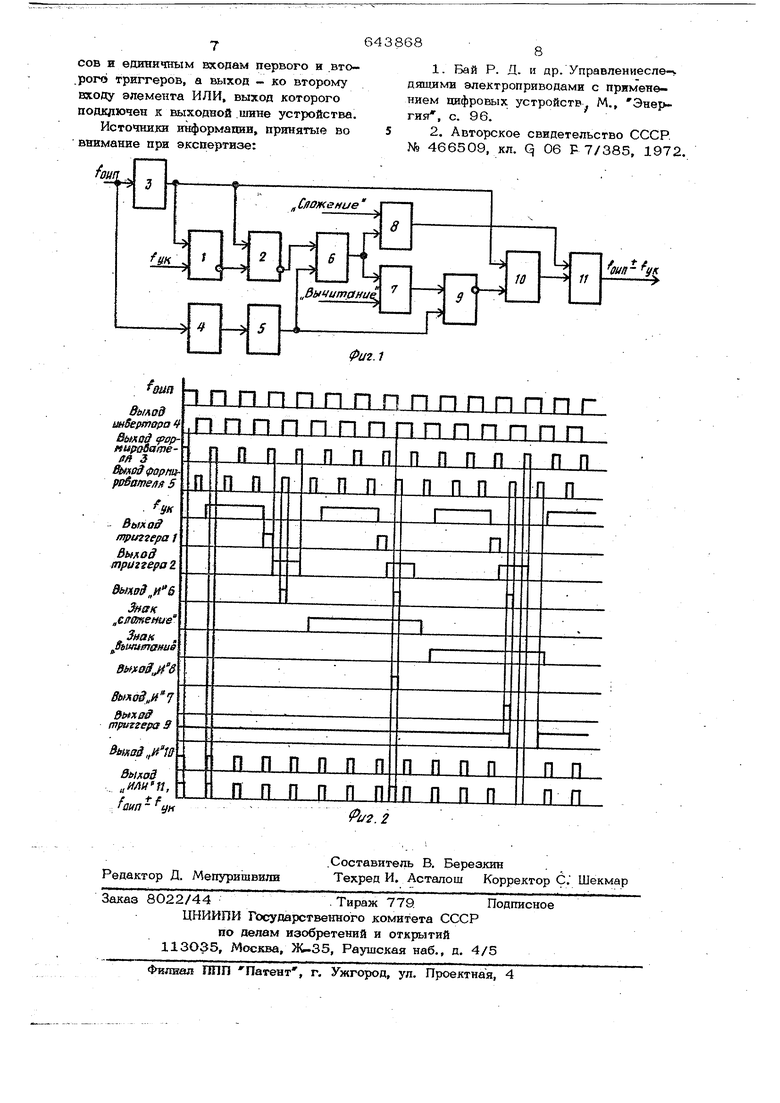

На фиг. 1 изображена функциональна схема устройства; на фиг. 2 - временная диаграмма работы устройства.

Устройство содержит первый 1. и втрой 2 триггеры, единичные входы которых соединены между собой и с выходом первого формирователя импульсов 3, вход которого связан с первой входной шиной устройства, по которой подается основная импульсная последовательность о пп со входом элемента НЕ 4, Нулевой вход первого триггера соединен со второй входной шиной устройства, по которой подается унитарный код f ц) S нулевой выход - с нулевым входом второго триггера 2. Устройство содержит также второй формирователь импульсов 5, вход которого соединен с выходом элемента НЕ 4, элемент И 6, элемент И 7, элемент И 8, триггер 9, элемент И 10 и элемент ИЛИ 11. элемента ИЛИ связан с выходной шиной устройства, на которую выдается импульсная последовательность у 1,а входы с выходом элемента И 8 и с выходом элемента И 10. Один вход элемента И 10 соединен с единичными входами первого и второго триггеров 1 и 2 и с выходом первого формирователя импульсов 3, а другой вход - с нулевым выходом триггера 9. Единичный вход триггера 9 соединен с выходом элемента И 7, а нулевой вход - с выходом второго формирователя импульсов 5 и одним входом элемента И 6, другой вход которого соединен с нулевым выходом второго триггера 2. Выход элемента И 6 соединен с первыми входами элементов И 7 и 8. Второй вход элемента И 8 соединен с первой управляющей шиной устройства, по которой подается сигнал сложение а второй

ВХОД элемента И 7 соединен со второй управляющей шиной устройства, по которой подается сигнал вычитание.

Устройство работает следующим образом. На первую входную шину устройства поступают прямоугольные периодические сигналы основной импульсной последовательности которых первым формирователем импульсов 3 формируется последовательность импульсов, длительность которых меньше длительности импульсов основной последовательности. На вторую входную шину устройства поступают такие прямоугольные периодические сигналы унитарного кода fhl, частота которых меньше частоты основной импульсной последовательнос™ ОИП- . ,

Первый импульс. частоты 1 у ( устанавливает триггер 1 так, что на его нулевом выходе появляется высокий уровень сигнала, но так как частота с выхода первого формирователя, поступающая на единичный вход этого же триггера, больше частоты мц. этот триггер успевает возвратиться в исходное состояние (низкий уровень сигнала на нулевом выходе) до прихода следуюшего импульса частоты iuK . При одновременном окончании запускающих импульсов триггер 1 переходит в состояние, противоположное исходному, т.е. на его выходе будет высокий уровень сигнала. На выходе триггера 1 появляется импульс, который устанавливает по нулевому входу триг- гер 2 в состояние, при котором на его нулевом выходе появляется высокий уровень сигнала. Однако импульсы с выхода первого формирователя импульсов 3, подаваемые на этот же триггер, снова устанавливают его в первоначальное состояние (низкий уровень сигнала на нулевом входе). С приходом следующего импульса частоты Хм| работа триггеров 1 и 2 аналогична описанному выше. Таким образом, на нулевом выходе триггера 2 присутствует последовательность импульсов, частота которых равна частоте унитарного кода и к, а длительност равна периоду следования основной импульсной последовательности ioHfr- последовательность поступает на вход элемента И 6.

Проинвертированная основная импульсная последовательность с выхода элемента НЕ 4 поступает на вход второго формирователя импульсов 5. На выходе формирователя импульсов 5 присутствует последовательность импульсов .длительность которых меньше длительности им пульсов основной последовательности. Эта последовательность поступает на вход элемента И б, а также на нулево вход триггера 9. Совпадение сигналов на входах элемента И 6 дает последовательность импульсов, длительность которых равна длительности импульса на выходе второго формирователя импульсов 5, а частота - частоте f ук . Сигнал с вьххода. элемента И 6 поступает на первые входь элементов И 8 и 7. При отсутствии знаков сложения или вычитания (высокий уровень сигнала на управляющих шинах j на выходах элементов И 7 и 8 будет низкий уровень сигнала. Последовательность импульсов с вы хода второго формирователя импульсов 5 устанавливает триггер 9 в состояние когда на его нулевом выходе присутствует высокий уровень сигнала, который дает разрешение элементу И 10 на прохождение импульсной последовательности с выхода первого формирователя импульсов 3. Таким образом, на выходной шине устройства, т.е. на выходе элемента ИЛИ 11, присутствует импульсная последовательность с частотой 0(/)г, При поступлении разрешающего сигнала сложение (высокий уровень) по первой управляющей шине на вход элемента И 8 дается разрешение на прохождение сигнала с выхода элемента И 6. На выходе элемента ИЛИ 11 пол чается последовательность импульсов с выхода элемента И 10, между которыми вписаны импульсы с выхода элемента И 8 с частотой 1 у t;. Таким образом, на выходе элемента ИЛИ 11 (на выходе устройства) прису ствует импульсная последовательность с частотой 1оип t ijK При поступлении разрешающего сигнала вычитание (высокий уровень) по второй управляющей шине на вход элемента И 7 дается разрешение на прохождение сигнала с выхода элемента И 6. Первый импульс с выхода элемента И 7 устанавливает триггер 9 в состояние, при котором на его нулевом выходе присутствует низкий уровень сигнала. При одновременном окончании запускающих импульсов триггер 9 переходит в состояние, противополож ное исходному. Разрешающий сигнал 86 на входе элемента И 10 исчезает, запрещая прохождение импульса с выхода первого формирователя импульсов 3. С приходом импульса с выхода второго формирователя импульсов 5 триггер 9 вновь устанавливается в исходное состояние, разрешая прохождение импульсов с выхода первого формирователя импульсов 3 до прихода очередного импульса с выхода элемента И 7, Таким образом, на выходе устройства присутствует импульсная последователь- ность с частотойipj pfuj. Таким образом, можно констатировать, что данное устройство имеет расширенные функциональные возможности по сравнению с прототипом, так как позволяет производить сложение двух импульсных последовательностей. Формула изобретения числительное устройство, содержа- щее триггеры и элемент НЕ, причем вход элемента НЕ подключен к первой входной шине устройства, единичные входы первого и второго триггеров соединены между собой, нулевой вход первого триггера подключен ко второй входной, шине, а Нулевой вход второго триггера - к нулевому выходу первого триггера, отличаюшийся тем, что, с пелью расширения функциональных возможностей, заключающегося в обеспечении наряду с вычитанием сложения импулБсных последовательностей, устройство дополнительно содержит формирователи импульсов, элементы И и ИЛИ, причем входы первого и второго формирователей импульсов подключены соответственно к первой входной шине и выходу элемента НЕ, выход второго формирователя импульсов подключен к нулевому входу третьего триггера и к первому входу первого элемента И, второй вход которого подключен к нулевому выходу второго триггера, а выхбд - к первым входам второго и третьего элементов И, вторые входы которых Подключены соответственно к первой и второй управляющим щинам, а выходы - соответственно к первому входу элемента ИЛИ и единичному входу третьего триггера, нулевой выход которого соединен с первым входом четвертого элемента И, второй вход которого подключен к выходу первого формирователя импульсов и единичным входам первого и вто.рого триггеров, а выход - ко второму входу элемента ИЛИ, выход которого пошщючен к выходной шине устройства. Источники информапив, принятые во внимание при экспертизе:

/Л/л

1.Бай Р. Д. и др. Управлениесле-s дяоцими электроприводами с применением цифровых устройств М., Энернгня, с. 96.

2,Авторское свидетельство СССР. № 466509, кл. q 06 F 7/385, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания и сложения импульсов | 1980 |

|

SU928629A1 |

| Способ формирования частотно-импульсных сигналов датчика перемещения и устройство для его осуществления | 1976 |

|

SU905993A1 |

| Преобразователь унитарного кода в сдвиг фазы импульсного сигнала | 1984 |

|

SU1229962A1 |

| Масштабный расширитель импульсов | 1982 |

|

SU1050104A1 |

| Устройство для контроля импульсных последовательностей | 1986 |

|

SU1338034A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| Устройство для получения суммы и разности частот двух импульсных последовательностей | 1983 |

|

SU1109764A1 |

| Устройство для поиска зон информации на магнитном носителе | 1989 |

|

SU1712961A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

Авторы

Даты

1979-01-25—Публикация

1976-11-15—Подача