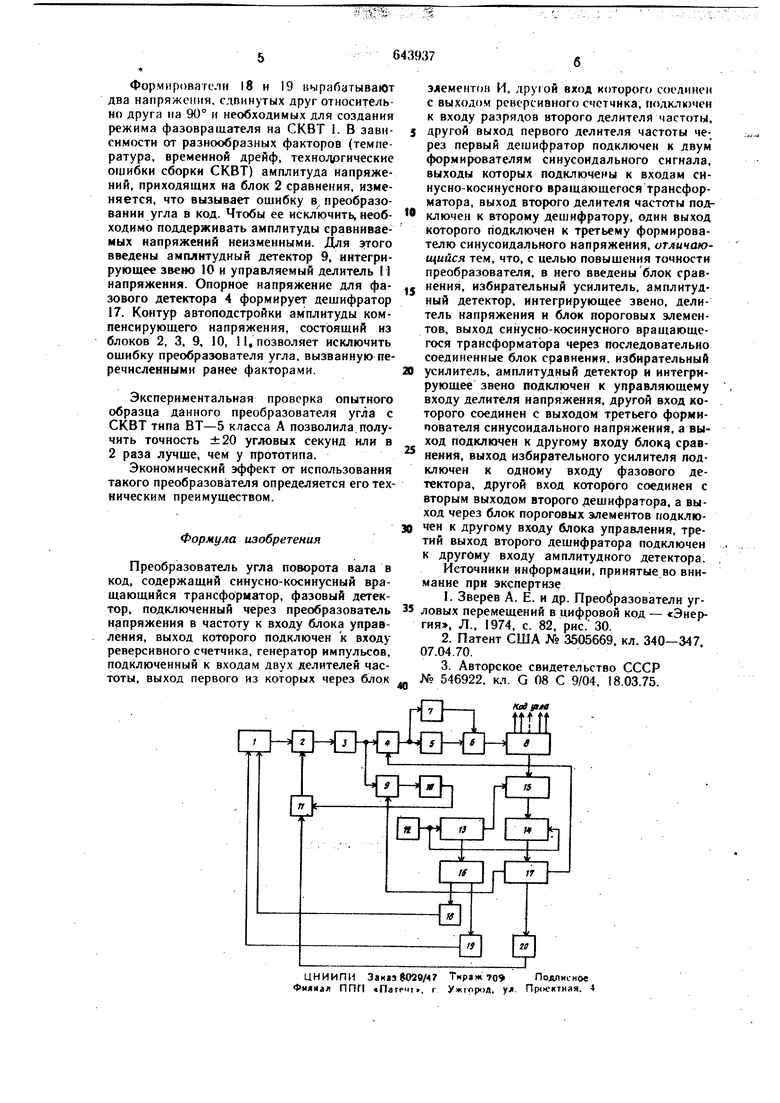

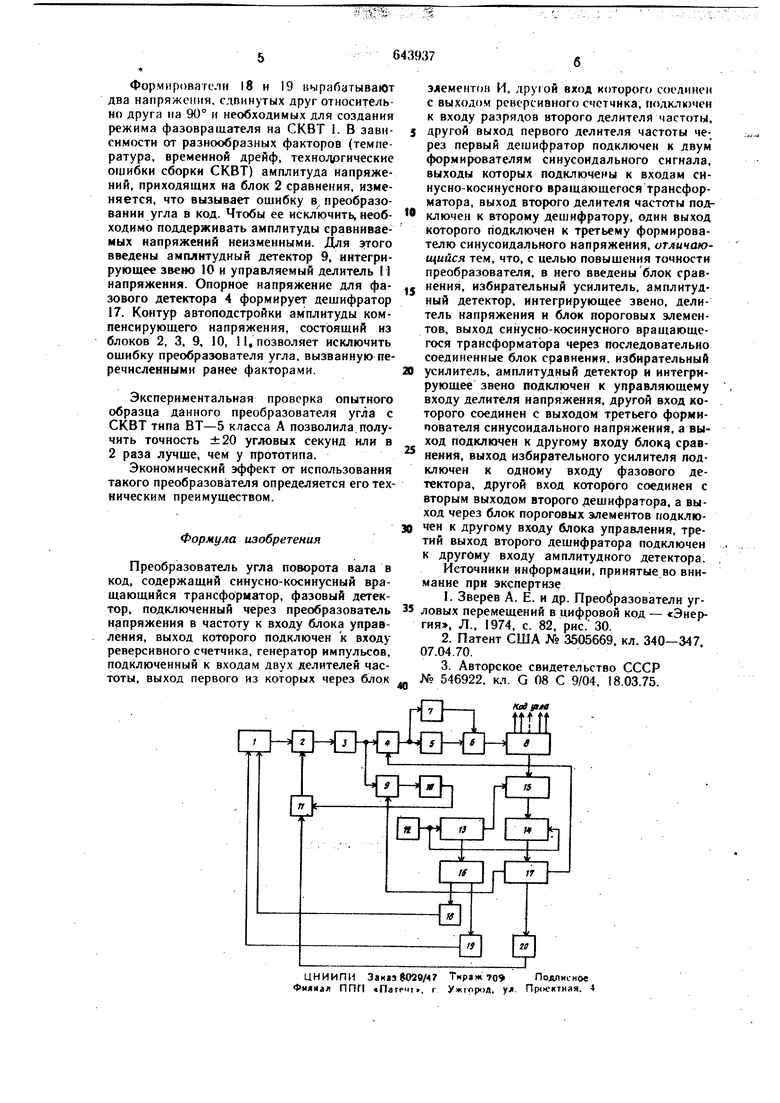

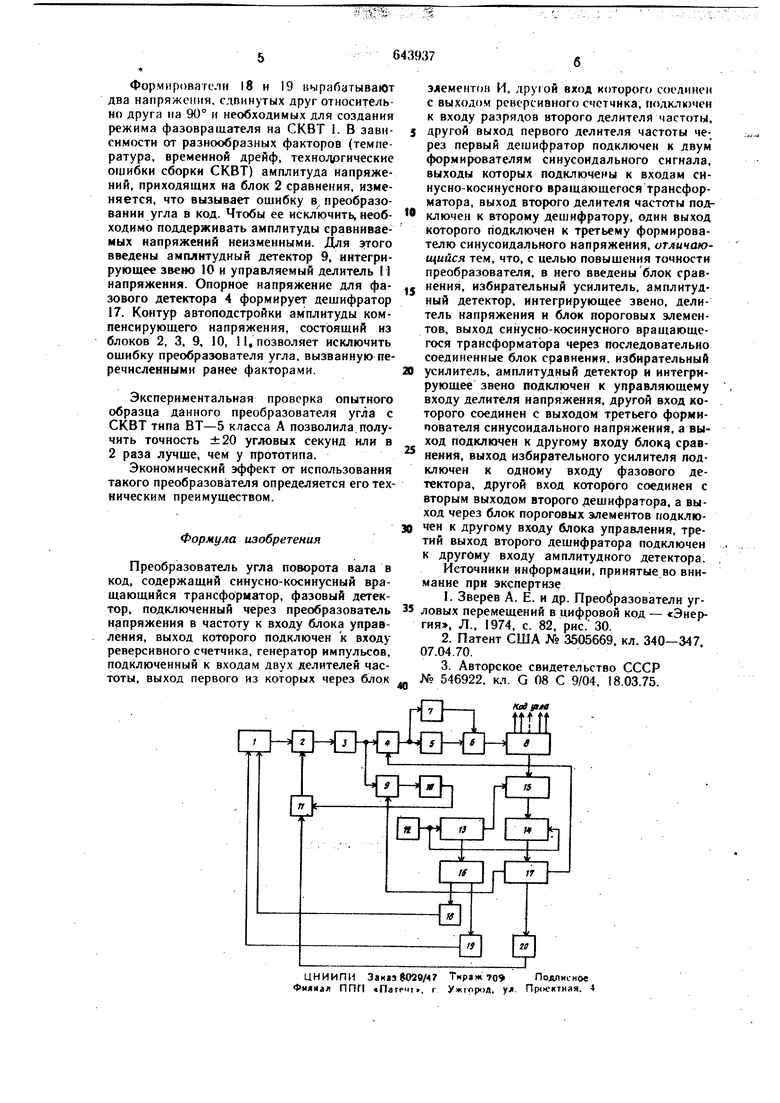

Целью изобретения является повышение точности преобразователя угла в код путем .автоматического регулирования амплитуд сравниваемых напряжений. Поотавленная цель достигается тем, что в преобразователь введены блок сравнения, избирательный усилитель, амплитудный детектор, интегрирующее звено, делитель напряжения и блок пороговых элементов, выход синусйо-косинусного вращающегося трансформатора через последовательно соединенные блок сравнения, избирательный усилитель, амплитудный детектор и интегрирующее звено подключен к управляющему входу делителя напряжения, другой вход которого соединен с выходом третьего формирователя синусоидального напряжения, а выход подключен к другому входу блока сравнения, выход избирательного усилителя подключен к одному входу фазового детектора, другой вход которого соединен с вторым выходом второго дешифратора, а выход через блок пороговых элементов подключен к другому входу блока управления, третий выход второго дещифратора подключен к другому входу амплитудного детектора. В таком преобразователе осуществляется автоматическая подстройка амплитуд информационного и компенсирующего напряжений, что повыщает точность преобразователя. Структурная схема преобразователя представлена на чертеже. Выход синусмо-косниусного вращающегося трансформатора 1 через последовательно соединенные блок 2 сравнения, избирательный усилитель 3, фазовый детектор 4 и блок 5 пороговых элементов соединен с одним входом блока 6 управления. Выход фазового детектора 4 через преобразователь 7 напряжения в частоту подключен к другому входу блока 6 управления, выход которого подключен к входу реверсивного счетчика 8. Выход избирательного усилителя 3 через последовательно соединенные амплитудный детектор &, интегрирующее звено 10 подключен к управляющему входу делителя 11 напряжения. Генератор 12 импульсов подключен к делителям 13 и 14 частоты. Выход реверсивного счетчика 8 через блок элементов И 15, другой вход которого соединен,с выходом делителя 13 частоты, подключен к входу разрядов делителя 14 частоты. Выходы разрядов делителей 13 и соответственно 14 частоты через дешифраторы 16 и соответственно 17 подключены к формирователям 18, 19 и соответственно 20 синусоидального напряжения. Выходы формирователей 18 и 19 подключены к обмоткам возбуждения СКВТ 1, а выходформирователя 20 подключен к другому входу делителя 11 напряжения, выход которого связан со вторым входом блока 2 сравнения. Второй выход аешнф ратора 17 подключен к другому входу фазового детектора 4, а третий выход к другому входу амплитудного детектора 9. СКВТ 1 преобразует угол поворота входного вала в напряжение, фазовый сдвиг которого пропорционален углу поворота входного вала. Выходное напряжение (напряжение СКВТ I) поступает в блок 2 сравнения, в котором складывается в противофазе с компенсирующим напряжением с выхода делителя 11. Из результата сложения выделяется и усиливается первая гармоника, несущая информацию как о фазовом, так и о амплитудном разбалаисе сравниваемых напряжений. Избирательный усилитель 3 в тракте фазового детектора 4 определяет постоянную времени, которая определяет динамическую характеристику преобразователя угол-код в целом. Расщирение диапазона преобразователя 7 напряжения в частоту позволяет до определенного предела скоростей изменения угла входного вала исключить динамическую ощибку. Знак и величина рассогласования по фазе между сравниваемыми напряжениями определяет режим работы, т.е. суммирование или вычитание, и частоту заполнения реверсивного счетчика 8, а по амплитуде - коэффициент передачи управляемого делителя 11 напряжения. Команды на режим работы, а также на остановку подачи импульсов от преобразователя 7 напряжения в частоту, вырабатываются блоком 5 пороговых элементов в совокупности с блоком б управления. Заполнение реверсивного сч.етчика 8 продолжается до тех пор, пока фазовый сдвиг между сравниваемыми напряжениями не будет равен 180°. По мере уменьшения фазового разбаланса снижаются частоты заполнения реверсивного счетчика 8. Чтобы, исключить колебательный режим у положения равновесия, введен блок 5 пороговых элементов, порог чувствительности которых должен быть равен половине цены младшего разряда. Изменение фазы компенсационного напряжения осуществляется по цепи,составленной из блоков 8, 15, 14, 17, 20. Число, записанное в реверсивном счетчике 8, один раз за период формируемого сигнала переписывается через блок 15 элементов И в делитель частоты 14. Команда на перенос числа вырабатывается делителем частоты 13 в момейт, когда все триггеры устанавливаются в нулевое положение. Отличие в работе делителей частоты 13 и 14 состоит в том, что записанное число в делитель 14 из реверсивного счетчика 8 эквивалентно начальной установке. Поэтому цикл делителя 14 будет смещен во времени. Этот временной сдвиг кодовых/комбинаций в делителях 13 и 14 частоты преобразуется дешифраторами 16 и 17 и формирователями 18, 19 и 20 синусоидального сигнала в фазовый сдвиг напряжений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU684578A1 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU669374A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

| Двухотсчетный преобразователь углапОВОРОТА ВАлА B КОд | 1979 |

|

SU840995A1 |

| Преобразователь угла поворота вала в код | 1978 |

|

SU771115A2 |

| Преобразователь угол-код | 1979 |

|

SU801020A1 |

| Компенсационный преобразователь угловых перемещений в код | 1975 |

|

SU546922A1 |

| Двухотчетный преобразователь углового перемещения в цифровой код | 1975 |

|

SU526932A1 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU813487A1 |

Авторы

Даты

1979-01-25—Публикация

1976-11-16—Подача