(54) УСТРОЙСТВО УПРАВЛЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАПШНЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для циклового программного управления | 1984 |

|

SU1231488A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для программного управления | 1984 |

|

SU1182488A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Многоканальное программно-временное устройство | 1985 |

|

SU1280570A1 |

| Терморегулятор для хроматографа | 1978 |

|

SU736059A1 |

| Устройство для ввода информации | 1991 |

|

SU1800452A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Устройство для циклового программного управления | 1986 |

|

SU1312527A1 |

Изобретение относится к области вычиспитепьной техники и может найти npHNfeHeHHe при проектировании высоконадежных устройств управления вычислите пьной машины с жесткой программой,

: Известно устройство управления вычисгеитепьной машины, состояпцее из бпо- ка коммутации и синхронизации, вьфабатываюшего серию упрайПяюших сигнапов блока управления командами, содержащего регистр команд, счетчика команд и допога1Ительных регистров, узла управпения операциями, содержащего дешифратор кода операций (блок операций) и вентильные схемы, образующие бпоки центрального и местного управпенйя операциями ij.

Недостатком этого устройства является низкая помехозащищенность.

При работе вычислительной машины в условиях значительных помех возможны ситуации, при которых происходит

выработка лишних управляющих сигналов, что приводит к неверному решению выполняемой задачи, в свою очередь при; водит к неправильной работе объекта регулирования или к выходу последнего из строя.

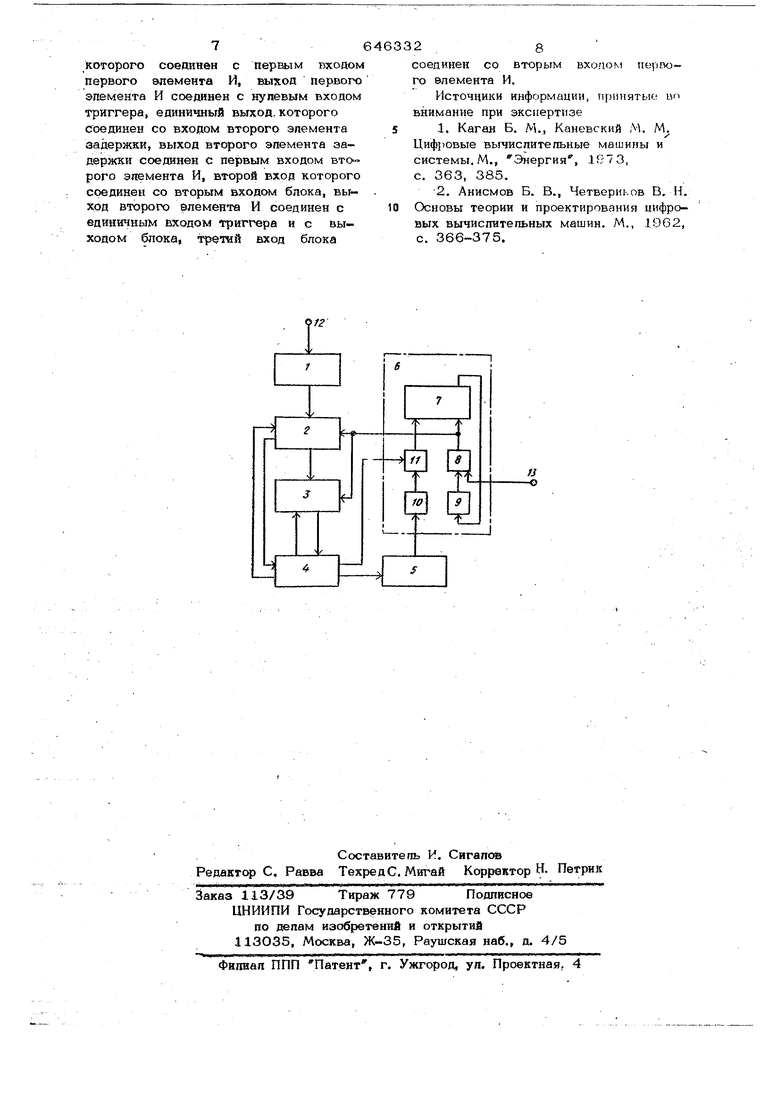

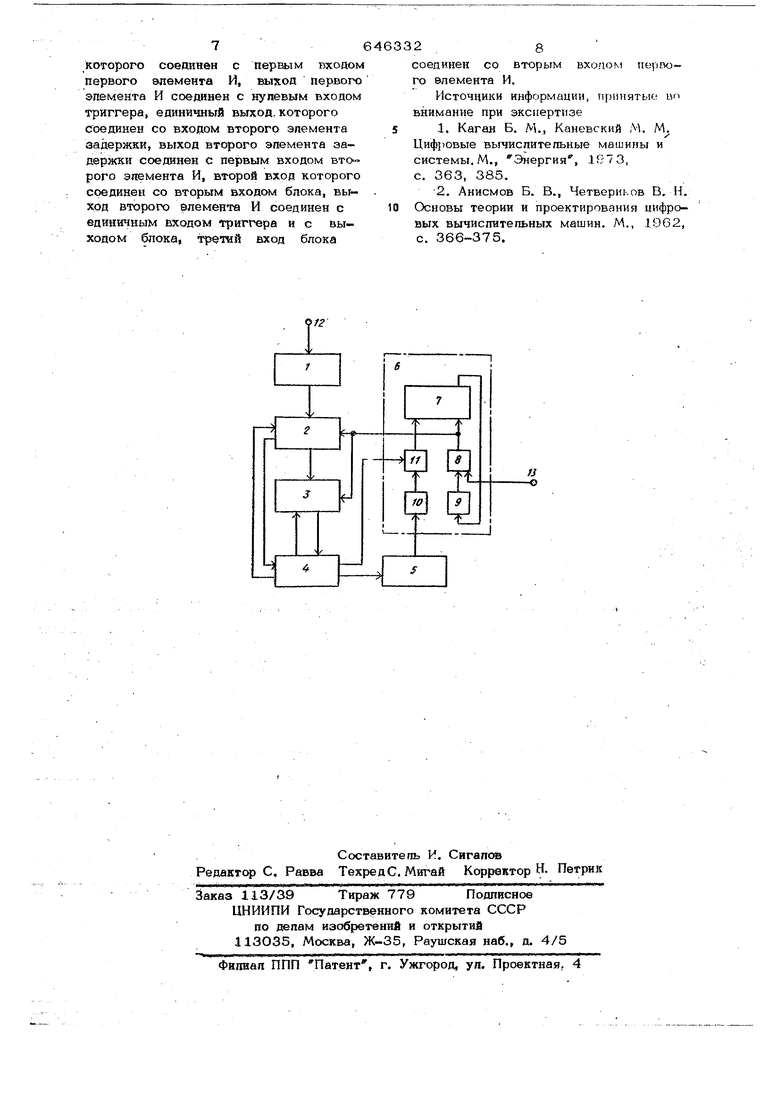

Из известных устройств управления наиболее близким по технической сущности является устройство управления, содержащее дешифратор кода операций блок ввода-вывьда, счвтшк команд и распределитель импульсов, причем первый и второй выходы дешифратора кода операций соединены соответственно с первым входом распределителя импупБсов и счёт шка ком0нд, а третий выход дешифратора кода операций соединен со всрдом блока ввода- выврдв, первый и второй выходы распределителя импульсов соединены соочъетственно с первым входом блока дешифратора кода операций и со вторым входом счетчика команд, выход счетчика команд сое3вднен со вторым входом де1иифратора («ода операций 2. Такое устройство управления обладае низкой помехозащищенностью, так как его работа зависит от воздействия импупьсных помех в канапах тактовой и цикповой частот, подаваемых на входы распредепитепя импульсов. При этом тактовая частота определя темп в ьтопнения операций вычислительной машиной, а цикЛовая - темп выполнения программы. Каждым импульсом цикловой частот происходит запуск вычислительной маши ны с начального адреса, записанного в определенную ячейку оперативной памяти. Обновление этой ячейки проио Зсодитперед концом работы программы, т. е. программа записав в ячейку начальный адрес следующей программы, останавливает вычислительную машину. Запуск вычислительной машины произiaotUJTCH импульсом цикповой частоты. При этом, если импульс цикловой частоты придет до того как машина остановнлась, то это приведет к сбою .всего вычислительного процесса. Цепью предлагаемого изобретения является повьшение помехозащищенност работы устройства. Поставленная цель достигается тем, что в устройство введены реле времени и логический блок, причем вход устройства соединен со входом реле времени, выход которого соединен со вторым входом распределителя импульсов, выход логического бло ка соединен соответственно с третьим входом распределителя импульсов и сче чика команд, выход блока ввода-вывода соединен с первым входом логического блока, второй и третий входы которого соединены соответственно со вторым входбм устройства и с четвертым выходом дешифратора кода операций. Логи ческий блок содержит триггер, первый и второй элементы И, первый и вт рой элементы задержки, причем первый вход логического блока соединен со вхо дом первого. элемента задержки, выход которого соединен с первым входом пер вого элемента И, выход первого элеS мента И соединен с нулевым входом тр гера, единичный выход которого соединен со входом второго элемента задерж ки, выход второго элемента задержки соединен с первым входом второго элемента И, второй вход которого сое24пинен со вторым входом блока, выход : торого зпемента И соединен с епиничым входом триггера и с выходом бпока, ретий вход блока соединен со вторым ходом первого элемента И. Сущность изобретения поясняется чертежом, где изображена структурная схема устройства управления вычислительной машины. Устройство содержит реле времени 1, распределитель импульсов 2, счетчик команд 3, дешифратор кода операций 4, блок ввода-вывода 5, логический блок .6, включающий в себя триггер 7, первый элемент И 8, первый элемент задержки 9, второй элемент задержки 10, второй элемент И 11. Вход реле времени 1 соединен со входом 12 устройства, который подключен к каналу тактовой частоты вычислительной машины, выход реле времени 1 соединен со входом распределителя импульсов 2. Второй вход распределителя импульсов 2 соединен с выходом дешифратора кода операций 4, а третий вход распределителя импульсов 2 соединен со входом счетчика команд 3 и выходом логического блока 6. Один выход распределителя импульсов 2 соединен со входом счетчика команд 3, а щзугой выход со входом дешифратора кода операций 4. Третий вход счетчика команд 3 соединен с первым выходом дешифратора кода операций 4, а выход счетчика команд 3 - 7;о входом дешифратора кода операций 4. Второй и третий выходы дешифратора кода операций 4 соединены соответственно со входом блока ввода-вывода 5 и с первым входом логического блока 6. Выход блока ввода-вывода 5 соединен со вторым входом логического бпока 6. Третий вход логического блока 6 соединен со входом 13 устройства, который подключен к каналу цикловой частоты вычислительной машины. Работа устройства после приведения в исходное состояние всех элементов вычислительной машины начинается с поступлени я на вход 13 устройства сигнала цикловой , который разрешает начало выполнения программы. Первый сигнал цикловой частоты., проходит через первый элемент И 8 на единичный вход триггера 7 и устанавливает его в состояние I, одновременно этот сигнал поступает на распределитель импульсов 2, разрешая 5 его работу, и на счетчик команд 3, устанавливая в нем номер начальной команды программы. Сигнал с нулевого плеча триггера 7 через первый элеiJieHT задержки 9 закрывает первый элемент И 8 и запрещает дальнейшее поступление сигналов из Начала тактовой частоты на распределитель импульсов 2 и счетчик команц 3. Первый элемент задержки 9 должен иметь время задержки не менее времени приведения в исходное состояние всех элементов и служит для задержки пропуокания первого сигнала цикловой частоты на входы распределителя импульсов 2 и счетчика команд 3 через первый элемент И 8 на время переходных процессов, связанных с установкой в исходное состояние вычислительной машины. Сигналы тактовой частоты поступают на вход .12 устройства и через реле времени 1 попадают на вход распределителя импульсов 2, работа которого разрешена первым сигналом цикловой частоты. Реле времени 1 пропускает на вход распределителя импупьсов 1 сигналы, имеющие период следования не меньше допустимого дгш данной вычислительной машины, что дает возмож ность защититься от помех в канале та товой частоты. Распределитель импульсов 2 обеспечивает синхроимпульсами счетчик команд 3 и дешифратор кода операций 4. После выполнения программы дешифратор кода операпий 4 вырабатьгоает сигн л окончания работы, который запрещает работу распределителя импульсов 1. Одновременно дешифратор кода операций 4 открывает второй элемент И 11 и запускает блок ввода-вывод 5, который вырабатьгоает сигнал, поступающий на вход логического блока 6 Этот сигнал через второй элемент задержки 10 поступает на второй элемент И 11, проходит через него и устанавливает триггер 7 в положение О после 4isro сигнал с нулевого ппеча три гера 7 через первый элемент задержки 9 поступает, на первый элемент И 8 и разрешает прохождение следующего сигнала из канала цикловой частоты. Время задержки второго элемента задержки 10 должно быть не меньше времени окончания работы распредепителя импульсов 2 и блока ввода-вывода 5 после выработки блоком операций 4 32 сигнала окончания выполнения программы. Использование в устройстве реле времени и логического блока, содержащего триггер, первый и второй элементы И и первьй и второй элементы задержки, позволяет защитить каналы тактопой и цикловой частоты соответственно от воздействия помех в этих каналах, так как сигналы помех в канале тактовой частоты нё прйнбдят к наруиГё Шю временной диаграммы взаимодействия устройств вычислительной машины, а помеки в канале цикловой частоты не приводят к перезапуску программы до окончания ее выполнения. Формула изобретения 1. Устройство управления вычислительной машины, содержащее дешифратор кода операций, блок ввода-вывода, счетчик команд и распределитель импульсов, причем первый и второй выходы дешифратора кода операций соединены соответственно с первым входом распределителя импульсов и счетчика команд, а третий выход дешифратора кода операций соединен со входом блока ввода-вывода, первый и второй выходы распределителя импульсов соединены соответственно с первым входом деаифратора кода операций и со вторым входом счетчика команд, выход счетчика команд соединен со вторыг входом дешифратора кода операций, о т л и ч а ющ е е с я тем, что, с целью повьпиения помехозащищенности в устройство введены реле времени и логический блок, причем первый вход устройства соединен со входом реле времени, выход которого соединен со вторым входом распределителя импульсов,, выход логического блока соединен соответственно с третьим входом распределителя импульсов и счетчика команд, выход блока ввода-вывода соединен с первым входом логического блока, второй и третий Bxozibr которого соединены соответственно со вторым входоК1 устройства и с четвертым выходом деигифратора кода операций. 2. Устройство по п. 1, отличающееся тем, что логический блок содержит триггер, первый и второй элементы И, первый и второй элементы задержки, причем первый вход логического блока соединен со входом первого элемента задержки, выход 7 которого соеоннен с первым входом первого элемента И, выход первого эпемента И соединен с нулевым входом триггера, единичный выход, которого соединен со входом второго эпемента задержки, выход второго эпемента задержки соединен с первым входом вта рого эпемента И, второй вход которого соединен со вторым входом блока, вььход второго елемента И соединен с единичным входом триггера и с выходом блока, третий вход блока 2 соединен со вторым входом перво- го елемента И. Источники информацииt принятые w внимание при экспертизе 1. Каган Б. М., Каневский М. М. Циф1)овые вычислительные машины и системы. М., Энергия , 1G73, с. 363, 385. 2. Анисмов Б. В., Четвериков В, Н. Основы теории и проектирования пифровых вычислитепьных машин. М., 1062, с. 366-375.

Авторы

Даты

1979-02-05—Публикация

1975-06-02—Подача