Цель изобретения - расширение функциональных возможностей за счет формирования команд управления с произвольной длительностью и моментом начала в фиксированных микротактах. Устройство содержит блок 1 памяти, 2 адреса, первый 3 и второй 4 регистры, первый 5 и второй 6 коммутаторы, блок 7 коммутации, группу 8( 8ff первых счетчиков импульсов, второй счетчик 9 импульсов, дешифратор 10, первый 11 и второй 12 RC-триггеры, генератор 13 импульсов, второй 15, третий 14, четвертый 18,

1

Изобретение отно.сится к промышленной автоматике и вычислительной технике и может найти применение при организации мультипрограммной работы вычислительных машин и сие- тем, в программируемых контролле-, pax, АСУ технологическим1 процессами, на станках с числовым программным управлением.

Целью изобретения является расши- рение функщюнальных возможностей ,за счет формирования команд управления с произвольной длительностью и моментом начала в фиксированных микротактах,

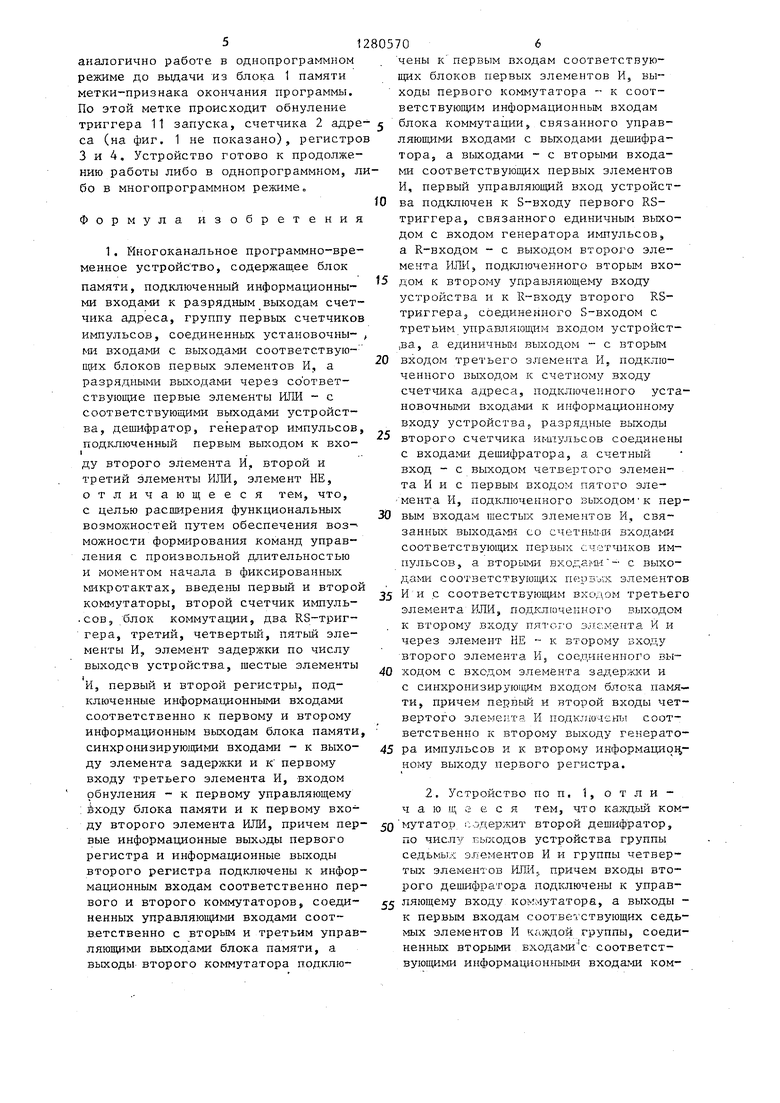

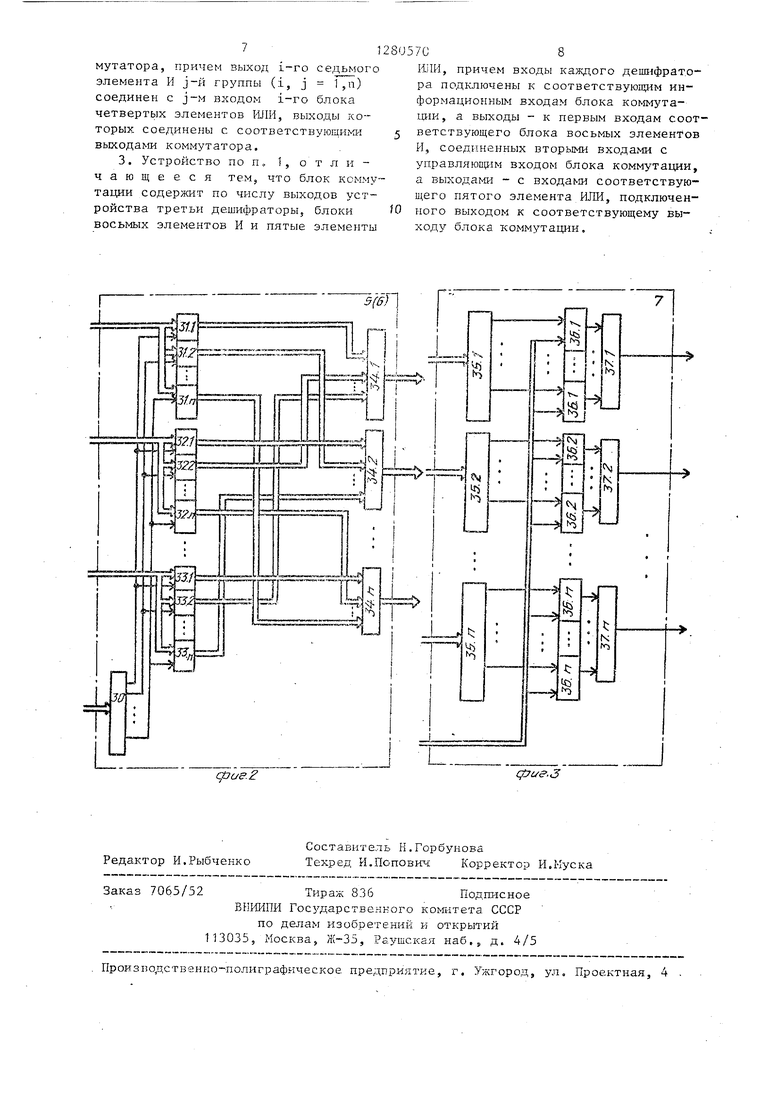

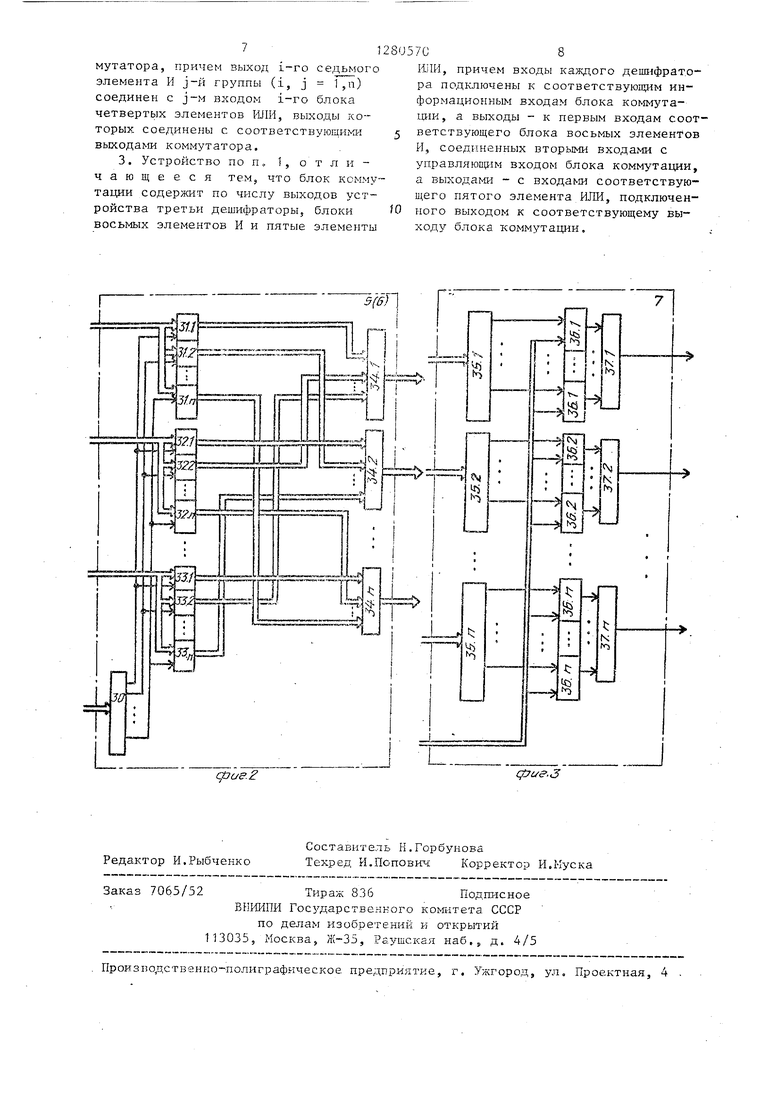

На фиг. 1 представлена функциональная схема устройстваJ на фиг.2 - функциональная схема первого (второго) коммутатора на фиг. 3 - функциональная схема блока коммутации.

Устройство (фиг, 1) содержит блок 1 памяти, счетчик 2 адреса, первый регистр 3, второй регистр 4, первый и второй коммутаторы 5 и 6, блок 7 коммутации, группу первых счетчиков 8,-8 импульсов (где п - количество выходов устройства), второй счетчик 9 имтульсов, дешифратор 10, первый RS-триггер 11, второй КЗ-триггер 12, генератор 13 импульсов, третий элемент И 14, второй элемент И 15, блоки первых элементов И 16,-16, шестые элементы И 17(-17р, четвертый элемент И 18, пятьй элемент И 19, второй элемент ИЛИ 20, третий элемен

пятый 19 элементы И, блоки , и первых и 17j-17f, шестых элементов И, блок 22, -22 первых элементов ИЛИ второй 20 и третий 21 элементы ИЛИ, элемент 23 задержки, элемент НЕ 24. Введение первого и второго коммутаторов, второго счетчика импульсов, блока коммутации, двух RS-триггеров, третьего, четвертого и пятого элементов И, по числу выходов устройства шестых элементов И, первого и второго регистров с соответствующими связями позволяет достичь поставленную цель. 2 з.п, ф-лы, 3 ил.

5

0 -5

0

5

35

30

ИЛИ 21, первые элементы ИЖ 22,-22„, элемент 23 задержки, элемент НЕ 24, информационный вход 25 устройства, первый 26, второй 27 и третий 28 уп- равляюш,ие входы устройства,выходы 29,-29f, устройства.

Первый (второй) коммутатор 5 (6) содержит второй дешифратор 30, п групп седьмых элементов И 31, 33;,-33f,, четвертые элементы ИТШ , (фиг. 2) ,

Блок 7 коммутации (фиг. 3) содержит третьи дешифраторы 35,--35 блоки восьмых элементов И 36, -Зб,, пятые элементы ИЛИ 37, -37 ,

В исходном состоянии элементы памяти устройства находятся в исходном (нулевом) состоянии.

Многоканальное программно-временное устройство может работать в одно- программном и MHoronporpat iMHOM режимах .

Oднoпpoгpaм пiьш режим.

дрес выполняемой программы с входа 25 устройства заносится в счетчик 2 адреса, С входа 26 на S-вход RS- триггера 11 (запуска) поступает импульс, который переводит триггер 11 в единичное состояние. Этим разрешается формирова.ние с выходов генератора 13 тактовых импульсов. Так как счетчики 8, -8,, находятся в нулевом .состоянии, то на выходах элементов ИЛИ 22,-22fi имеются сигналы логического нуля. Эти сигналы, проходя через элементы ИЛИ 21 и НЕ 24, разрешают

W

15

20

прохождение через элемент И 15 тактового импульса с выхода генератора 13, который поступает на синхронизирующий вход блока 1 памяти и разрешает из него выборку информации по адресу, записанному в счетчике 2 адреса. Этот же импульс через злемент 23 задержки поступает на вход элемента И 14, который закрыт нулевым потенциалом с единичного выхода триггера 12 режима. Увеличения адреса на счетчике 2 не происходит. Информация, выбранная из блока 1 памяти, заносится в регистры 3 и 4.

После считывания информации из блока 1 памяти по метке-признаку наличия импульсной последовательности (второй информационный выход) регистра 3 открывается злемент И 18 и импульсы с выхода генератора 13 с частотой, определяемой длительностью микротакта, заполняют счетчик 9. Последний совместно с дешифратором 10 образует распределитель импульсов. Сигналы с выходов дешифратора 10 оп- 25 ределяют последовательность (номера) микротактов и производят опрос по- лей регистра 3 через коммутатор 5 на блоке 7 коммутации, Б поляк регистра 3 хранятся коды начала им- 30 пульсов программы управления. При совпадении кода микротакта с выхода дешифратора 10 с кодом начала импульса по определенному каналу на соответствующем выходе злементов ШШ 37, -37 блока 7 коммутации (фиг. 3) появляется сигнал начала импульса. Сигналы начала импульсов в определенном микротакте с выхода блока 7 коммутации открывают элементы И 16| (i 17),-, через которые из полей регистра 4 через коммутатор 6 переписываются в счетчики 8,-8 коды длин импульсов, начавшихся в данном микротакте.-В результате на соответствующих выходах (каналах) 29, -29р устройства появляются выходные сигналы.

Изменение нулевого состояния определенных счетчиков 8,-8ц приводит к появлению сигналов на соответствующих выходах злементов ИЛИ 22(-22, которые поступают на элементы Ш1И21. Сигнал о начале вьшолнения программы управления поступает на злемент И 19 и одновременно запрещает через элемент НЕ 24 формирование очередной импульсной последовательности. С началом выполнения программы открыва40

50

55

45

5

5

0

5 0

0

ется элемент И 19 и на счетные (вычитающие) входы счетчиков 8(-8 поступают импульсы с генератора 13, которые изменяют состояние кодов соответствующих счетчиков по мере из- менения номера микротакта. Выходной сигнал в канал 29j устройства (i 1 ,п) вьщается до обнуления соответствующего счетчика. После обнуления счетчиков 8(-8р сигнал логического нуля на выходе элемента ИЛИ 21 через злемент НЕ 24 и элемент И 15 разрешает считывание информации из блока 1 памяти по адресу, код которого определяется содержимым счетчика 2, В данном случае считывается информация по предьщущему адресу, и программа вьщачи временной импульсной последовательности повторяется аналогично описанному.

Первый 5 и второй 6 коммутаторы осуществляют перестро ение (фиг.2) кодов полей регистров 3 и 4. Такое оперативное использование кодов одних полей с последующим их использованием для других каналов позволяет уменьшить объем блока 1 памяти и, следовательно, увеличить функциональную надежность устройства.

При необходимости закончить выдачу импульсов управления с входа 27 через злемент ИЛИ 20 на R-вход RS- триг гера 1 1 (запуска) поступает сигнал, который запрещает выдачу тактовых импульсов с выходов генератора 13 (цепи обнуления счетчика 2 адре- са, регистров 3 и 4, а также счетчика 9 не показаны), На этом работа устройства в однопрограммном режиме заканчивается.

Многопрограммный режим. Как и в однопрограммном режиме, работа устройства начинается с пода- чи на вход 25 начального адреса программы. Триггер 12 (режима) путем подачи импульса с входа 28 устанавливается в единичное состояние, с входа 26 устройства импульс запуска переводит RS-триггер 11 в единичное состояние. Генератор 13 выдает импульс, ко- торый через элемент И 15 производит выборку информации из блока 1 памяти по адресу, хранимому в счетчике 2. Одновременно с выборкой информации этот тактовый импульс через элемент 23 задержки и элемент И 14 увеличивает содержимое счетчика 2 адреса на единицу. Далее устройство работает .

аналогично работе в однопрограммном режиме до выдачи из блока 1 памяти метки-признака окончания программьи По этой метке происходит обнуление триггера 11 запуска, счетчика 2 адре- / са (на фиг. 1 не показано), регистров 3 и 4, Устройство готово к продолжению работы либо в однопрограммном, либо в многопрограммном режиме

Формула изобретения

1. Многоканальное программно-временное устройство, содержащее блок

памяти, подключенный информационными входами к разрядным выходам счетчика адреса, группу первых счетчиков импульсов, соединенных установочны- ми входами с выходами соответствуюuijix блоков первых элементов И, а разрядныьш выходами через со ответ- ствугощие первые элементы ИЛИ - с соответствуюпщми выходами устройства, дешифратор, генератор импульсов, подключенный первым выходом к входу второго элемента И, второй и третий элементы ИЛИ, элемент НЕ, отличающееся тем, что, с целью расширения функциональных возмолшостей путем обеспечения возможности формирования команд управления с произвольной длительностью и моментом начала в фиксированных NaiKpOTaKTax, введены первый и второй коммутаторы, второй счетчик и шyль- .сов, блок коммутации, два RS-триг- гера, третий, четвертьш, пятый элементы И, элемент задержки по числу выходов устройства, шестые элементы

,,

И, первый и второй регистры, подключенные информационными входами соответственно к первому и второму информационным выходам блока памяти, синхронизирующими входами - к выходу элемента задержки и к первому входу третьего элемента И, входом обнуления - к первому управляющему

; йходу блока памяти и к первому входу второго элемента ИХШ, причем первые информационные выходы первого регистра и информационные выходы второго регистра подключены к информационным входам соответственно первого и второго коммутаторов, соединенных управляющими входами соот в.етственно с вторым и третьим управляющими выходами блока памяти, а вьсходы второго коммутатора подклю/0

25

чены к первым входам соответствующих блоков первых элементов И, выходы первого коммутатора -- к соответствующим информационным входам блока коммутации, связанного з прав- ляющими входами с выходами дешифратора, а выходами - с вторыми входами соответствующих первых элементов И, первый управляющий вход устройст- 0 ва подключен к S-входу первого RS- триггера, связанного единичным выходом с входом генератора импульсов, а R-входом - с выходом второго элемента ИЛИ, подключенного вторым вхоt5 дом к второму управляющему входу устройства и к К входу второго RS- триггера, соединенного S-входом с третьим управляющим входом устройства, а единичны - выходом - с вторым ВХО7ДОМ третьего элемента И, подключенного выходом к счетному входу счетчика адреса, подключенного установочными входами к информационному входу устройстваJ разрядные выходы второго счетчика импульсов соединены с входами дешифратора, а счетный вход - с выходом четвертого элемента И и с первым входом пятого эле- мента И, подключенного вькодом к пер30 вым входам шестых элементов И, связанных выходами со счетньада входами соответствующих первых счетчиков импульсов, а вторыми Bxo ajfl-i. - с выходами соответствующих первь-х элементов

35 И и с соответствующим входом третьего

элемента ИЛИ, подключенного выходом . к второму входу пятог о э.иемеита И и через элемент НЕ - к второму входу второго элемента И, соединенного вы40 ходом с входом элемента задержки и с синхронизирую1.цим входом блока памяти, причем первый и второй входы четвертого элеме5.та И подключены соответственно к второму выходу генерато45 ра импульсов и к второму информацио - ному выходу первого регистра.

2. Устройство по п, 1, о т л и - ч а ю щ ч; е с я тем, что каждый ком50 ГУтатор :;одержит второй дешифратор, по числу выходов устройства группы седьмых элементов И и группы четвертых элементов ИЛИ. причем входы второго дешифратора подхшючены к управ55 ляющему входу коммутатора, а выходы - к первым входам соответствующих седьмых элементов PI каждой группы, соединенных вторыми входами с соответствующими информационны1«{ входат-ш коммутатора, причем выход i-ro седьмого элемента И j-й группы (i, j f ,11) соединен с j-м входом i-ro блока четвертых элементов ШШ, выходы которых соединены с соответствующими выxoдa ш коммутатора,

3. Устройство по По 1, отличающееся тем, что блок коммутации содержит по числу выходов устройства третьи дешифраторы, блоки восьмых элементов И и пятые элементы

ШШ, причем входы каждого де1Ш1фрат.о- ра подключены к соответствующим информационным входам блока коммута- Ш1и, а выходы - к первым входам соответствующего блока восьмых элементов И, соединенных вторыми входами с управляюпц-iM входом блока коммутации, а выходами - с входами соответствующего пятого элемента ИЛИ, подключенного выходом к соответствующему выходу блока коммутации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1986 |

|

SU1405105A1 |

| Многоканальное устройство для программного управления технологическими процессами | 1986 |

|

SU1361509A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1986 |

|

SU1372600A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| Устройство микропрограммного управления | 1981 |

|

SU960815A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

Изобретение относится к промышленной автоматике и вычислительной технике и может найти применение при организации мультипрограммной работы вычислительных машин и систем в программируемых контроллерах, АСУ технологическими процессами, на станках с числовым программным управлением. 25 (Л

qucjff.2

.-

фие.З

Редактор И.Рыбченко

Составитель Н.Горбунова

Техред И.Поповкч Корректор И.Муска

Заказ 7065/52Тираж 836Подписное

ВНИИПЙ Государственного ком-итета СССР

по делам изобретений к открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Произ1ю,цственно-полиграфическое предприяо:ие, г. Ужгород, ул. Проектная, 4

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Многоканальное программно-временное устройство | 1982 |

|

SU1057926A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-12-30—Публикация

1985-04-15—Подача