(54) ИНВЕРТОР НА МДП - ТРАНЗИСТОРАХ

| название | год | авторы | номер документа |

|---|---|---|---|

| МДП-инвертор | 1990 |

|

SU1780184A1 |

| МДП-инвертор | 1989 |

|

SU1629986A1 |

| ИНТЕГРАЛЬНЫЙ ВЫХОДНОЙ МДП-ИНВЕРТОР | 1992 |

|

RU2012100C1 |

| Формирователь импульсов | 1981 |

|

SU991507A1 |

| Преобразователь уровней | 1988 |

|

SU1539991A1 |

| Инвертор на МДП-транзисторах | 1982 |

|

SU1128388A1 |

| МДП-инвертор | 1991 |

|

SU1803972A1 |

| Динамический инвертор на МДП-транзисторах | 1982 |

|

SU1080210A1 |

| ГЕНЕРАТОР ТЕСТОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2034399C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

Изобретение относится к автоматике и вычислительной технике, может быть использовано, в частности, в мощных выходных каскадах логических устройств. Известен инвертор на МДП-транзисторах-( бутстрепный каскад ) , содержащий три транзистора и ускоря ющий конденсатор l . Его недостатком является большая потребляемая статическая мощность, обусловленная протеканием большого тока в. цепи информационного и наг.рузочного транзисторов. Наиболее близок к предлагаемому инвертор на МДП-транзисторах и конденсаторе, в котором первый вывод конденсатора соединен, с истоком Пер вого транзистора, сток и затвор которого подключены к шине питания, и с затвором второго транзистора, исток .которого соединен со стоком, третьего и с затвором четвертого транзисторов, исток четвертого тран зистора, своим стоком подключенного к шине питания,соединен со стоком пятого транзистора.и с выходной шиной, затворы и истоки первого и пятого транзисторов соединены со вход ной клеммой и с общей шиной соответ- ственно 2j. Недостаток этого устройства в низком выходном уровне логической единицы и в малом быстродействии, обусловленном относительно низким уровнем напряжения, действующего на затворе четвертого транзистора, что приводит к малой скорости заряда выходной шины. Цель изобретения - повышение выходного уровня логической единицы и быстродействия - достигается тем, что в инверторе на МДП-.транзисторах, содержащем пять транзисторов и конденсатор, первый вывод которого соединен с истоком первого транзистрра/ сток и затвор которого подключены к шине питания , и с затвором второго транзистора, исток которого соединен со стоком третьего и с затвором четвертого транзисторов, исток четвертого транзистора, своим стоком подключенного к шинам питания, сое динен со стоком пятого транзистора и с выходной шиной, затворы и истоки первого и пятого транзисторов соединены со входной клеммой и с общей шиной соответственно, сток второго транзистора соединен с его затвором.

второй вывод конденсатора - с выодной шиной.

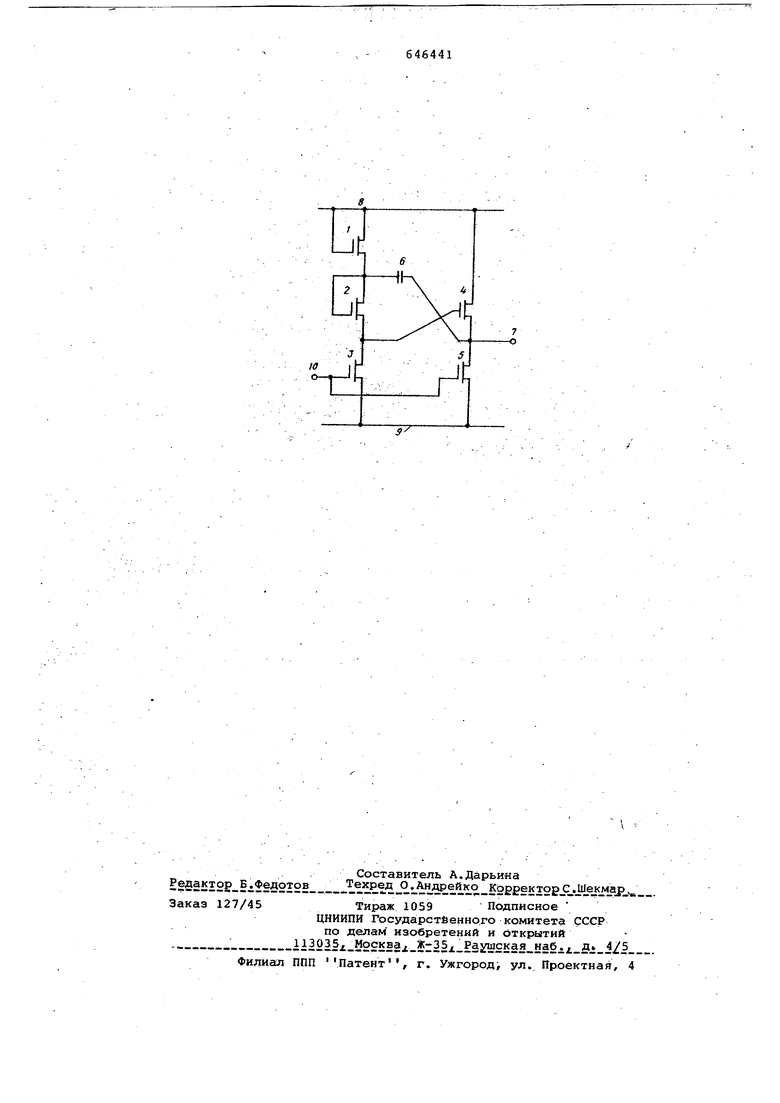

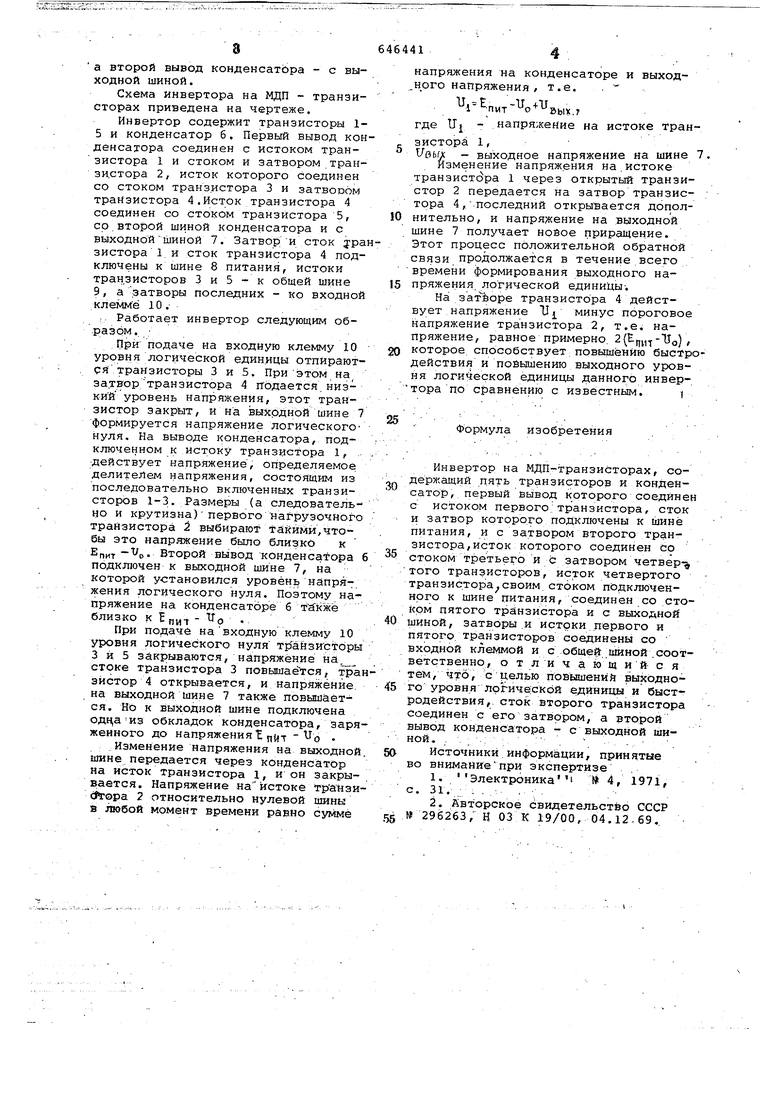

Схема инвертора на 2ВДП - транзиторах приведена на чертеже.

Инвертор содержит транзисторы 15 и конденсатор 6. Первый вывод коненсатора соединен с истоком транзистора 1 и стоком и затвором .транзистора 2, исток которого соединен со стоком транзистора 3 и затвооом транзистора 4.Исток транзистора 4 соединен со стоком транзистора 5, со второй шиной конденсатора и с выходной шиной 7. ЗатворИ сток jpaHзистора 1 и сток транзистора 4 подключены к шине 8 питания, истоки транзисторов 3 и 5 - к общей шине 9, а затворы последних - ко входной клемме 10.. Работает инвертор следующим образом.

При подаче на входную клемму 10 уровня логической единицы отпираются, транзисторы 3 и 5. ПриЭТОМ на/ за.твор транзистора 4 подается, низкий уровень напряжения, этот транзистор закрыт, и на выходной шине 7 формируется напряжение логического- нуля. На выводе конденсатора, под- , ключенном к истоку транзисггора 1, . , действует напряжение , определяемое делителем напряжения, состоящим из последовательно включенных транзисторов 1-3, Размеры (а следовательно и крутизна) первого нагрузочного транзистора i выбирают акйми,чтобы это напряжение было близко к ЕПИТ о- Второй вьзвод конденсатора 6 подключен к выходной шине 7, на которой установился уровень напряжения логического нуля. Поэтому напряжение на конденсаторе 6 близко к Епит о

При подаче навходную клемму 10 уровня логического нуля транзисторы 3 и 5 закрываются, напряжение на стоке транзистора 3 повышается, транэйстор 4 открывается, и напряжение, на выходной шине 7 также повыша.ётся. Но к выходной шине подключена обкладок конденсатора, заряженного до напряжения пит о

Изменение напряжения на выходной, шине передается через конденсатор на исток транзистора 1, и он закрывается. Напряжение наистоке транзисйгора 2 относительно нулевой шины в ойобой момент времени равно сумме

напряжения на конденсаторе и выход нрго напряжения, т.е. .

Г ;ПИТ- О УВЫ..Г где Uj - напряжение на истоке транзистора 1, 1/0бО( - выходное напряжение на шине 7.

Изменение напряж.ения на.истоке транзистора 1 через открытый транзистор 2 передается на затвор транзистора 4 ,,.последний открывается дополнительно, и напряжение на выходной шине 7 получает новое приращение. Этот процесс положительной обратной связи продолжается в течение всего . времени формирования выходного напряжения, логической единицы-.

На затЬоре транзистора 4 действует напряжение 1} j минус пороговое напряжение транзистора 2, т.е напряжение, равное примерно. 2(E.|,j,-Uo) ,

которое способствует; повышению быстродействия и повышению выходного уровня логической единицы данного инвертора по сравнению с известным. j

Формула изобретения

Инвертор на МДП-транзисторах, содёри :ащий пять транзисторов и конденсатор, первый вывод которого соединен с истоко.м первого.транзистора, сток и затвор которого подключены к шине питания, и с затвором второго транзистора, исток которого соединен со

стоком третьего и с затвором четвертого транзисторов, исток четвертого транзистора своим, стоком подключенного к шине питания, соединен со стоком пятого транзистора и с выходной

шиной, затворы .и истоки первого и пятого транзисторов соединены со входной клеммой и с общей.шиной.соответственно, о т л И ч а ю щ ий- с я тем, что, сцелью повышения выходного уровня лргиче:ск6й единицы и быстродействия, сток второго транзистора соединен с его затвором, а второй вывод конденсатора - с выходной шиной. .. :;:. . -..

Источники информации, принятые во вниманиепри экспертизе

Авторы

Даты

1979-02-05—Публикация

1976-12-03—Подача