оо о ю

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Логический элемент или-не- на мдптранзисторах | 1977 |

|

SU692089A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Динамический регистр сдвига | 1977 |

|

SU739655A1 |

| Инвертор на мдп-транзисторах | 1976 |

|

SU646441A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Логический элемент на мдп-транзисторах | 1977 |

|

SU664297A1 |

| Логический элемент на МДП-транзисторах | 1982 |

|

SU1026315A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

ДИНАМИЧЕСКИЙ ИНВЕРТОР НА МДП-ТРАНЗИСТОРАХ, содержащий управляющий транзистор, исток которого подключен к шине нулевого .потенциала, затвор является информационньм входом инвертора, сток соединен с истоком первого нагрузочного тран- . зистора и является выходом инвертора, сток первого нагрузочного транзистора подключен к истоку и затвору второго нагрузочного транзистора, сток которого подключен к шине питания, отличающийся тем, что, с целью повьпиения быстродействия инвертора, в него введен транзистор связи, сток которого являет- :ся тактовым входом инвертора, исток подключен к затвору первого нагрузочного транзистора, а затвор соединен с шиной питания.i

I

Изобретение отьюсится к вычислительной технике и может быть использовано для создания запоминающих устройств (ЗУ) на МДП-транзисторах.

В современных быстродействунлцих .статических ЗУПВ с микромощным режимом хранения информации в качеств нагрузочных элементов в формирователях различных сигналов и других периферийных каскадах применяются последовательно включенные объединеный и обогащенный МДП-транзисторы

Ги.

Наиболее близок к предлагаемому динамический инвертор, содержащий управляющий транзистор, исток которого подключен к шине нулевого потенциала, затвор является входом инвертора, сток соединен с истоком первого нагрузочного транзистора и является выходом динамического инвертора, затвор первого нагрузочного транзистора является тактовым входом, сток подключен к истоку и затвору второго нагрузочного транзистора, работающего в режиме объединения, сток которого подключен к шине питания 2J.

Недостатком данного инвертора являются потери уровня логической единицы и низкое быстродействие при передаче сигнала от стока к истоку первого нагрузочного транзистора, работающего в режиме обогащения.

Цель изобретения - повышение быстродействия динамического инвертора на МДП-транзисторах.

Указанная цель достигается тем, что в динамический инвертор на МДПтранзисторах, содержащий управляющий транзистор, исток которого подключен к шине нулевого потенциала, затвор является информационным входом инвертора, сток соединен с истоником первого нагрузочного транзистора и является выходом инвертора, сток первого нагрузочного транзистора подключен к истоку и затвору второго .нагрузочного транзистора, сток которого подключен к шине питания, введен транзистор связи, сток которого является тактовым входом инвертора, исток подключен к затвору первого нагрузочного транзистора, а затвор соединен с шинОй питания.

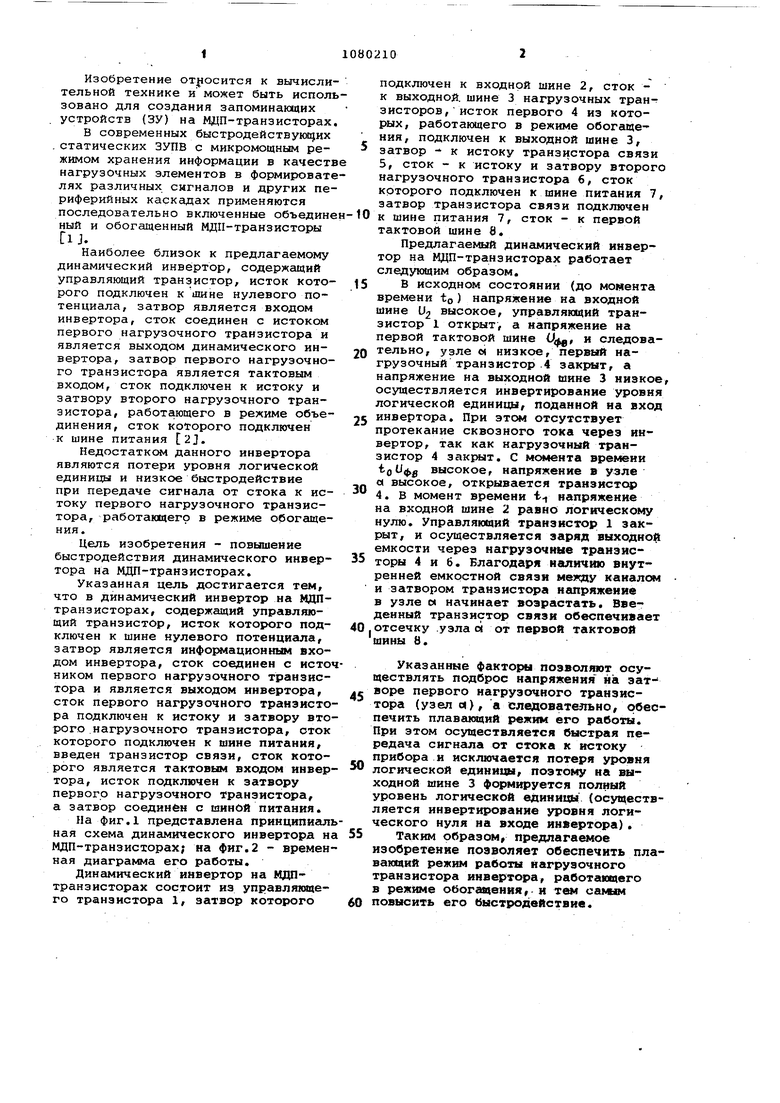

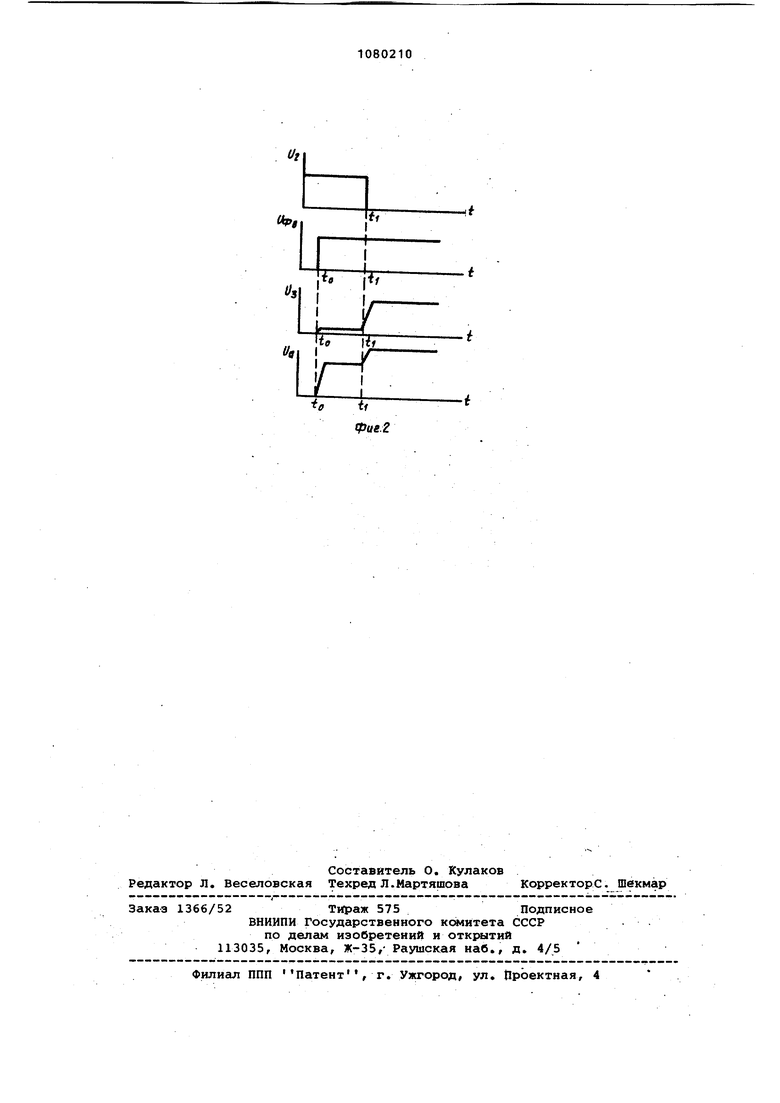

На фиг.1 представлена принципигшная схема динамического инвертора н МДП-транзисхорах; на фиг.2 - временная диаграмма его работы.

Динамический инвертор на МДПтранзисторах состоит из управляяицего транзистора 1, затвор которого

подключен к входной шине 2, сток к выходной, шине 3 нагрузочных транзисторов, исток первого 4 из которых, работающего в режиме обогаще. НИН, подключен к выходной шине 3, затвор - к истоку транзистора связи 5, сток - к истоку и затвору второго нагрузочного транзистора 6, сток которого подключен к шине питания 7, затвор транзистора связи подключен

0 к шине питания 7, сток - к первой тактовой шине в.

Предлагаемый динамический инвертор на ВДП-транзисторах работает следующим образом.

5 В исходном состоянии (до момента времени to) напряжение на входной шине 1)2 высокое, управляющий транзистор 1 открыт, а напряжение на первой тактовой шине Ц, и следовательно, узле « низкое, первый нагрузочный транзистор .4 закрыт, а напряжение на выходной шине 3 низкое, осуществляется инвертирование уровня логической единицы, поданной иа вход

5 инвертора. При этом отсутствует

протекание сквозного тока через инвертор, так как нагрузочный транзистор 4 закрыт. С момента времени высокое, напряжение В узле о( высокое, открывается транзистор 4. В момент времени i напряжение на входной шине 2 равно логическому нулю. Управляющий транзистор 1 закрыт, и осуществляется заряд выходной емкости через нагрузочные траизис5 торы 4 и 6. Благодаря наличию внутренней емкостной связи м&гспу каналом и затвором транзистора напряжение в узле начинает возрастать. Введенный транзистор связи обеспечивает

0,отсечку .узла ci от первой тактовой

шины 8.

Указанные Факторы поэволюот осуществлять подброс напряжения на эатворе первого нагрузочного транзистора (узел 01), а следовательно, обеспечить плавакядий режим его работы. При зтом осуществляется быстрая передача сигнала от стока к истоку прибора и исключается потеря уровня

логической единицы, поэтому на выходной шине 3 формируется полный уровень логической единицы (осуществляется инвертирование уровня логического нуля на входе инвертора).

Таким образом, предлагаемое

изобретение позволяет обеспечить плавающий режим работы нагрузочного транзистора инвертора, работающего в режиме обогащения, и т&л самом

повысить его быстродействие.

V9

rl

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4096584, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Динамическая ячейка на мдп транзисторах | 1973 |

|

SU478361A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-03-15—Публикация

1982-12-20—Подача