1

Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности в мощных выходных каскадах логических устройств.

Известен инвертор на МДП-транзисторах, содержащий два нагрузочных траняистора, соединенных последовательно с входным ппеключающим транзистором, двухтактный выходной каскад, ускоряющий конденсатор, подключенный одним выводом к выходной шине, а другим - к истоку первого нагрузочного транзистора, стоку и затяору второго нагрузочного транзистора Llj

Недостатком данного устройства является наличие сквозного тока, протекающего через выходные транзисторы при работе инвертора в динамическом режиме (при подаче логической единицы на вход устройства некоторое время оба выходных транзистора оказьшаются открытьми и через них протекает ток от шины питания к общей шине), что приводит к большому потреблению мощности в динамическом режиме.

Наиболее близким к изобретению является формирователь импульсов, содержащий конденсатор, первая обкладка которого соединена с истоком первого транзистора, сток и затвор которого подключены к щине питания, второй транзистор, сток которого соединен с шиной питания, затвор - со стоком третьего транзистора, исток - с второй обкладкой конденсатора и с выходной шиной, затвор третьего транзистора соединен с входной шиной и со стоком четвертого транзистора, затвор которого .соединен с шиной питания, исток - с затвором пятого транзистора, исток которого соединен с ис током третьего транзистора и с общей шиной, при этом сток третьего транзистора соединен с истоком первого транзистора, а исток второго со стоком пятого транзистора. В известном устройстве за счет цепи задержки на четвертом транзисторе сквозной ток отсутствует .

Недостатком известного устройства является его низкое быстродействие, так как для включения и выключения неинвертирующего транзистора выходного каскада необходимо

283882

заряжать конденсатор через нагрузочный транзистор входного инвертора и разрежать через входной транзистор инвертора.

Цель изобретения - повьшение быстродействия устройства.

Поставленная цель достигается тем, что в инвертор на МДП-транзисIQ торах, содержащий конденсатор, первый вывод которого соединен с истоком первого транзистора, сток и затяор которого подключены к шине питания, второй транзистор, сток JJ которого соединен с шиной питания, затвор - со стоком третьего транзистора, исток - с вторым выводом конденсатора и с выходной шиной, затвор третьего транзистора соединен с входной шиной и со стоком

четвертого транзистора, затвор ко-, торого соединен с шиной питания, а -исток - с затвором пятого транзистора, исток которого соединен с

5 истоком третьего траняистора и с общей шиной, введены шестой и седьмой транзисторы, причем затвор и сток шестого траняистора соединены с первой обкладкой конденсатора, а исток - со стоком третьего транзистора, затвор седьмого транзистора соединен с входной ишной, сток - с выходной шиной, а исток со стоком пятого транзистора.

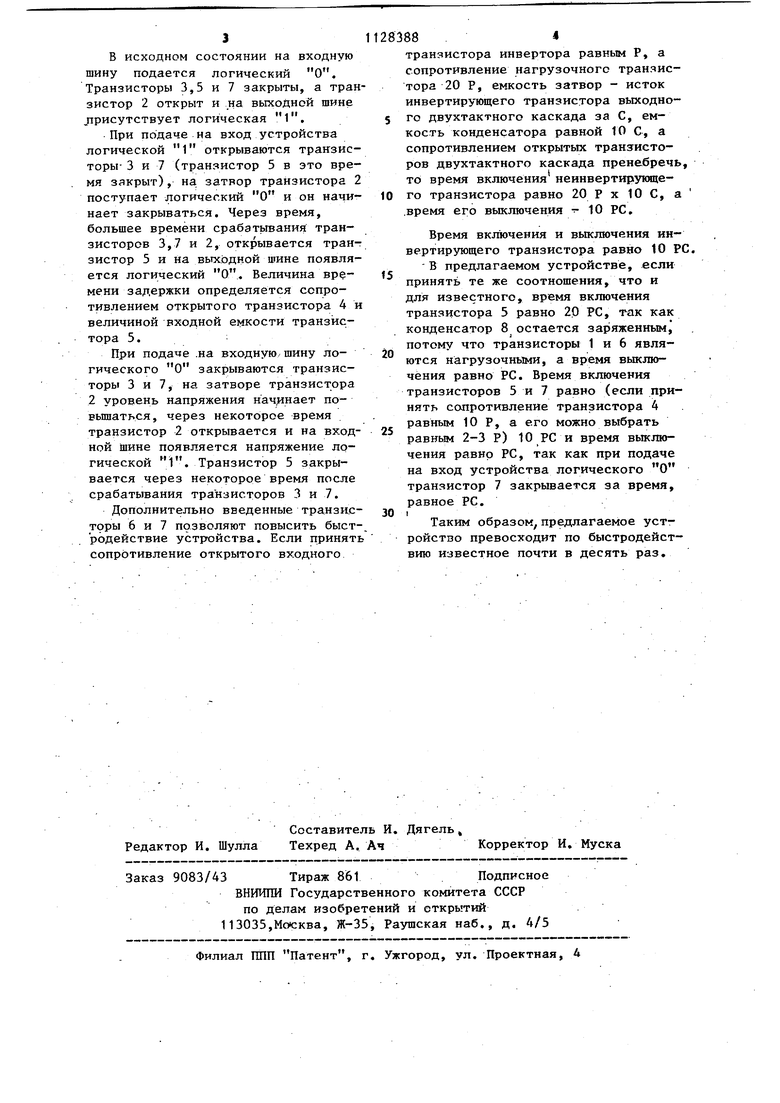

На чертеже представлена принци5 пиальная электрическая схема предлагаемого инвертора.

Устройство содержит транзисторы 1-7 и конденсатор 8. Первый вывод конденсатора 8 соединен с истоком

транзистора 1, затвор и сток кото. рого соединены с шиной питания и с затррром и стоком транзистора 6, исток которого соединен со стоком транзистора 3 и с затвором траняис тора 2. Сток транзистора 2 соединен с щиной питания, исток - с второй обкладкой конденсатора, со стоком транзистора 7 и.с выходной ши, ной. Затворы, транзисторов 3 и 7

0 соединены с входной шиной. Истоки транзисторов 3 и 5 соединены с общей шиной. Затвор транзистора 4 подключен к шине питания, сток - к входной шине, а исток - к затвору .

5 транзистора 5. Сток транзистора 5 соединен с истоком траняистора 7. Устройство работает следующим , образом

3

в исходном состоянии на входную шину подается логический О, Транзисторы 3,5 и 7 закрыты, а транзистор 2 открыт и на выходной шине jipHcyTCTsyeT логическая 1,

При подаче на вход устройства логической 1 открываются транзисторы- 3 и 7 (транзистор 5 в это время закрыт), на затвор транзистора 2 поступает логический О и он начинает закрываться. Через время, большее времени срабатьгеания транзисторов 3,7 и 2, открывается транзистор 5 и на выходной шине появля ется логический О, Величина вр мени задержки определяется сопротивлением открытого транзистора 4 и величиной входной емкости транзистора 5. ;

При подаче .на входную/шину логического О закрываются транзисторы 3 и 7, на затворе транзистора 2 уровень напряжения начинает поБЬШ1аться, через некоторое время транзистор 2 открывается и на входной шине появляется напряжение логической 1. Транзистор 5 закрывается через некоторое время после срабатывания транзисторов 3 и 7.

Дополнительно введенные транзисторы 6 и 7 позволяют повысить быстродействие устройства. Если принять сопротивление открытого входного

28388

транзистора инвертора равным Р, а сопротивление нагрузочного транзистора 20 Р, емкость затвор - исток инвертирующего транзистора выходно- 5 го двухтактного каскада за С, емкость конденсатора равной 10 С, а сопротивлением открытых транэгисторов двухтактного каскада пренебречь, то время включения неинвертирующе- 0 го транзистора равно 20 Р х 10 С, а .время его выключения - 10 PC,

Бремя включения и выключения инвертирующего транзистора равно 10 PC.

В предлагаемом устройстве, .если принять те же соотношения, что и для известного, время включения транзистора 5 равно 2Q PC, так как конденсатор 8 остается заряженным потому что транзисторы 1 и 6 являются нагрузочными, а время выключения равно PC. Время включения транзисторов 5 и 7 равно (если принять сопротивление транзистора 4 равным ЮР, а его можно выбрать равньм 2-3 Р) 10 PC и время выключения равно PC, так как при подаче на вход устройства логического О транзистор 7 закрывается за время,

равное PC. I

Таким образом, предлагаемое устройство превосходит по быстродействию известное почти в десять раз.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Инвертор на мдп-транзисторах | 1976 |

|

SU646441A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Выходное устройство | 1978 |

|

SU771874A1 |

| Управляемый инвертор на мдп-транзисторах | 1976 |

|

SU641655A1 |

| Буферное устройство | 1979 |

|

SU822366A1 |

ИНВЕРТОР НА МДП-ТРАНЗИСТОРАХ, содержащий конденсатор, первый вьшод которого соединен с истоком первого транзистора, сток и затвор которого подключены к шине питания, второй транзистор, сток которого соединен с шиной питания, затвор со стоком третьего ,тран- . зистора, исток - с вторым вьгеодом конденсатора и с выходной шиной, затвор третьего транзистора соединен с входной шиной и с стоком четвертого транзистора, затвор.которого соединен с шиной питания, а исток - с затвором пятого транзистора, исток которого соединен с истоком третьего транзистора и .с общей шиной, отличаю ш, и йс я тем, что, с целью повьш1ения его быстродействия, в него введены шестой и седьмой транзисторы, причем затвор и сток шестого транзис- тора соединены с первой обкладкой конденсатора, а исток - со стоком третьего транзистора, затвор седьмого транзистора соединен с входной шиной,- сток - с выходной шиной, а исток - со стоком пятого транзистора. -0f д х со эо вм. эо АНС гч-4 .Л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-12-07—Публикация

1982-01-04—Подача