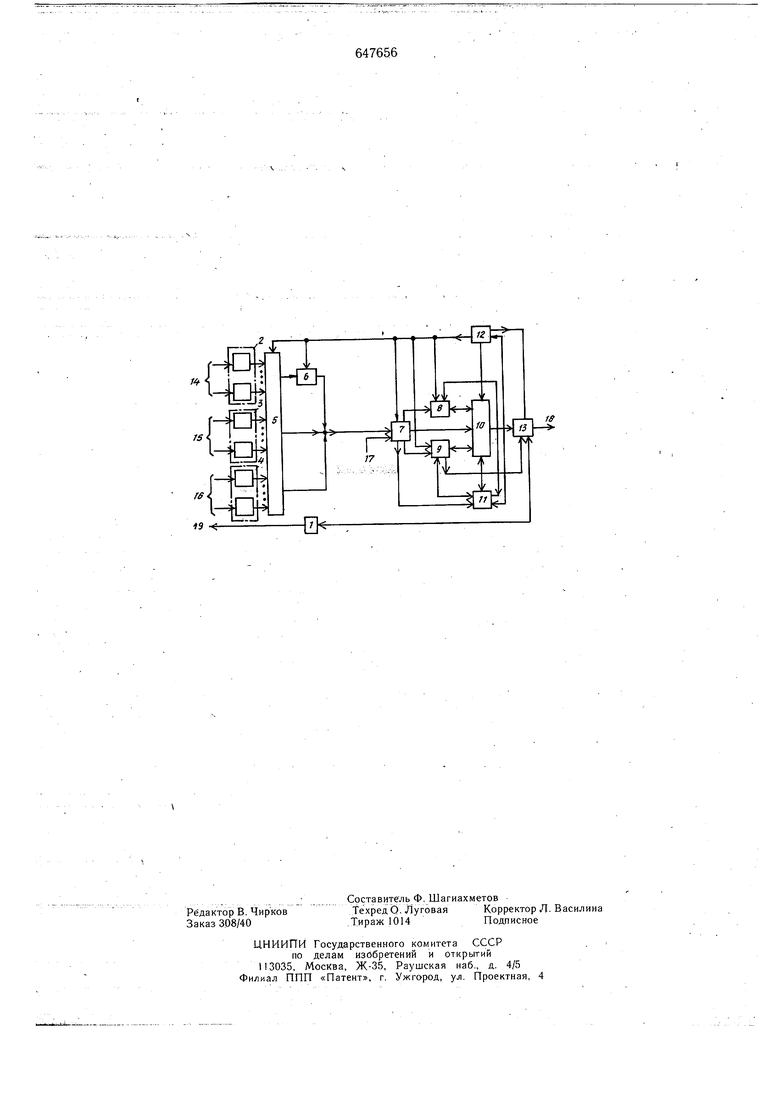

(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОБЪЕКТОМ и потому устройство производит операции умножения и деления соответственно умножением и делением, которые требуют большего времени, чем операции сложения и вычитания. Постоянство шагов квантования аналого-цифровых преобразователей, определяющих пилообразность относительной погрешности измерения по диапазону измерения (в начале каждого поддиапазона измерения погрешность выше, чем в конце его), приводит к значительной по величине относительной погрешности и к большему разбросу результатов расчета, избыточности количества результатов измерения и вычислений. Цель изобретения - повышение быстродействия, выравнивание и увеличение точности управления. Поставленная цель достигается тем, что устройство содержит преобразователь аналоговых величин в цифровые величины целочисленнь х логарифмов, блок логарифмирования и блок антилогарифмирования, причем первый, второй входы и выход преобразователя аналоговых величин в цифровые величины целочисленных логарифмов соединены соответственно с третьим выходом коммутатора, с первым выходом блока управления и с первым входом блока ввода, первые входы блоков логарифмирования и антилогарифмирования соединены с первым выходом блока управления, третий и четвертый выходы блока ввода соединены со вторыми входами соответственно блока логарифмирования и блока,антилогарифмирования, первые и вторые входы-выходы которых соединены соответственно с третьим, четвертым входами-выходами блока памяти и с третьим, четвертым входами-выходами арифметико-логического блока, а выход блока антилогарифмирования соединен с третьим входом блока вывода. Структурная схема устройства представлена на чертеже. Устройство для управления объектом содержит исполнительный блок 1, группы 24 датчиков, коммутатор 5, преобразователь 6 аналоговых величин в цифровые величины целочисленных логарифмов, блок 7 ввода, блок 8 логарифмирования, блок 9 антилогарифмирования, арифметико-логический блок 10, блок 11 памяти, блок 12 управления, блок 13 вывода, группы 144-16 входов, вход 17, первый 18 и второй 19 выходы. Устройство работает следующим образом. Устройство имеет группу 14 входов для непрерывных, группу 15 для .целочисленных и. группу 16 входов для двоичных параметров типа «да, «нет. Непрерывные параметры поступают в соответствующие датчики группы 2, которыми они нормализуются по величине (превращаются в напряжение определенной амплитуды) и по значению для последующего преобразования одни.м преобразователем 6. Целочисленные параметры фиксируются соответствующими даГчиками группы 3, а двоичные параметры фиксируются датчиками группы 4 для передачи в блок 7 Арифметические операции производятся в арифметико-логическом блокеЛО со следующими особенностями. Если данная операция является сложением или вычитанием, то информация от преобразователя 6 предварительно проходит через блок 9 антилогарифмирования, после чего она поступает в блок 10 для суммирования. Если этот аргумент от преобразователя 6 используется в последующих вычислениях, он одновременно поступает в блок II. Если для рассматриваемой операции сложения или вычитания аргументом является результат предшествующих вычислений, то последний остается в арифметико-логическом блоке 10 неизменным, а если он получен в виде целочисленного логарифма, то предварительно пропускается через блок 9 антилогарифмирования. Целочисленные величины от датчиков группы 3, участвующие в данной операции, направляются непосредственно в арифметико-логический блок 10 через коммутатор 5 и блок 7 ввода. Если производится операция умножения или деления, то информация от преобразователя 6 поступает через блок 7 ввода непосредственно в блок 10, а целочисленные величины от датчиков группы 3 через коммутатор 5 предварительно пропускаются через блок 8 логарифмирования, превращающий их в целочисленные логарифмы. Результаты промежуточных вычислений, проведенные в логарифмической .форме и участвующие в данной операции, остаются в арифметико-логическом блоке 10 неизменными, а результаты вычислений, проведенные в самих значениях величин, предварительно пропускаются через блок 8 логарифмирования, т. е. при выполнении операций умножения и деления исходных величин они, будучи преобразованными в целочисленные логарифмы, складываются или , вычитаются в арифметико-логическом блоке 10. После последней операции результат вычислений, если он получен в логарифмическом виде, проходит через блок 9 антилогарифмирования и поступает либо в блок 13 вывода, либо в блок 11 памяти. Двоичная информация типа «да, «нет от датчиков группы 4 через коммутатор 5 и блок 7 ввода поступает в блок 11 памяти и далее в арифметико-логический блок 10, в которых и (совместно с блоком 12 управления) используется для принятия соответствующих рещений. Изменение состояния объекта контроля и управления производится исполнительным блоком 1, получающим соответствующие сигналы. Коды от коммутатора 5 и преобразователя 6 проходят в арифметикологический блок 10 в зависимости от программы работы по сигналам вызова, приходящим от блока 12 управления.

Преи1мущества изобретения по сравнению с известным устройством состоят, вопервых, в увеличении быстродействия, достигаемого заменой операции умножения и деления соответственно операциями сложения и вычитания, во-вторых, в повышении и выравнивании точности результатов вычислений, что для автоматизированной системы управления технологическими процессами приводит к повышению качества и однородности вырабатываемого ею продукта (данное свойство является следствием использования в изобретении равноточного по всему диапазону измерения преобразователя), в-третьих, в сокращении требуемого объема блока памяти, что является следствием использования равноточного преобразователя из-за отсутствия избыточных результатов измерения ими при заданной точности.

Формула изобретения

Устройство для управления объектом, содержащее группы датчиков, выходы которых соединены с соответствующими группами входов коммутатора, блок ввода, первый вход которого соединен с первым и вторым выхода.ми коммутатора, арифметикологический блок, выход которого соединен с первым входом блока вывода, блок памяти, вход которого соединен с первым выходом блока ввода, блок управления, первый выход которого соединен со входом коммутатора и со вторым входом блока ввода, причем второй вход и первый выход блока вывода соединены сйответственно со вторым выходом блока управления и со входом исполнительного блока, первый и второй входы - выходы блока памяти соединены с

первыми входами-выходами .соответственно блока управления и арифметико-логического блока, второй вход-выход которого соединен соответственно со вторым входом-выходом блока управления и вторым выходом блока ввода, третий вход блока ввода, входы групп датчиков, выходы блока вывода и исг олнительного блока являются соответственно входом устройства, группами входов

устройства, первым и вторым выходами устройства, отличающееся тем, что, с целью повышения быстродействия, выравнивания и увеличения точности управления, оно содержит преобразователь аналоговых величин в цифровые величины целочисленных

логарифмов, блок логарифмирования и блок антилогарифмирования, причем первый, второй входы и выход преобразователя аналоговых величин в цифровые величины целочисленных логарифмов соединены соответственно с третьим выходом коммутатора, с первым выходом блока управления и с первым входом блока ввода, первые входы блоков логарифмирования и антилогарифмирования соединены с первым выходом блока управления, третий и четвертый выходы блока ввода соединены со вторыми входами собтветственно блока логарифмирования и блока антилогарифмирования, первые и вторые входы - выходы которых соединены соответственно с третьим, четвертым входамивыхода15№ блока памяти и с третьим, четвертым входами-выходами арифметико-логического блока, а выход блока антилогарифмирования соединен с третьим входом блока вывода.

Источники информации, принятые во внимание при экспертизе

1.Малиновский Б. Н. Цифровые управляющие машины и автоматизация производства, «Машиностроение, М., 1963, с. 17.

2.Каталог «Комплекс технических средств М-6000 АСВТ-М, часть 1.4, НИИЦВМ, Северодонецк, 1972, с. 59.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптический вычислительный модуль в системе остаточных классов | 1989 |

|

SU1686442A1 |

| Цифровое усредняющее устройство | 1979 |

|

SU842836A1 |

| Устройство для управления @ -пульсным выпрямителем | 1986 |

|

SU1363405A1 |

| Функциональный преобразователь | 1986 |

|

SU1397905A1 |

| Вычислительное устройство | 1990 |

|

SU1742814A1 |

| Устройство для ввода аналоговой информации | 1985 |

|

SU1277083A1 |

| Цифро-аналоговая система для регистрации и статистической обработки информации | 1979 |

|

SU858023A1 |

| Устройство для решения системы алгебраических уравнений | 1981 |

|

SU966702A1 |

| Устройство для логарифмирования | 1982 |

|

SU1030800A1 |

| Устройство для возведения в степень | 1977 |

|

SU653619A1 |

Авторы

Даты

1979-02-15—Публикация

1977-03-18—Подача