(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМЫ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ

1

изобретение относится к вычислительной технике, в частности к специализированным цифровым вычислительным устройствам для решения систем алгебраических уравнений и задач линейного программирования, Оно может быть использовано как автономно, так и в составе цифровых и аналого-цифровых вычислительных комплексов.

Известно цифровое устройство для ю решения систем алгебраических уравнений.

Известное устройство характеризуется тем, что содержит блоки формирования коэффициентов, сумматоры, регистры, цифровые интеграторы, коммутатор и элементы И | 1 .

Недостатками этого устройства являются низкие скорости обработки информ ции, большое количество оборудова- 20 ниА и низкая технологичность.

Наиболее близким к предлагаемому является циЛровое устройство для решения систем алгебраических уравнений.

Это устройство характеризуется те, что содержит блок уравновешивания, блок синхронизации, блок ввода-вывода, блок индикации и (м+2 ) вычислительных блоков, каждый из которых состоит из арифметико-логического узла, группы регистров и формирователя адресов (где hi - число уравнений решаемой системы алгебраических уравнений).

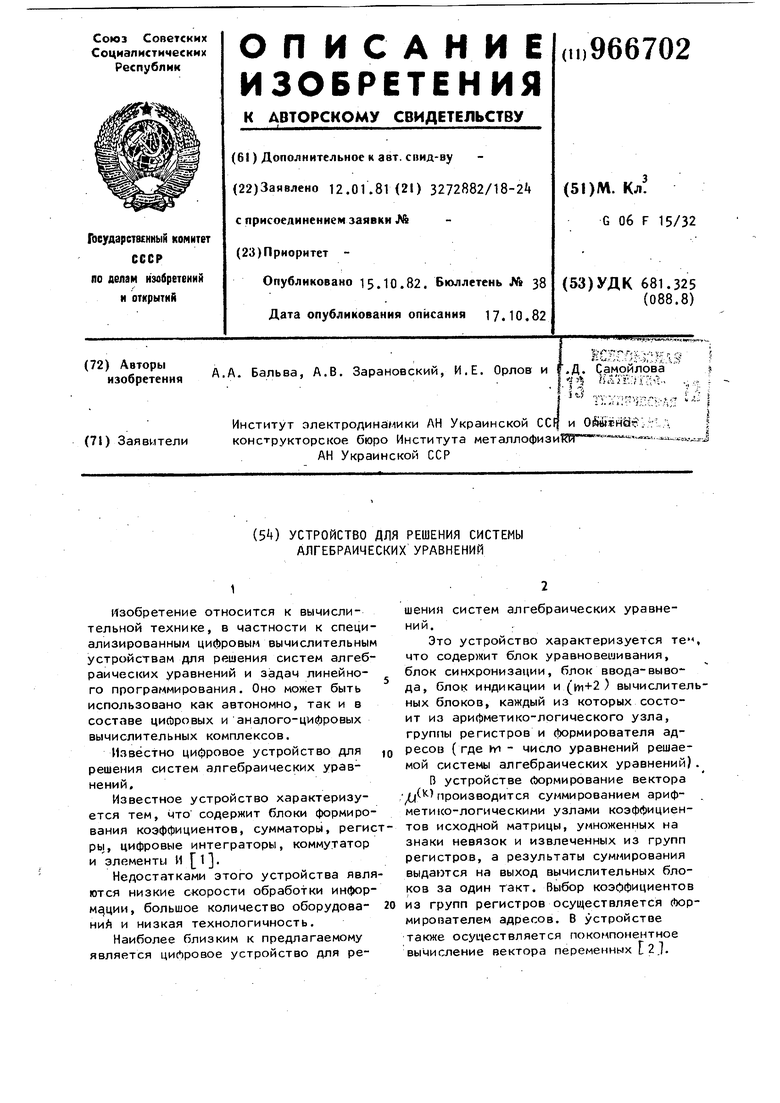

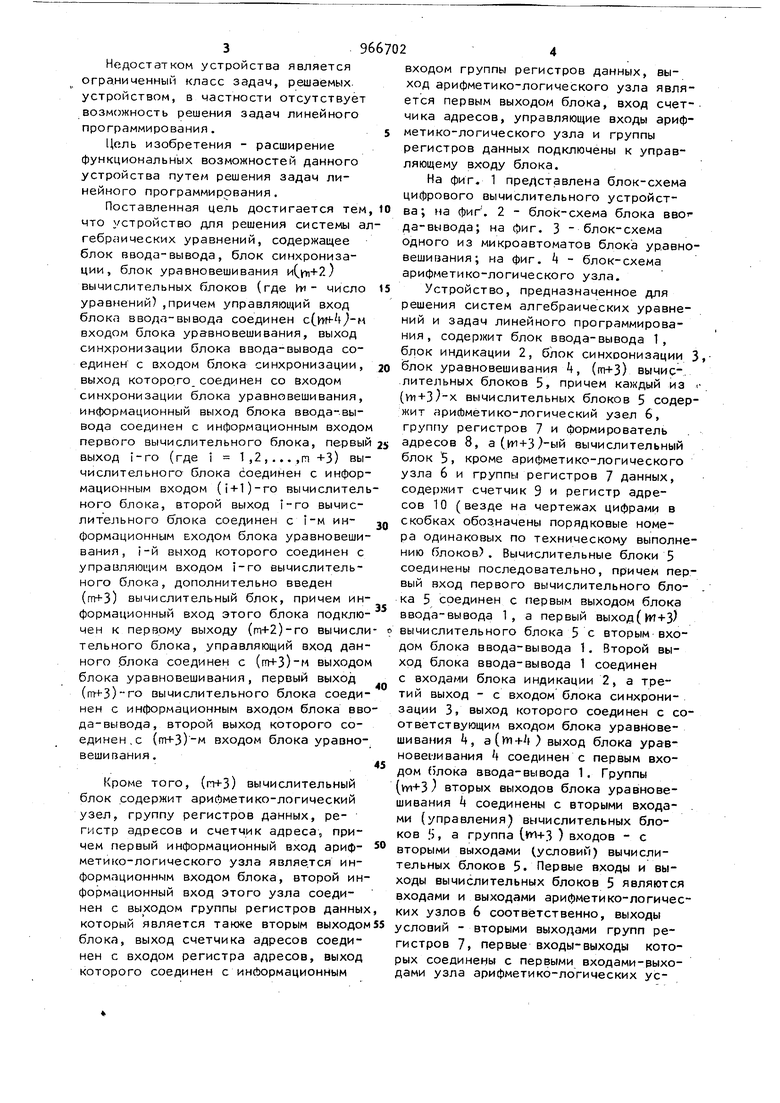

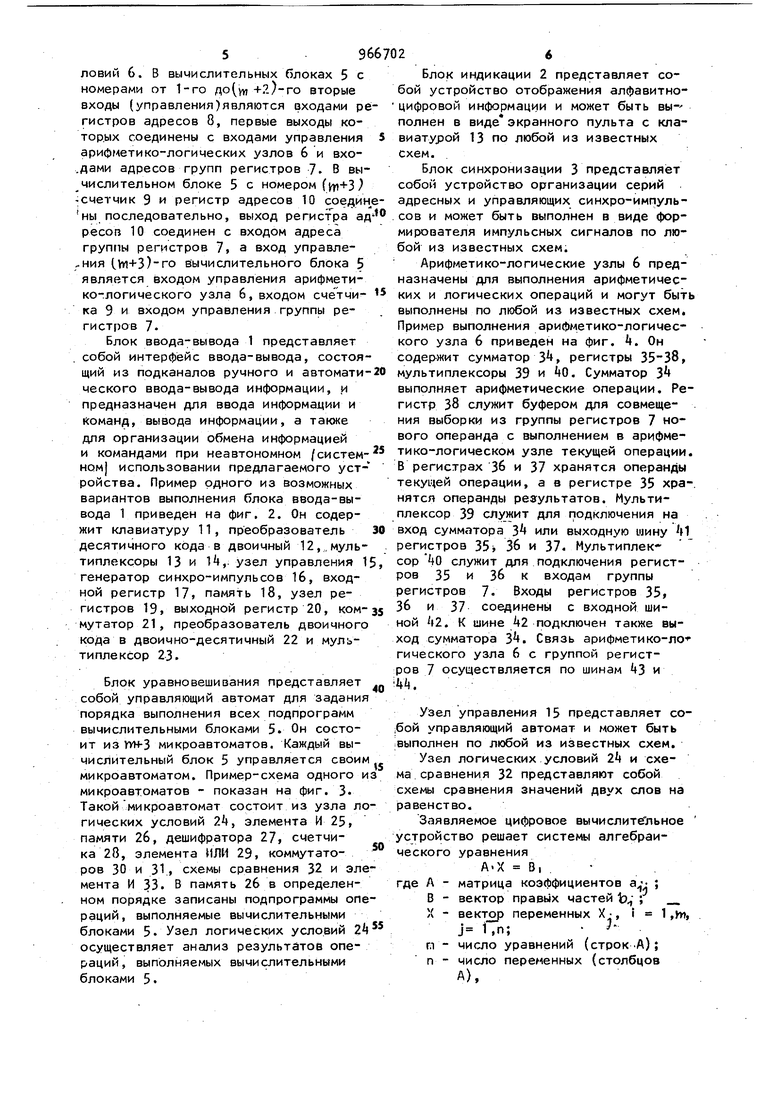

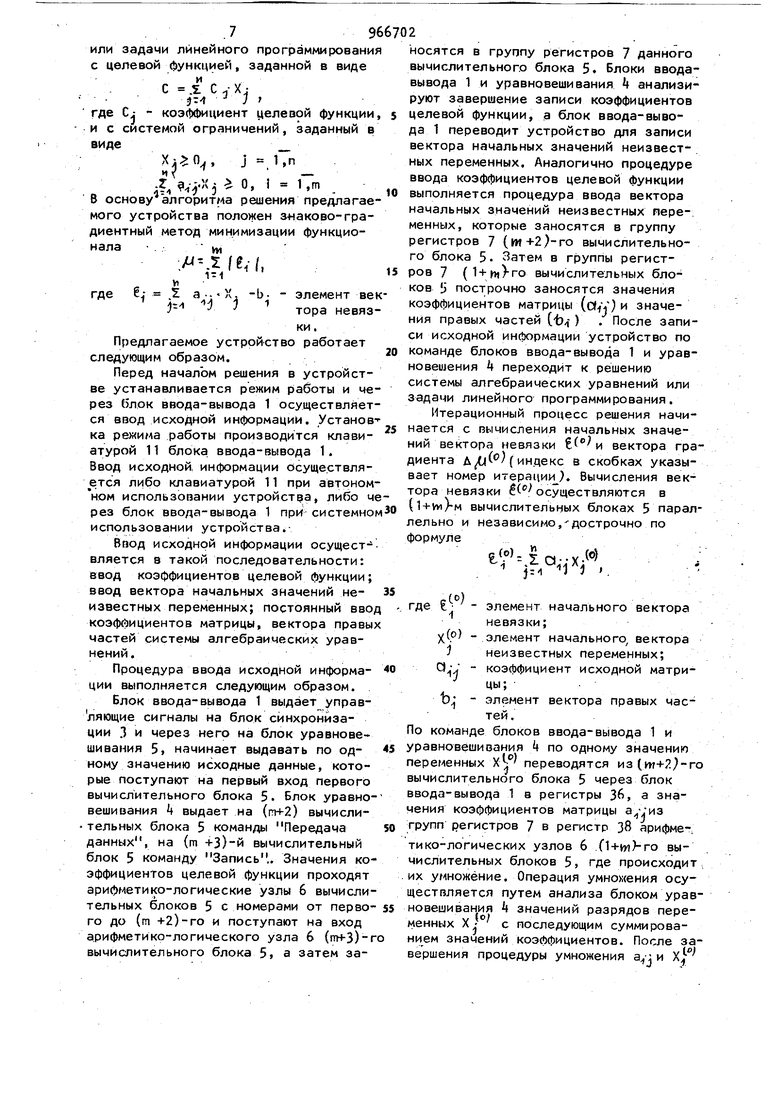

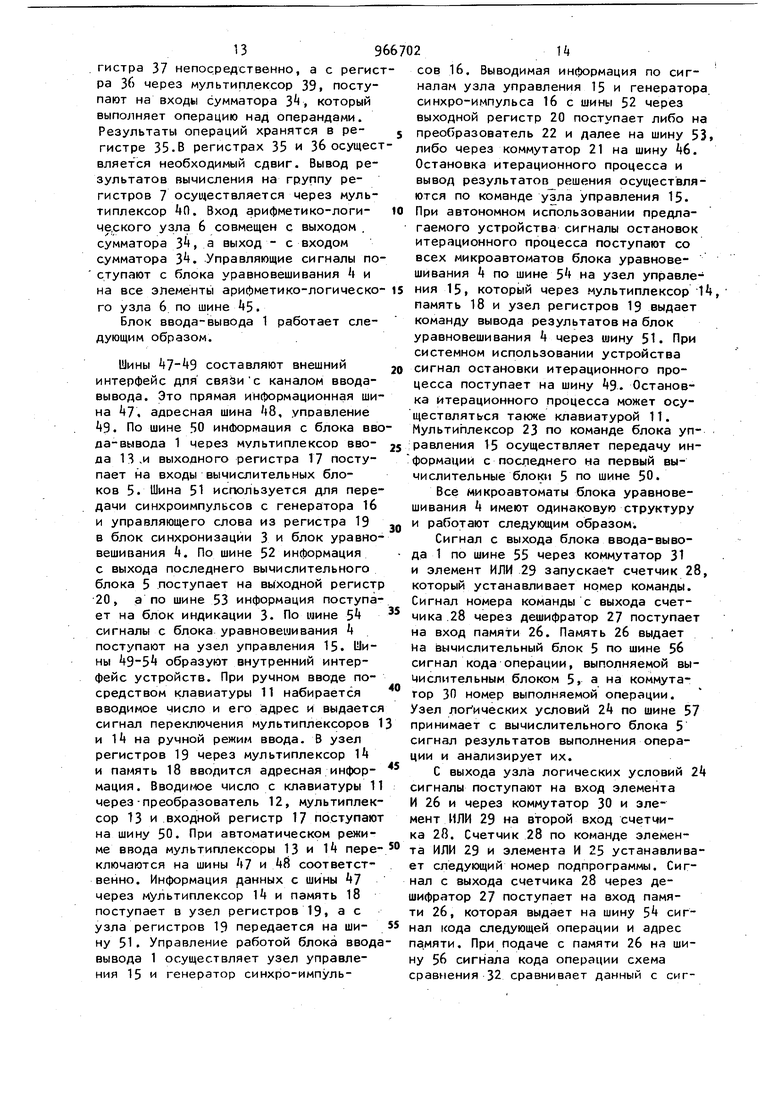

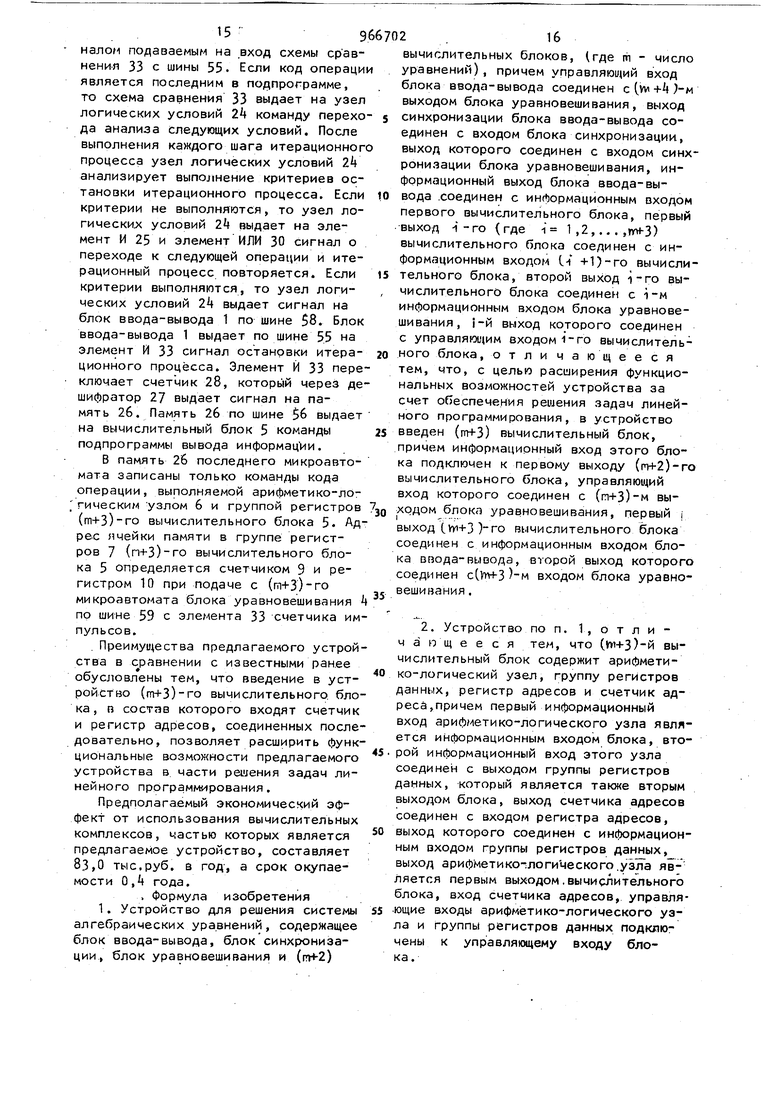

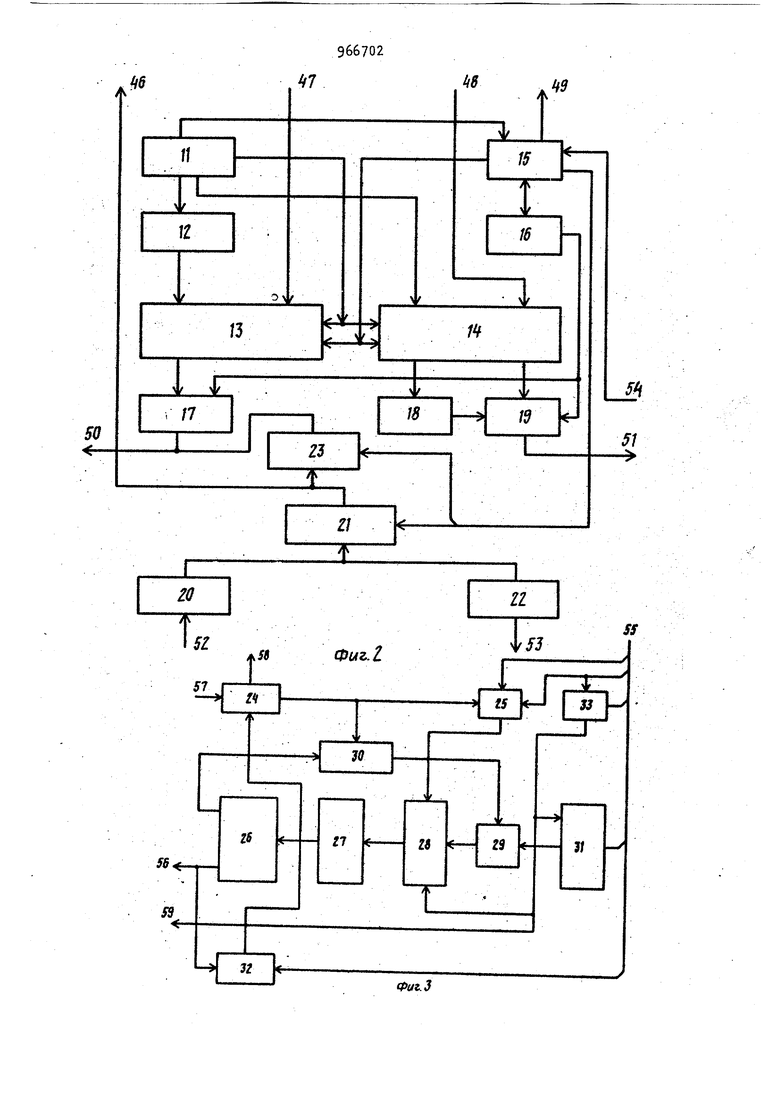

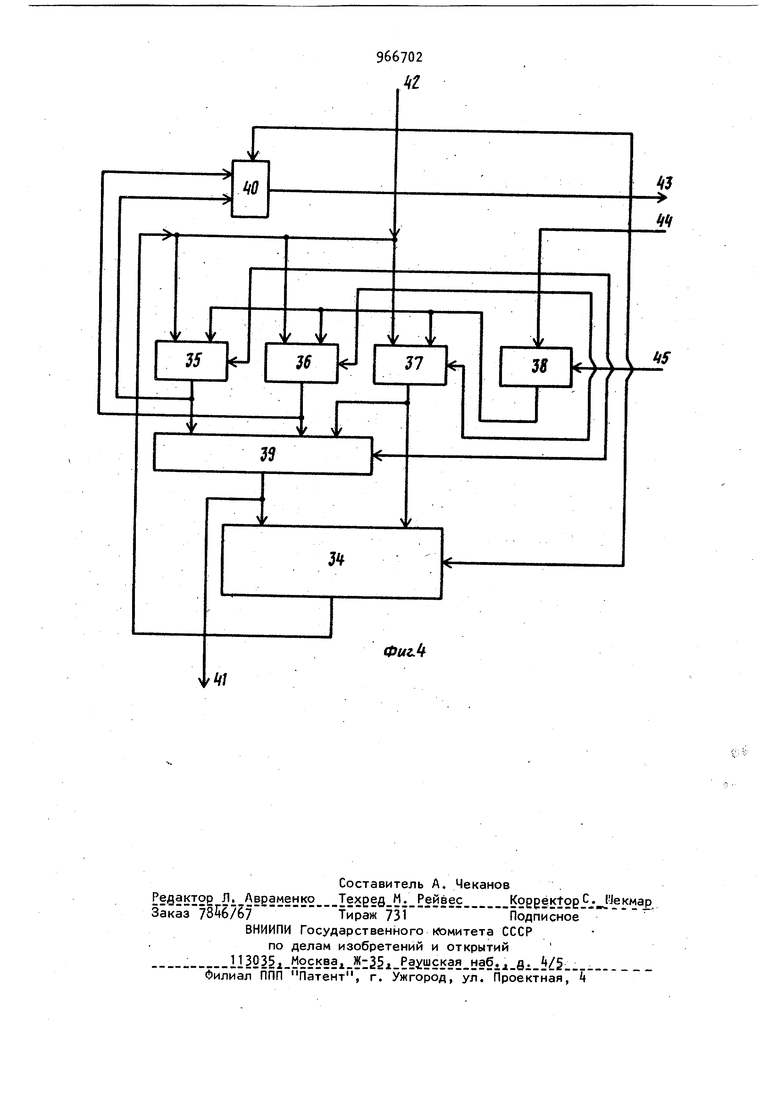

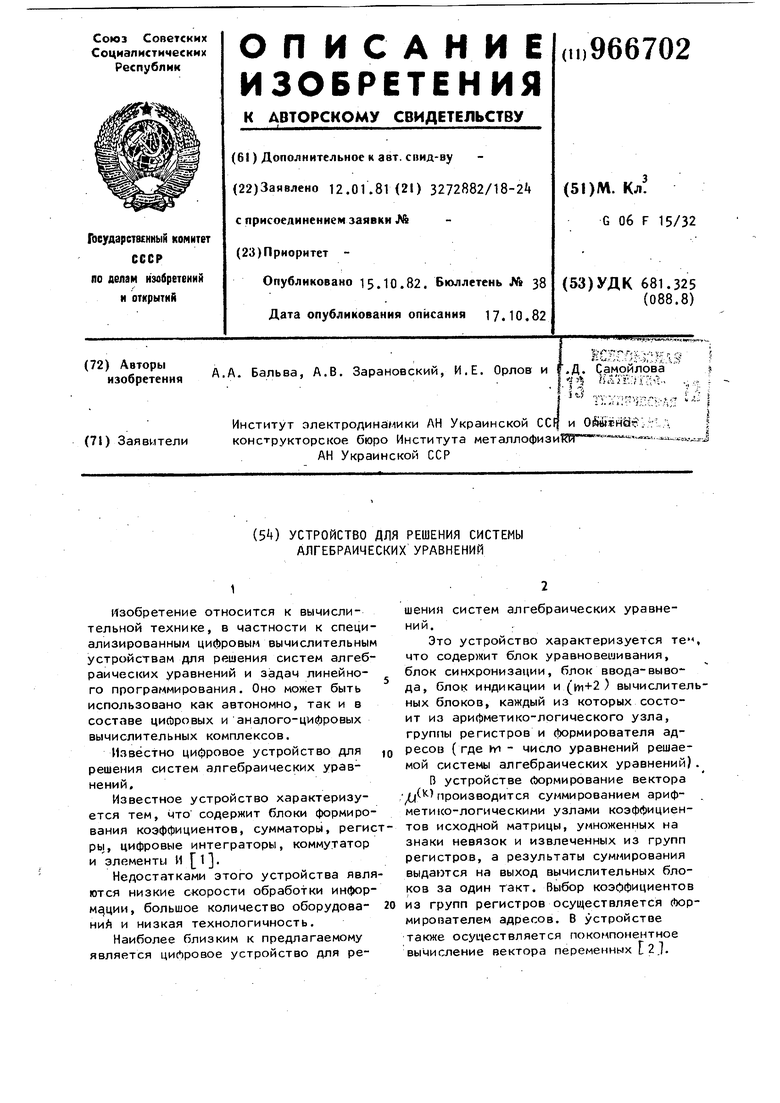

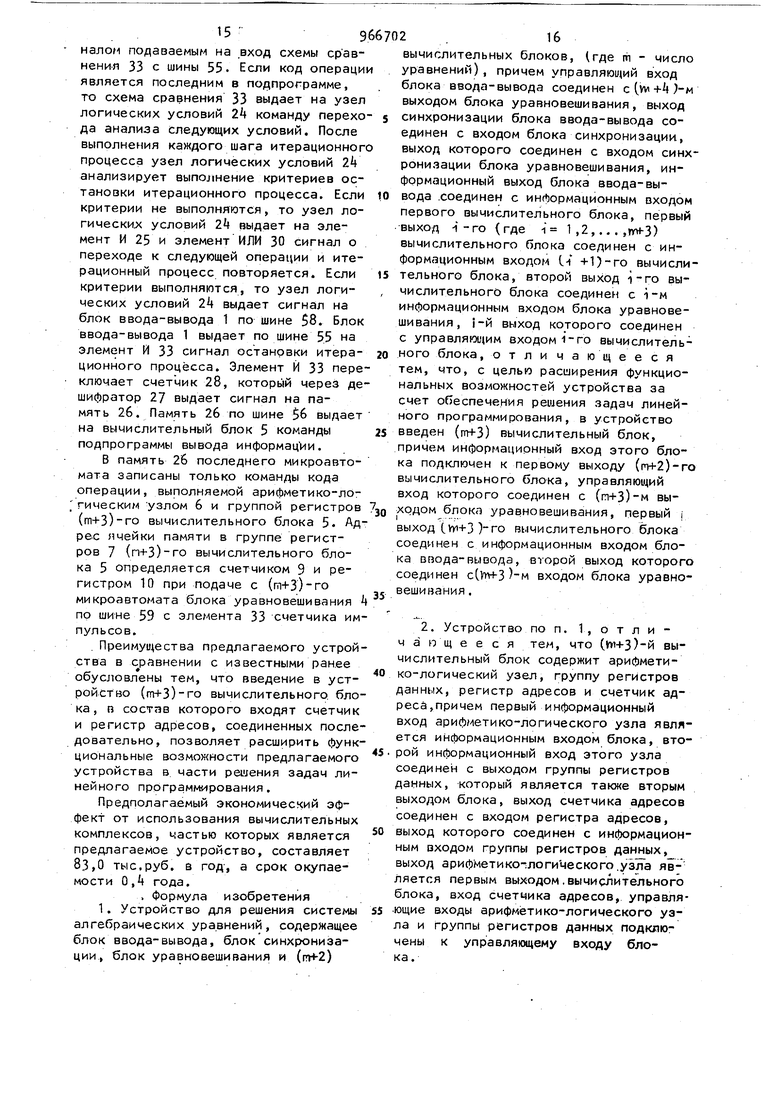

R устройстве формирование вектора .-п Ътроизводится суммированием арифметико-логическими узлами коэффициентов исходной матрицы, умноженных на знаки невязок и извлеченных из групп регистров, а результаты суммирования выдаются на выход вычислительных блоков за один такт. Выбор коэффициентов из групп регистров осуществляется Лормирогаателем адресов. В устройстве также осуществляется покомпонентное вычисление вектора переменных L 2.. 396 Недостатком устройства является ограниченный класс задач, решаемых устройством, в частности отсутствует возмсжность решения задач линейного программирования. Цель изобретения - расширение функциональных возможностей данного устройства путем решения задач линеиного программирования. Поставленная цель достигается тем, что устройство для решения системы ал гебраических уравнений, содержащее блок ввода-вывода, блок синхронизации, блок уравновешивания и(+2) вычислительных блоков (где hi- число уравнений),причем управляющий вход блока ввода-вывода соединен )-H входом блока уравновешивания, выход синхронизации блока ввода-вывода соединен с входом блока синхронизации, выход которого соединен со входом синхронизации блока уравновешивания, информационный выход блока ввода-.вывода соединен с информационным входом первого вычислительного блока, первый выход i-ro (где 1 1,2,,..,гт +3) вычислительного блока соединен с информационным входом (i+l)-ro вычислитель иого блока, второй выход 1-го вычислительного блока соединен с i-м ийформационным входом блока уравновешивания, i-й выход которого соединен с управляющим входом i-ro вычислительного блока, дополнительно введен (т+З) вычислительный блок, причем информационный вход этого блока подключен к первому выходу (т+2)-го вычисли тельного блока, управляющий вход данного блока соединен с (ггн-3)м выходом блока уравновешивания, первый выход (т+3)го вычислительного блока соединен с информационным входом блока вво да-вывода, второй выход которого соединен, с (т+3)м входом блока уравновешивания. Кроме того, (п+3) вычислительный блок содержит арифметико-логический узел, группу регистров данных, регистр адресов и счетчик адреса, причем первый информационный вход арифметико-логического узла является информпционным входом блока, второй информационный вход этого узла соединен с выходом группы регистров данных который является также вторым выходом блока, выход счетчика адресов соединен с входом регистра адресов, выход которого соединен с информационным входом группы регистров данных, выход арифметико-логического узла является первым выходом блока, вход счетчика адресов, управляющие входы арифметико-логического узла и группы регистров данных подключены к управляющему входу блока. На фиг. 1 представлена блок-схема цифрового вычислительного устройства; на фиг . 2 - блок-схема блока ввог да-вывода; на фиг. 3 - блок-схема одного из микроавтоматов блока ур.авновеширэания; на фиг. 4 - блок-схема арифметико-логического узла. Устройство, предназначенное для решения систем алгебраических уравнений и задач линейного программирования, содержит блок ввода-вывода 1, блок индикации 2, блок синхронизации 3,ёлок уравновешивания k, (гп+З) вычир-. лительных блоков 5, причем каждый из (уп+3} Х вычислительных блоков 5 содержит арифметико-логический узел 6, группу регистров 7 и формирователь адресов 8, а(п+3)-ый вычислительный блок 5, кроме арифметико-логического узла 6 и группы регистров 7 данных, содержит счетчик 9 и регистр адресов 10 (везде на чертежах цифрами в скобках обоз начены порядковые номера одинаковых по техническому выполнению блоков. Вычислительные блоки 5 соединены последовательно, причем первый вход первого вычислительного блока 5 соединен с первым выходом блока ввода-вывода 1, а первый выход(И1+3 вычислительного блока 5 с вторым входом блока ввода-вывода 1. Второй выХОД блока ввода-вывода 1 соединен с входами блока индикации 2, а третий выход - с входом блока синхронизации 3 выход которого соединен с соответствующим входом блока уравновешивания 4, a( ) выход блока уравновеиивания соединен с первым входом блока ввода-вывода 1. Группы () вторых выходов блока уравновешивания k соединены с вторыми входа- . ми (управления) вычислительных блоков ), а группа (.V4+3 ) входов - с вторыми выходами (условий) вычислительных блоков 5. Первые входы и выходы вычислительных блоков 5 являются входами и выходами арифметико-логических узлов 6 соответственно, выходы условий - вторыми выходами групп регистров 7, первые входы-выходы которых соединены с первыми входами-рыходами узла арифметико-логических ус59667ловий 6. в вычислительных блоках 5 с номерами от 1-го no(w +2)-го вторые входы (управления)являются входами peiгистров адресов 8, первые выходы которых соединены с входами управления арифметико-логических узлов 6 и вхо.дами адресов групп регистров 7. В вы числитеяьном блоке 5 с номером (1+3 -счетчик 9 и регистр адресов 10 соедин ены последовательно, выход регистра ад-® ресов 10 соединен с входом адреса группы регистров 7, а вход управле,.ния (Wi+3)-ro бычислительного блока 5 является входом управления арифметико-логического узла 6, входом счетчи- ка 9 и входом управления группы регистров 7. Блок ввода-вывода 1 представляет собой интерфейс ввода-вывода, состоящий из подканалов ручного и автомати-20 ческого ввода-вывода информации, и предназначен для ввода информации и команд, вывода информации, а также для организации обмена информацией командами при неавтономном /систем НОМ} использовании предлагаемого уст ройства. Пример одного из возможных вариантов выполнения блока ввода-вывода 1 приведен на фиг. 2. Он содержит клавиатуру 11, преобразователь десятичного кода в двоичный 12,.,муль типлексоры 13 и Il, узел управления генератор синхро-импульсов 16, входной регистр 17, память 18, узел регистров 19, выходной регистр 20, ком мутатор 21, преобразователь двоичног кода в двоично-десятичный 22 и мультиплексор 23. Блок уравновешивания представляет собой управляющий автомат для задани порядка выполнения всех подпрограмм вычислительными блоками 5. Он состоит из 1W-3 микроавтоматов. Каждый вычислительный блок 5 управляется свои микроавтоматом. Пример-схема одного микроавтоматов - показан на фиг. 3. Такой микроавтомат состоит из узла л гических условий 2, элемента И 25, памяти 26, дешифратора 27, счетчика 28, элемента ИЛИ 29, коммутаторов 30 и 31., схемы сравнения 32 и эл мента И 33 В память 26 в определенном порядке записаны подпрограммы оп раций, выполняемые вычислительными блоками 5. Узел логических условий 2 осуществляет анализ результатов операций, выполняемых вычислительными блоками 5. 2 Блок индикации 2 представляет собой устройство отображения алфавитноцифровой информации и может быть выполнен в виде экранного пульта с клавиатурой 13 по любой из известных схем. Блок синхронизации 3 представляет собой устройство организации серий адресных и управляющих синхро-импульсов и может быть выполнен в виде формирователя импульсных сигналов по любой из известных схем. Арифметико-логические узлы 6 предназначены для выполнения арифметических и логических операций и могут быть выполнены по любой из известных схем. Пример выполнения арифметико-логического узла 6 приведен на фиг. k. Он содер жит сумматор 3, регистры 35-38, мультиплексоры 39 и ЦО, Сумматор З выполняет арифметические операции. Регистр 38 служит буфером для совмещения выборки из группы регистров 7 нового операнда с выполнением в арифметико-логическом узле текущей операции. В регистрах Зб и 37 хранятся операнды текущей операции, а в регистре 35 хра-. нятся операнды результатов. Мультиплексор 39 служит для подключения на вход сумматора 3 или выходную шину t1 регистров 35j 36 и 37. Мультиплексор +0 служит для подключения регистРов 35 и Зб к входам группы регистров 7. Входы регистров 35, Зб и 37 соединены с входной шиной (2. К шине k2 подключен также выход сумматора 3. Связь арифметико-ло- гического узла 6 с группой регистров 7 осуществляется по шинам 3 и kk. Узел управления 15 представляет со;бой управляющий автомат и может быть выполнен по любой из известных схем. Узел логических условий 2 и схема сравнения 32 представляют собой схемы сравнения значений двух слов на равенство. Заявляемое цифровое вычислительное устройство решает системы алгебраического уравнения А.Х В, матрица коэффициентов ; вектор правь1х частей Ъ ; BeKTjop переменных Х-, i 1 j 1,n; число уравнений (строк А); число переменных (столбцов А), или задачи линейного программирования с целевой функцией, заданной в виде с .51 с где С.- - коэффициент целевой функции и с системой ограничений, заданный в виде ХрП, j ,1.п В основу алгоритма решения предлагаемого устройства положен з аково-градиентный метод минимизации функционала VM :Р Д(г,(, 2 а -«)(. -Ь. - элемент ве 1 тора невязки. Предлагаемое устройство работает следующим образом. Перед началом решения в устройстве устанавливается режим работы и че рез С)лок ввода-вывода 1 осуществляет ся ввод исходной информации. Установ ка режима работы производится клавиатурой 11 блока ввода-вывода 1. Ввод исходной, информации осуществляется либо клавиатурой 11 при автоном ном использовании устройства, либо ч рез блок ввода-вывода 1 при системно использовании устройства. Ввод исходной информации осуществляется в такой последовательности: ввод коэффициентов целевой функции; ввод вектора начальных значений неизвестных переменных; постоянный вво коэффициентов матрицы, вектора правы частей системы алгебраических уравнений. Процедура ввода исходной информации выполняется следующим образом. Блок ввода-вывода 1 выдает управляющие сигналы на блок синхронизации 3 и через него на блок уравновешивания 5, начинает выдавать по одному значению исходные данные, которые поступают на первый вход первого вычислительного блока 5. Блок уравновешивания k выдает на (т+2) вычислительных блока 5 команды Передача данных, на (т +3)й вычислительный блок 5 команду Запись,. Значения ко эффициентов целевой функции проходят арифметико-логические узлы 6 вычисли тельных блоков 5 с номерами от перво го до (т +2)-го и поступают на вход арифметико-логического узла 6 {ггн-3)вычислительного блока 5, а затем заносятся в группу регистров 7 данного вычислительного блока 5. Блоки вводавывода 1 и уравновешивания k анализируют завершение записи коэффициентов целевой функции, а блок ввода-вывода 1 переводит устройство для записи вектора начальных значений неизвестных переменных. Аналогично процедуре ввода коэффициентов целевой функции выполняется процедура ввода вектора начальных значений неизвестных переменных, которые заносятся в группу регистров 7 (wf+2)-ro вычислительного блока 5. Затем в группы регистров 7 ()то вычислительных блоков IJ построчно заносятся значения коэффициентов матрицы () и значения правых частей {Ь ) . После записи исходной информации устройство по команде блоков ввода-вывода 1 и уравновешения k переходит к решению системы алгебраических уравнений или задачи линейного программирования. Итерационный процесс решения начинается с вычисления начальных значений вектора невязки вектора градиента (индекс в скобках указывает номер итерации). Вычисления вектора невязки i осуществляются в (l+vyt)-M вычислительных блоках 5 параллельно и независимо,дострочно по формуле f.)-. ia-X-) jz. . элемент начального вектора невязки; )((р) - элемент начального вектора неизвестных переменных; - коэффициент исходной матрицы;Ь - элемент вектора правых частей. По команде блоков ввода-вывода 1 и уравновешивания k по одному значению переменных переводятся из (и7+2)-го вычислительного блока 5 через блок ввода-вывода 1 в регистры 36, а значения коэффициентов матрицы групп регистров 7 в регистр 38 арифметико-логических узлов 6 .()-го вычислительных блоков 5, где происходит .их умножение. Операция умноксения осуществляется путем анализа блоком уравновешивания k значений разрядов переменных X с последующим суммированием значений коэффициентов. После завершения процедуры умножения ayj и по команде блока уравновешивания 4 значения переменных Х переводятся из i-тых в ( + )-ые вычислительные блоки 5, а из групп регистров 7 в арифметико-логические узлы 6 значения сле дующих коэффициентов а- и процедура умно)чения повторяется. Результаты у|Мно ; ения суммируются с величиной Ь и заносятся в группы регистров J, Вычисление вектора завершается занесением в группы регистров 7 значений , а значения функций Sgn блок уравновешивания 4. Затем блок уравновешивания k переводит устройство для вычисления начальных значени вектора градиента, элемент которого вычисляется по формуле (о) W j 1 ,п 1 при / О , где Sgn ) О при О. Вычисление элементов начального значения вектора градиента осуществляется в вычислительных блоках По команде блока уравновешивания i значения коэффициентов а. со знаком соответствующим его знаку, умноженно му на знак функции Sgn ff,поступают из группы регистров 7 в арифметикологические узлы 6, где происходит суммирование со значениями коэффициентов a,j, поступающими на их входы Данная процедура завершается по команде блока уравновешивания 4 занесе нием значений элементов начального вектора градиента в группу регистров 7 (т+1)-го вычислительного блока 5 и значений функций в блок уравновешивания Ц, где функция . Блок уравновешивания k фикси 5ует завершение вычисления начальных значений гХ.( )и переводит устройство в подре им итерационного решения. 1йтерационный процесс решения наминается с-вычисления приращения невязки по формуле ) ,- .-гг. .,лх,,н,. -hTtSgnV/ i , j 1,n - п ращения;j-тогоэлементе вектора пере менных на к-том шаге итерационного процесса; шаг приращения j-того элемента вектора переменных. По команде блока ввода-вывода 1, дока синхронизации 3 и блока уравно вешивания k в ( Т + уй}-том вы числительных блоках 5 из групп регистров 7 в арифметико-логические узлы 6 передаются коэффициенты а., где выполняется процедура умножения на ikXf, которая осуществляется путем многократного суммирования коэффициентов н-.. Величины приращений Л Х), paBHfcie шагу приращения 4ii,. и знаки приращений , противоположные знак;зм элементов вектора градиентаг V/(iV устанавливаются в блоке уравновешивания 4. Полученное произведение по команде блока уравновешивания переводится в группы регистров 7- Затем передаются следующие коэффициенты а vj из групп регистров 7 в арифметикологические узлы 6, в которых выполняется умнонение этих коэффициентов на приращения полученные произведения .д-Х. суммируются с предыду Л . Завершение вычисления щими а. приращения вектора невязки л . анализируется блоком уравновешивания А, который переводит устройство для решения новых значений вектора переX и невязки . менних В1.1числение новых значений векторов U хСк и Е выполняются суммированием предыдущих значений векторов Х и . с приращениями т.е. Xf , j (Т;, Вычисление новых значений векторов выполняется в (1+ш)-их вычислительных (5локах 5, а вектора - в (т+2)-м вычислительном блоке 5 .параллельно. После выполнения данных вычислений . значения элементов заносятся в группы |эегистров 7 (1 +гп)-го вычислительных блоков 5, значения - в группу регистров 7 (гп+2)-го вычислительного .блока 5, а значения бункций . Sgn f в блок уравновешивания t, который переводит устройство для вычисления вектора градиента V/ . Процедура вычисления вектора градиента выполняется аналогично процедуре вычисления начального вектора градиенTa, Блок уравновешивания h анализирует завершение вычисления вектора градиента V 1, значение которого заносится в группу регистров 7 (m+l) -го вычислительного блока 5, фиксирует значения функций ВдпГЛТи переводит устройство для выполнения следующего шага итерационного процесса, ко119то|5ый начинается с вычисления приращения вектора невязки. При решении задач Л11 нейного программирования на каждом шаге итерационного процесса после вычисления вектора невязки t блок уравновешивания анализирует значения вектора невя, переменной . По результатам этого анализа блок уравновешивания k выдает команды вычисления VK) VX по формуле градиента вектора ,1,) ги ()v(J,xr,;;,.,;S,H« где 5 °-Т4 1 i Л O-K/ju.XlivO i (0«/ги. Если на данном итерационном шаге зна чения элементов векторов невязки С и переменной удовлетворяют необзначение эл ходимым ограничениям, то вычи ментов вектора градиента v ляется по значению коэффициентов целевой функции С) . Если значение векторов невязки Е. и переменной не удовлетворяют необходимым ограничениям, то значения элементов градиента вычисляются аналогично вычислению значений элементов вектора градиента для систем алгебраических уравнений. Итерационный процесс решения завершается по команде блока ввода-вывода 1 и блока уравновешивания 4. Блок уравновешивания k на каждом шаге итерационного процесса анализируе критерии остановки итерационного про цесса. Если эти критерии не выполняются, то итерационный процесс продолжается. В случае, если критерии остановки выполняются то блок уравновешивания выдает на блок ввода-вывода 1 сигнал остановки итерационног процесса, который инициирует сигналы остановки во всех микроавтоматах. По команде блока ввода-вывода 1 блок уравновешивания k управляет пер дачей по одному значению результатов решения по цепочке вычислительных бл ков 5 на вход блока ввода-вывода 1 , который далее передает эти значения на блок индикации 2. Остановка итерационного процесса и вывод результа тов решения может также осуи4ествлять ся с клавиатуры 11 при автономном ис пользовании устройства или по команде узла управления 15 при системном использовании устройства. 2 Вычислительными блоками 5 управляет блок уравновешивания if, который на формирователь адреса 8 выдает управляющие команды, а формирователь адресов 8 преобразует эти команды. С вы-, хода формирователя адресов 8 на группу регистров 7 поступают команды адреса ячейки памяти Запись или Чтение, а на арифметико-логический узел 6 - команды операций. Группа регистров 7 по команде формирователя адресоа 8 может записывать информацию, поступающую с ариф/четико-логического узла 6, и выдавать информацию на арифметико-логический узел 6 или на блок уравновешивания Ц, Арифметико-логический у;зел 6 по командам, поступающим с формирователя адресов 8, выполняет команды над информацией, поступающей на вход вычислительного блока 5 или с группы регистров 7. Результаты выполненных операций выдаются на выход вычислительного блока 5 или на вход группы регистров 7. Последний вычислительный блок 5, кроме арифметикологического узла 6 и группы регистров 7, имеет счетчик 9 и, регистр адресов 10, включенных последовательно. Управление работой арифметико-логическим узлом 6 осуществляется непосредственно с блока уравновешивания . Задание выполнения операции Запись или Чтения в группе регистров 7 также осуществляется блоком уравновешивания А, а адресацию определяют счетчик 9 и регистр адресов 10. На вход счетчика 9 с блока уравновешивания k поступают счетные импульсы. Счетчик 9 задает команду адреса ячейки памяти в группе регистров 7, которая хранится в регистре адресов 10 до поступления следующего импульса на вход счетчика 9. Арифметико-логические узлы 6 предназначены для выполнения арифметических и логических операций и имеют одинаковую структуру. Арифметико-логический узел 6 работает следующим образом. Операнды, поступающие на вход арифметико-логического узла 6, размещаются в одном из регистров 36 или 37. Для совмещения выполнения текущей операции в арифметико-логическом узле 6 с выборкой операндов из группы регистров 7 служит регистр 38. После выполнения операции операнд заносится в регистр 35. Операнды с регистра 37 непосредственно, а с регистра 36 через мультиплексор 39, поступают на входы сумматора 3, который выполняет операцию над операндами. Результаты операций хранятся в регистре 35.В регистрах 35 и 36 осуществляется необходимый сдвиг. Вывод результатов вычисления на группу регистров 7 осуществляется через мультиплексор . Вход арифметико-логиче.ского узла 6 совмещен с выходом . сумматора З, а выход - с входом сумматора 3. Управляющие сигналы поступают с блока уравновешивания f и на все элементь арифметико-логического узла 6. по шине 5.

Блок ввода-вывода 1 работает следующим образом.

Шины составляют внешний интерфейс для каналом вводавывода. Это прямая информационная шина 47, адресная шина 48, управление 9. По шине 50 информация с блока ввода-вывода 1 через мультиплексор ввода 13 ,и выходного регистра 17 поступает на входы вычислительных блоков 5. Шина 51 используется для передачи синхроимпульсов с генератора 16 и управляющего слова из регистра 19 в блок синхронизации 3 и блок уравновешивания Ц. По шине 52 информация с выхода последнего вычислительного блока 5 поступает на выходной регистр 20, а по шине 53 информация поступает на блок индикации 3. По шине S сигналы с блока уравновешивания k поступают на узел управления 15. Шины 49-5 образуют внутренний интерфейс устройств. При ручном вводе посредством клавиатуры 11 набирается вводимое число и его адрес и выдается сигнал переключения мультиплексоров 1 и I на ручной режим ввода. В узел регистров 19 через мультиплексор I и память 18 вводится адресная информация. ВводигЮе число с клавиатуры 11 через-преобразователь 12, мультиплексор 13 и входной регистр 17 поступают на шину 50. При автоматическом режиме ввода мультиплексоры 13 и 14 переключаются на шины 7 и Л8 соответственно. Информация данных с шины 47 через мультиплексор 14 и память 18 поступает в узел регистров 19 а с узла регистров 19 передается на шину 51. Управление работой блока вводавывода 1 осуществляет узел управления 15 и генератор синхро-импульсов 16. Выводимая информация по сигналам узла управления 15 и генератора синхро-импульса 16 с шины 52 через выходной регистр 20 поступает либо на преобразователь 22 и далее на шину 53 либо через коммутатор 21 на шину 46. Остановка итерационного процесса и вывод результатов решения осуществляются по команде узла управления 15. При автономном использовании предлагаемого устройства сигналы остановок итерационного процесса поступают со всех микроавтоматов блока уравновешивания 4 по шине 54 на узел управления 15, который через мультиплексор 1 память 18 и узел регистров 19 выдает команду вывода результатов на блок уравновешивания 4 через шину 51. При системном использовании устройства сигнал остановки итерационного процесса поступает на шину 49. Остановка итерационного процесса может осуществляться также клавиатурой 11. Мультиплексор 23 по команде блока управления 15 осуществляет передачу информации с последнего на первый вычислительные блоки 5 по шине 50.

Все микроавтоматы блока уравновешивания 4 имеют одинаковую структуру и работают следующим образом.

Сигнал с выхода блока ввода-вывода 1 по шине 55 через коммутатор 31 и элемент ИЛИ 29 запускает счетчик 28 который устанавливает номер команды. Сигнал номера команды с выхода счетчика 28 через дешифратор 27 поступает на вход памяти 2б. Память 26 выдает На вычислительный блок 5 по шине 5б сигнал кода операции, выполняемой вы4ислительным блоком 5 а на коммутатор 30 номер выполняемой операции. Узел логических условий 24 по шине 57 принимает с вычислительного блока 5 сигнал результатов выполнения операции и анализирует их.

С выхода узла логических условий 24 сигналы поступают на вход элемента И 26 и через коммутатор 30 и элемент ИЛИ 29 на второй вход сметчика 28. Счетчик 28 по команде элемента ИЛИ 29 и элемента И 25 устанавливает следующий номер подпрограммы. Сигнал с выхода счетчика 28 через дешифратор 27 поступает на вход памяти 2б, которая выдает на шину 54 сигнал кода следующей операции и адрес памяти. При подаче с памяти 2б на шину 5б сигнала кода операции схема сравнения 32 сравнивает данный с сиг15 96 налом подаваемым на .вход схемы сравнения 33 с шины 55. Если код операции является последним в подпрограмме, то схема сравнения 33 выдает на узел логических условий 2k команду перехода анализа следующих условий. После выполнения каждого шага итерационного процесса узел логических условий 2k анализирует выполнение критериев остановки итерационного процесса. Если критерии не выполняются, то узел логических условий 2 выдает на элемент И 25 и элемент ИЛИ 30 сигнал о переходе к следующей операции и итерационный процесс повторяется. Если критерии выполняются, то узел логических условий 2k выдает сигнал на блок ввода-вывода 1 по шине 58. Блок ввода-вывода 1 выдает по шине 55 на элемент И 33 сигнал остановки итерационного процесса. Элемент И 33 переключает счетчик 28, который через дешифратор 27 выдает сигнал на память 2б. Память 26 по шине 56 выдает на вычислительный блок 5 команды подпрограммы вывода информации. В память 2б последнего микроавтомата записаны только команды кода операции, выполняемой арифметико-ло; гическим -узлом 6 и группой регистров / . f (т+3)-го вычислительного блока 5. Адг рее ячейки памяти в группе регистров 7 (п-нЗ)-го вычислительного блока 5 определяется счетчиком 9 и регистром 10 при подаче с (т+3)-го микроавтомата блока уравновешивания k по шине 59 с элемента 33 счетчика импульсов. Преимущества предлагаемого устройства в сравнении с известными ранее обусловлены тем, что введение в уст ройство (т+3)-го вычислительного блока, п состав которого входят счетчик и регистр адресов, соединенных последовательно, позволяет расширить функциональные возможности предлагаемого устройства в части ре1|;ения задач линейного программирования. Предполагаемый экономический эффeкt от использования вычислительных комплексов, частью которых является предлагаемое устройство, составляет 83,0 тыс,руб. в год, а срок окупаемости D,k года. . Формула изобретения 1. Устройство для решения системы алгебраических уравнений, содержащее блок ввода-вывода, блок синхронизации, блок уравновешивания и () 2 .16 вычислительных блоков, (где т - число уравнений), причем управляющий вход блока ввода-вывода соединен с (.Wi+ )-м выходом блока уравновешивания, выход синхронизации блока ввода-вывода соединен с входом блока синхронизации, выход которого соединен с входом синхронизации блока уравновешивания, информационный выход блока ввода-вывода .соединен с информационным входом первого вычислительного блока, первый выход I-ro (где i 1 ,2,.. , ,mf-3) вычислительного блока соединен с информационным входом {. +1)-го вычислительного блока, второй выход i-ro вычислительного блока соединен с i-M информационным входом блока уравновешивания, i-й выход которого соединен с управляюи(им входом 1-го вычислительного блока, о тли чающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения решения задач линейного программирования, в устройство введен (т+3) вычислительный блок, причем информационный вход этого блока подключен к первому выходу (гт+2)-го вычислительного блока, управляющий вход которого соединен с (гп+3)-м выходом блока уравновешивания, первый i I-т. ... ВЫХОД (.уп+3)го вычислительного блока соединен с информационным входом блока ввода-вывода, второй выход которого соединен с уун-3 м входом блока уравновешивания . 2. Устройство по п. 1, о т л и чающееся тем, что (П1+3)й вычислительный блок содержит арифметико-логический узел, группу регистров Данных, регистр адресов и счетчик адреса,причем первый информационный вход арифметико-логического узла является информационным входом блока, второй информационный вход этого узла соединен с выходом группы регистров данных, который является также вторым выходом блока, выход счетчика адресов соединен с входом регистра адресов, выход которого соединен с информационным входом группы регистров данных, выход арифМетико-логического.узгГа является первым выходом.вычислительного блока, вход счетчика адресов, управля-ющие входы арифметико-логического узла и группы регистров данных подключены к управляющему входу блока.

1796670218

Источники инйормации,2. Авторское свидетельство СССР

.принятые во внимание при экспертизе по заявке I 2753317/18-2t,

1. Авторское свидетельство СССР кл. Г, Об F 15/32, 21.02.79 (прото№ , кл. G Об F 15/32, 1977. .тип;..

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для реше-Ния СиСТЕМ АлгЕбРАичЕСКиХ уРАВ-НЕНий | 1979 |

|

SU798863A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Процессор | 1989 |

|

SU1725224A1 |

| Устройство для решения уравнений математической физики | 1986 |

|

SU1363260A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Цифровой интерполятор | 1987 |

|

SU1460726A1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1543232A1 |

Фиг.

fiO

f f

f

35

36

966702 fil

4J

f f

liS

37

n

Фиг,

Авторы

Даты

1982-10-15—Публикация

1981-01-12—Подача