(54) ЦИФТОАНАЛОГОВАЯ СИСТЕМА

ДЛЯ РЕГИСТРАЦИИ И СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ИНФОРМАЦИИ

1

Изобретение атносится к вь1чис1штельной технике и может быть использовано в любой области, где требуется производить сбор и статистическую обработку данных, в частности, при автоматизации экспериментальных исследований.

Известно устройство для регистрации и статистической обработки информации, содержащее преобразователь информации, подключенный выходом к оператгвному запоминающему устройству, цифровой вы1а|слительный блок, связанный с оперативным запоминающим устройством и соединенш 1Й с ними блок управле1ШЯ, а также блок выходных устройств. Это устройство предназначено для регистрации разг физических величин при экспериментальных исследованиях и для их последующей статистической обработки в арифметическом устройстве по жесткой программе 1.

Наиболее близкой к предлагаемому по технической сущности является система, содержащая микропроцессор, связанный с оперативньш упоминакнцим устройством и через аналогоцифровые пpeoбpaзoвateли с датчиками входных величин, контролер и устройство вывода 2.

Данную систему можно перестраивать для различного типа датчиков, однако перестройка не является оперативной. Регистрация только унифицированных входных снгналов, связанных с измеряемой величиной линейной зависимостью, сужает функциональные возможности и уменьшает эффективность использования системы. Необходимость запоминания для последующего

10 анализа всей входной информации, отсутствие ее разметки и привязки к условиям эксперимента снижают быстродействие системы и точность обработки данных. Быстродействие устройства в неМеньшей мере зависит также и от

15 принятого способа обработки информации. В известной системе информация обрабатьшается только в цифровой форме.

Целью изобретения является повышение быстродействия, точности и увеличение гибкости

2Q структуры.

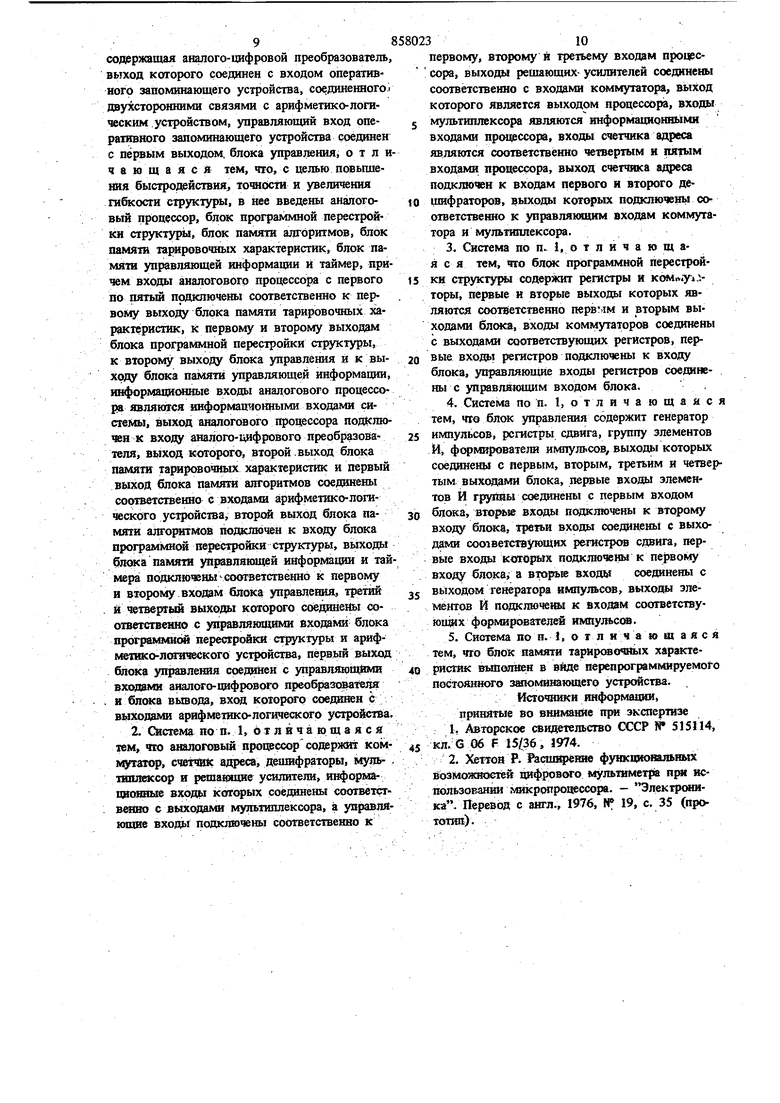

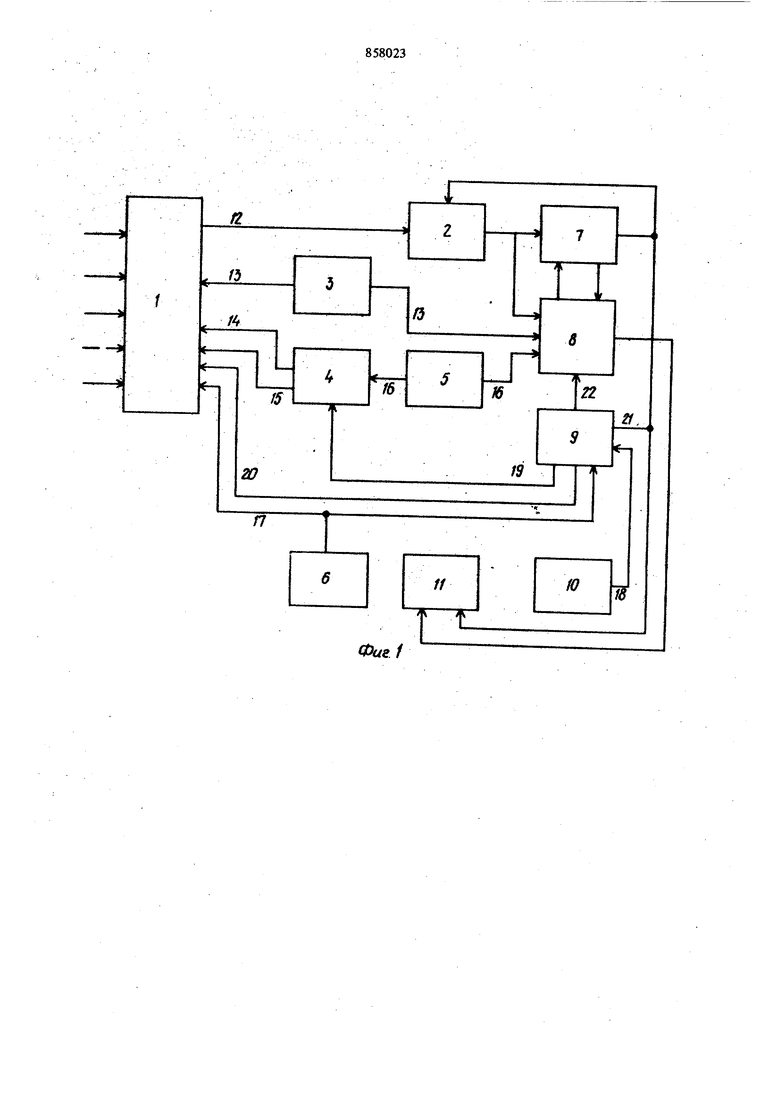

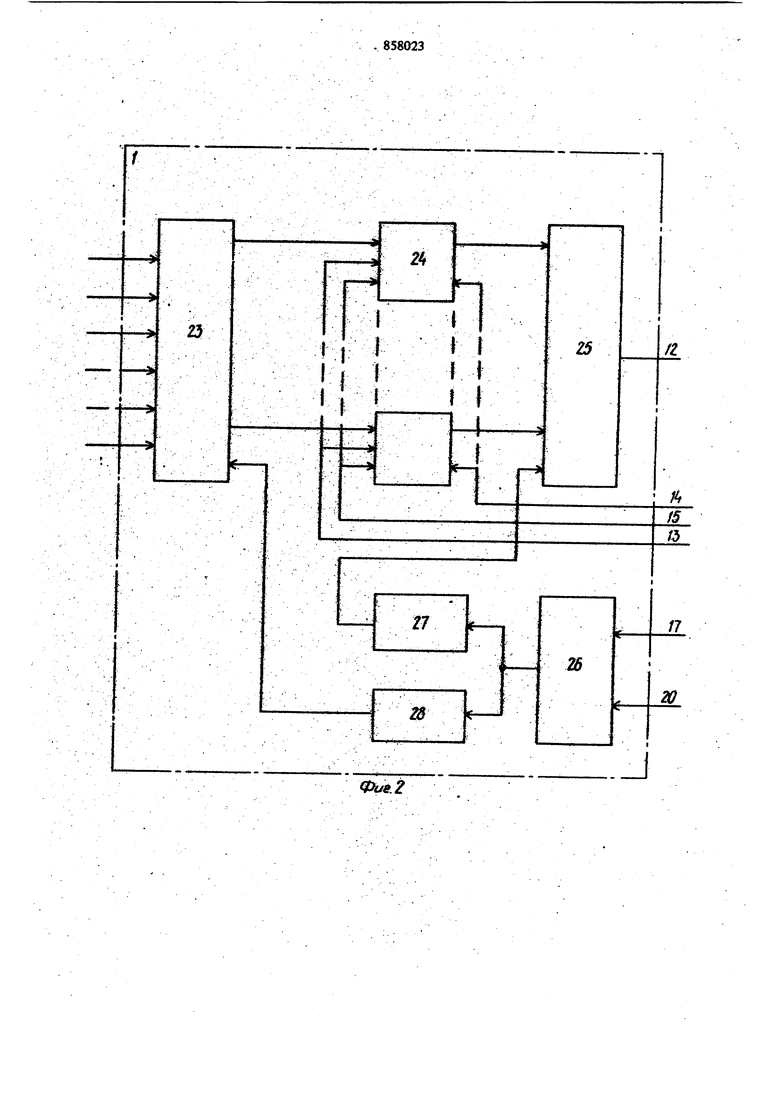

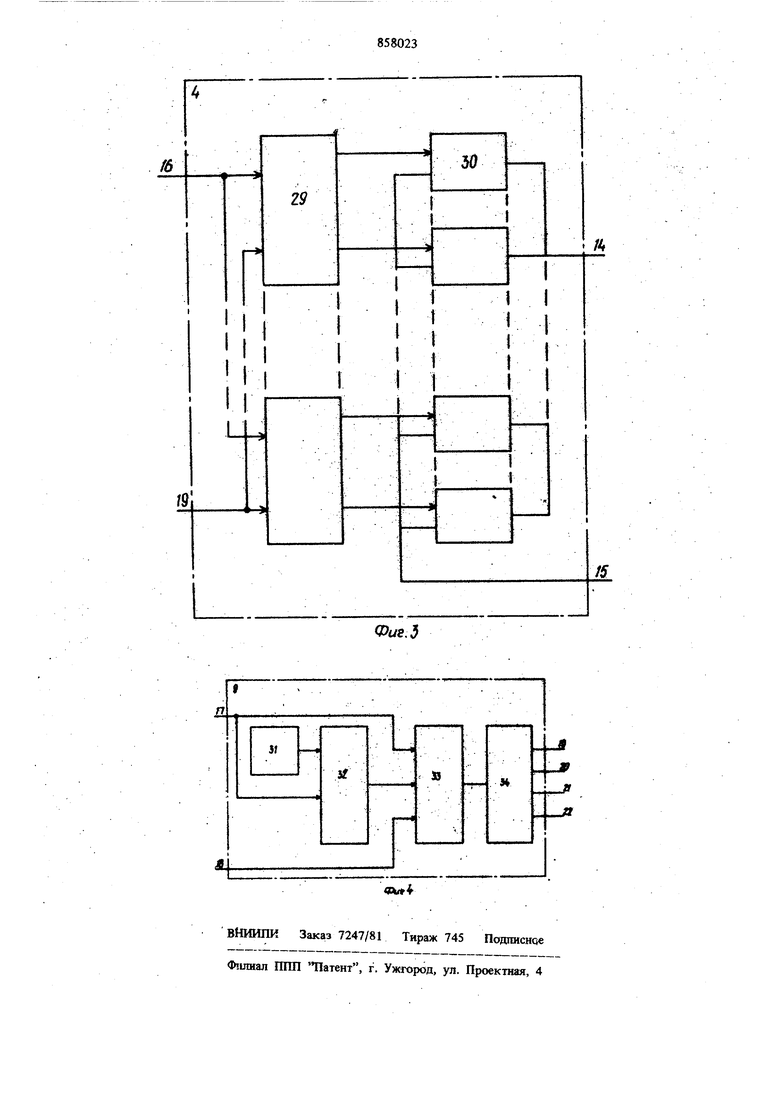

Поставленная цкль достигается тем, что в систему, соде{}жащую -аналого-цифровоый преобразователь, выход которого соединен с вхо3дом оперативного запоминающего устройства, соединенного р аутоуюротшмя связями с арифметико-логидаским устройстйом, управляющий вход оперативного запоминающего устройства соединен с первым выходом блока управления, введены аналогсжый процессор, блок програм(иной перестройки структуры, блок памяти алгоритмов, блок памяти таркровочных характеристик, блок памяти управляющей информдщш,. таймер, причем входа: аналогового профссора с первого по пятый подключены соответственно к первому выходу блока памяти тарировочных характеристик, к первому и второму выходам блока программной перестройки структуры, к второму выходу блока управления и к выходу блока памяти управляющей информации, информационные входы аналогового npogjeccopa являются информационными входами системы, выход аналогового процессора подключен к входу аналого-цифрового преобразователя, выход которого, второй выход блока памяти тарировйчньк характеристик и первый выход блока памяти алгоритмов соединены соответственно с входами арифметико логического устройства, второй выход блока памяти алгоритмов подключен к заходу блока программной перестройки структуры, выходы блока памяти управляющей информации и таймера подключены соответственно к первому И второму входам блока управления, третий и четвертый выходь которого соединены соответственно с управ ЛЯЮЩИШ1 входами блока Ьрограммной перестройки структуры и арифметико-лопрвского устройства, первый выход блока управления соединен с управляющими входами аналого-щ рового преобразователя и блока вьюода, вход которого соединен с выходом арифметеко-логического устройства, а также тем, что аналоговый процессор содержит коммутатор, счетчик адреса, Дешифраторы, мул типлексор, решающие усилители, информационные входы которых соединены соответственно с выходаАШ мультиплексора, а управляюцще входа подключены соответственно к первому, второму и третьему входам процессора, выходы решаияцих: усилителей соединены соответственно с входами квилмутатря выход которого этляется выходом процессора, входы мультшщексора являшся информационными входами пр(щеосора, входа счетчика адреса являются соответственно чеетвертьш и пятым входами процессор, выход счетчика адреса подключен к входам шрвого и второго дешиф раторов, выхода1 которых подключень соответ стенно к управляющим входам коАЛи утатора и мультиплексора, а такяф тем, что блок программной перестройки сгрукт5фы содержит регистры и коммутаторы, первые и вторые выходы которых являются соответственно первы И BTopbnvi выходами блока, входы коммутаторов соединены с выходами соответствующих регистров, первые входы регистров подключены к входу блока, управляницие входы регистров соединены с управляющим входом блока, а также тем, сто блок управления содержит генератор илтульсов, регистры сдвига, группу элемеотов И, формирователи икшульсов, выходы KOTopbtx соединены с пер1вым, вторым, третьим и четвертым вьисодами блока, первые входы элементов И группы соединены с первым входом , вторые входы подключены к второму входу блока, третьи входы соединены с выходами соответствующих регистров сдвига, первые входа котфцх подключены к первому вколу блока, а вторые входы соединёнь с выходом генератора импульсов, элементов И подключены к входам соответствующих формирователей импульсов, а также тем, что блок памяти тарированных характерней тик выполнен в виде перепрограммируемсго постоянного запоминающего устройства. На фиг. 1 представлена блок-схема системь ; на фиг. 2 - схема аналогового процессора; на фиг. 3 - схема блока программной перестройки структу|и 1; на фш. 4 схема блока управления. Схема включает аналоговый процессор 1, аиа-пого-цифровой преобразователь 2 (АЦП), блок 3 памяти тарировочнь Х характеристик блок 4 программной перестройки структуры, блок 5 памя-га алгоритмов, блок 6 памяти управляющей информации, оперативное за омш{ающее устройство (ОЗУ), арифметико-логическое устройство (АЛУ) 8, блок 9 управления, таймер 10, блок U вывода, дапи 12-22 связи, мультиплексор 23, рещаюадае усилители 24, коммутатор 25, счетчик 26 адреса, дешифраторы 27 и 28, регистры 29, коммутатс Ж 30, генератор 31 импульсов, регистры 32 с аэвига, группу элементов И 33, форлсирователи 34 импульсов. Аналоговый процессор Г (фда. 2) осуществляет сопряжение устрг%тва с nepBK i&iAra измерительными преобраэовзтелААш инфс пиющю (дагшками) и производит ее предаарттельную математическую обработку. Рещаюише усилители обеспечивают необходимые преобразовгошя сигналов за счет isstaeнешя параметров цепей их обратшлх связей. Блок 3 вьшолнен в виде перепрограммируемого электричежим мешком полущюводаиковрго nocTOHHHcffo запоминающего ус1{ ойства, а блок 5 в виде полу1 вошшкового постоянного запоминающего устройства, программируем(-о выжиганием. Блок 6 аредсгавляет управляющую память, инфсфма1шя из которой выдается в соответствии с нажатыми клавнщакш пульта

оператора. В качестве арифметико-логического устройства 8 может использоваться универсальный микропроцессор с микропрограммно или жестко управляемой обработкой информации.

Блок 9 управления (фиг. 4) предназначен для выработки сигналов временной диаграммы требуемой для отработки набора команд устройства.

Блок 11 включает в себя стандартные устройства отображения и выдачи инфор,у1ации, к примеру, индикационное табло и цифропечать.

Работает система следующим образом.

БЛОКИ 6 и 9 и таймер 10 обеспечивают задание и отработку программы измерений в зксперименте в реальном масштабе времени, а также выработку ряда служебных сигналов. В частности, блок 6 позволяет выбрать число измеряемых каналов и частоту опроса датчиков, а также продолжительность съема данных т.е. время реализации. Осуществляется это путем считывания информации с управляющей памяти блока 6 в соответствии с нажатием клавишами пульта оператора. Так, по этой информации, поступившей по связи 17 на вход аналогового процессора 1, производится одновременно подключение на вход системы группы датчиков, номера которых определяются кодом, установленным в счетчике 26 адреса, и логической функцией, реализуемой дешифратором 28. Временные характеристики программы измерений, задаваемой блоком 6, обрабатываются блоком 9 управления. Информация об изменении программы поступает в блок 9 по связи 17.

Блок 6 позволяет также представить отрезок исследуемой характеристики радом jniacTков, в каждом из которых может быть задано требуемое число циклов измерений и дискретность их повторения. Это дает возможность исключить избыточность накапливаемой информации на участках с плавным юменением параметра, а с другой стороны - выделить один участок на измеряемой характеристике и исследовать его с повышенной дискретностью повторения съема данных. Привязка контролируемых переменных к текущему времени с целью получения полной картины их изменения и, тем самым, повышения точности обработки экспериментальных данных обеспечивается таймером 10. Последний используется в системе для задания и измерения временных интервалов и может быть выполнен в виде счетчика реального времени, работающего от кварцевого генератора.

В зависимости от выработанмых режимов работы системы информация, поступающая с объекта исследования, может непосредственно, либо после предаарительной обработки поступать на блок 11 для регистрации и последующего анализа, использоваться для экотрессанализа в реальном времени и отображения в удобной для восприятия форме на цифровом десятичном табло блока 11 с целью оперативного контроля состояния объекта и, наконец, подвергаться статистической обработке. Последняя включает построение функции распределения случайных велнвдн, вычисление таких статистических характеристик распределения, как математическое ожидание, дисперсия, стандартное отклонение, размах, коэффициент вариации и др., а также осуществляет линейное оценивание параметров статистической модели. Предварительная обработка экспериментальных данных включает расшифровку сигналов датчиков их масштабирование, тарировку, вычисление по исходным параметрам неизмеряемых параметров и формирование массивов данных. В результате этого системой помимо статистической обработки данных производится концентрация исходной информации, что способствует ее передаче на другие вычислительные центры в случае, если настоящая система используется на борту объекта исследования (подвижном объекте).

Требуемый режим съема и регистрации данных, алгоритм их обработки обеспечиваются совокупностью блоков 3-6. При этом блок 4 программной перестройки структуры и блок 5 памяти алгоритмов производят перестройку конфигурации системы программным путем применительно к алгоритмам и типам выполняемых задач. Достигается это выбором отдельных функциональных элементов или их групп из числа узлов (блоков) цифровых и аналоговых блоков системы и установлением между ними требуемых связей. Так, блок 4 программной перестройки структуры по информагош, занесенной по связи 16 с блока 5 памяти алгоритмов, управляет решающими усилителями 24, которые выполнены на линейных, интегральных схемах. С помощью различных цепей обратной связи решающих усилителей, изменяемых посредством элементов коммутации и управления, легко получать разнообразные перюдаточные функции, соответствующие различным математическим операциям: суммированию, итгегрирова1нию, умножению на постоянный коэффнциetrr и др. При соответствующей нелинейной обратной связи рещающие усилители 24 дают возможность производить нелинейные преобразования сигна та, что соответствует нелинейным математическим операциям. Блок 4 программной перестройки структуры подключает или отключает цепь обработки аналоговых сигналов к отдельным узлам аналогового процессора 1, изменяет тип обратной связи решающих усилителей и ее величину, а также режим их рабо78ты (к примеру, задание начальных условий, итегрироваше, хранение информации и др.) Запись кода, соответствующего требуемой конфигурации системь и режиму ее работы, в ретнс ы 29 блока 4 производится по сигналу от блока 9 управления. После того, как сигналы с мультиплексора 23 от группы датчиков нормализуются (непрерывнье сигналы подвергаются ряду преобразований, вызванных необходшлостью их фильтрации, сглаживания, приведения к стандартнр-j му уровню и Щ).) и пройдут Определенную ма тематическую обработку в процессоре 1, они поступают на коммутатор 25. Последний обес.печивает подключение на вход АДП 2 одного из выходов усилителей 24. Управление ком1йутатором 25 осуществляется счетчиком 26 адреса и дешифратором 27. С выхода АЦП 2 дискретные сигналы, в зависимости от приняTtWo режима регистрации и обработки зксиеримешгашьных данных, поступают в оперативное запоминающее устройство 7 или непосредственно в АЛУ 8, Обработка поступающих на вход системы сигналов в соответствии с тартфовочными характернстиками датчиков также производится в цифровой и аналоговой форме. При этом взаимодетствне процессора 1 и блока 3 выражается в том, что по командам, поступающим с блока 3 на элементы управления и коммута цин решающих усилителей 24, осуществляется изменение наклона градуировочных кривых и смещение нулевого уровня первичных измерительных преобразователей. Дальнейщая обработка провощпся цифровыкш блоками (жстемы по дащшм, поступающим навход АЛУ 8 с АЩ1 2 и блока 3 памяти тарировочных харак теристик. В случае поДключегаш к системе час тотных датчиков осуществляется измерение ие ркот колебаний частотно-модулированного сиг нала и производится его перевод в цифровую по тартровочной зирактеристике. Требуемое для зтого формирование времешаис ин тервалов осуществляется таймером 10. . - . Сочетшие цифровой и аналоговой формы представления я обработки информации способ ствует повьпоегаио эффективности вычисшпель ных процессов, позволяет более полно )щовлет ворить тр ова1шя высокого быстродействия и точности, обешечивает гибкость структуры системы и упрощает программирование рещаемых зйдач. При этом также саижаются аппарат шые затраты, что приводат к увеличению надежности и ук1енш1еяшо габаритов, веса и стоимости. С другой стороны, наличие в сис1еме блока 5 памяти алгоритмов позволяет использовать шеративное поминающее устройство 7 только даю хранения текущей информа ции и часто изменяемых пользователем констант. Этим достигается уменьщение объема шеративного запоминающего устройства 7. Кроме того, использование жесткого программирования обеспечивает высокую готовность системы к работе и ее обслуживание. Структура рассмотренной системы по сравнению с известными системами и устройствами такого же рода дает следующие преимущества:а)возможность подключения системы к датчикам любого типа и с любым уровнем выходных сигналов вне заввсямости от их тариpoB04iQ ix харзкте{кнстик; б)высоку гибкость структуры шстемы, обеспечиваемую перестройкой ее конфигурации программным путем применительно к алго{жтмам и типам выполняемых задач, в)высокое быстродействие и точность обработки информации, достигаемые за счет выполнения системы по цифро-аналоговой струкtype, а также вследствие управления режимами съема данных, разметки и концентрации исходной информации. Кроме того, сочетание цифровых и аналоговых принцщов обработки ияфЬртции обеспечивает простоту ее С(щряя«нвя с обьектом и высокую эффективность вычислительных процессов при обработке и интерпретации в реальном масштабе времени сигналов из внешней среды. Структура системы шособсгвует также значительному упрощению математической и технической экошуатадаи, так как отпадает необходимость В устройствах ввода программ н в yrvffiiuQ пользователя програмьшровать задачи. В результате, помимо предоставления удобств пользователю в общении с шстемой, повышается также надежность и допускается зксилуатация, за иослючекнем врофииактичесжнх ра-. бот, без специального обслуживающего персонала. Все эти достоиястоа системы предсяредепяют преилотдестве1шую облйяь его применения - автоматизахщя экшерименташаых исследований, проводимых при натураых ишытавиях объектов (бортовые шстейы) я в усаоааях. цехового производства, где фахтс ы, как небольшие: ra@a:pHTbtj вес, wataa потребляемая моншость, простота обслуживания и высокая надежность приобретают пе1гос1епенную роль. Формула изобретения. 1. 1Ънфроаналоговая сис-кма для регистрации и статистически обработки информация.

содержащая аналого-цифровой преобразователь выход которого соединен с входом оперативного запоминающего устройства, соединенного двухсторонними связями с арифметико-логическим устройством, управляющий вход оперативного запоминающего устройства соединен с первым ВЫХОДШ1. блока управления, отличающаяся тем, что, с целью повьппешя быстродействия TowoctH и увеличения гибкости структуры, в нее введены аналоговый процессор, блок программной перестройки структуры, блок памяти алгоритмов, блок памяти тарировочных характеристик, блок памяти управляющей информации и таймер, причем входы аналогового процессора с первого по пятый подключены соответственно к первоыу выходу блока памяти тарировочных характеристик, k первому и второму выходам блока программной перестройки структуры, к второй выходу блока управления и к выходу блока памяти управляющей информации, информационные входы аналогового процессора являются информационными входами системы, выход аналогового процессора подключен к входу анапого-дифрового преобразователя, выход которого, второй .выход блока памяпг тарировочных характеристик и первый выход блока памяти алгоритмов соединены соответственно с входав ш арифметико-логического устройства, второй выход блока памяти алгоритмов подключен к входу блсяса программной перестройки структуры, выходал памяти {)авлякш(ей информации и таймера подключены соответственн6 к первому и второму входам блока управления, третий и четвертый выходы которого соединены соответственно с 11равляк щими входакга блока программной перестройки структуры и арифметико-лашческого устройства, первый выход бпока управления соединен с управляющими входами аналого-цифрового преобразователя и блока вывода, вход которого соедижн с выходами арифмеяжо-лопетеского устройства.

2. Система по п. 1, отличающаяся тем, 4fo аналоговый процессор содержит комN atop, счетчщс адреса, дешифраторы, муль- . тшшйссор и решаихдие усилители, инфорго входы котсфых соединены соответстъевяо с выходами мультиплексора, а уяравля ющие входа подключены соответственно к

первому, второму и третьему входам процессора, выходы решающих- усилителей соединены соответственно с входами коммутатора, выход которого является выходом процессо, входы

мультиплексора являются информационнь1 Ми входами прсщессора, входы счетчика адреса являются соответственно четвертым и пятым входами процессора, выход счетчика адреса подключен к входам первого и второго дешифраторов, выходы которых подключены соответственно к управлякяцим входам коммутатора и мультиплексора.

3.Система по п i, о т л и ч а ю щ ая с я тем, 1ГГО блок программной перестройкн CTpjocT sj содержит регистры и ком«.у1 торы, первые и вторые выходы которых являются соответственно первмм и вторым выходами блока, входы коммутатор(ж соединены с выходами соответствующих регистров, первые входа регистров подключень к входу блока, )шравляющие входы регистров соеданены с управляющим входом блока..

4.Система по п. 1, о т л и ч а ю щ а я с я тем, что блок управления содержит генератор

импульсов, регистры сдвига, группу элементов И, формирователи импульсов, выходь которых соединены с первым, вторым, третьим и четвертым, выходами блока, первые входь элемен тов И соед1шены с первым входом

блока, вторые входы подключены к второму входу бл(жа, входы соеданень с выходами соо1ветствующих регистров сдаига, первые входал которых подключены к первому входу блокад а вторые входы соединень с

вь1ходом генератора импульсов, выходы элементов И подклшче1Ш к входам соответствуЮ1ЩХ формирователей няшульсш.

5.Система по п. 1, о г л и ч а ю Ш а я с я тем, что блок памяти тарировоч1й.Х характерисшк выполнен в виде верепрограммируемого постоянного запоминающего устройства.

Источники информа1ши, принятые во внимание при экспертизе

1..Авторское (Жидетельство СССР N 515114, кл.6 06 F 15(36. 1974.

2.Хеттов Р. Распофёвие фзгнкциовалькых ЁозможЯЕОетей ффров о мультвметра нрт использовании лшкропроцессора. - Электршика. Перевод с аетл., 1976, ff 19, с. 35 (прототйк).

ФЬ«.

л

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОАНАЛОГОВАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ И ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2022364C1 |

| Аналого-цифровое вычислительное устройство | 1986 |

|

SU1388913A1 |

| Однородный параллельный процессор | 1978 |

|

SU736107A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006942C1 |

| Устройство для контроля и управления процессом контактной сварки | 1976 |

|

SU656767A2 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| РАДИОЛИНИЯ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2004 |

|

RU2273099C1 |

| ПАРАЛЛЕЛЬНЫЙ ПРОЦЕССОР С ПЕРЕПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1994 |

|

RU2110088C1 |

Авторы

Даты

1981-08-23—Публикация

1979-11-13—Подача