Изобретение относится к технической кибернетике, в частности к устройствам для распознавания знаков.

Известны устройства для распознавания знаков, одно из которых содержит блок сканирования, регистр, первый блок памяти, соединенный с буферной памятью, селектор адреса, детектор обнаружения и второй блок памяти, соединенный с вычислительным блоком 1. Это известное устройство не имеет достаточно высокой надежности распознавания. Наиболее близким к изобретению является устройство, содержащее блок сравнения, соединенный с блоком сканирования, вход которого подключен к генератору импульсов, с блоками памяти, формирования коорди-нат и с элементом ИЛИ, подключенным к первому регистру, мультиплексер, входы которого соединены с блоком формирования координат, подключенным к генератору импульсов, а выход соединен с блоком памяти, первый вычислительный блок, подключенный к блоку формирования координат, вторые регистры, соединенные с блоком формирования координат и с триггером, и блок принятия решения 2. Оно характеризуется также недостаточно высокой точностью распознавания.

Цель изобретения состоит в повышении точности распознавания. В описываемом устройстве это достигается тем, что оно содержит блок стробирования кодов, входы которого соединены с блоками сравнения, формирования координат и с генератором импульсов, а выходы подключены к первому вычислительному блоку и к блоку принятия решения, второй вычислительный блок, соединенный со вторыми регистрами, сумматоры, подключенные к блоку принятия решения, мультиплексеру и к вычислительным блокам, и элемент ИЛИ-НЕ, соединенный

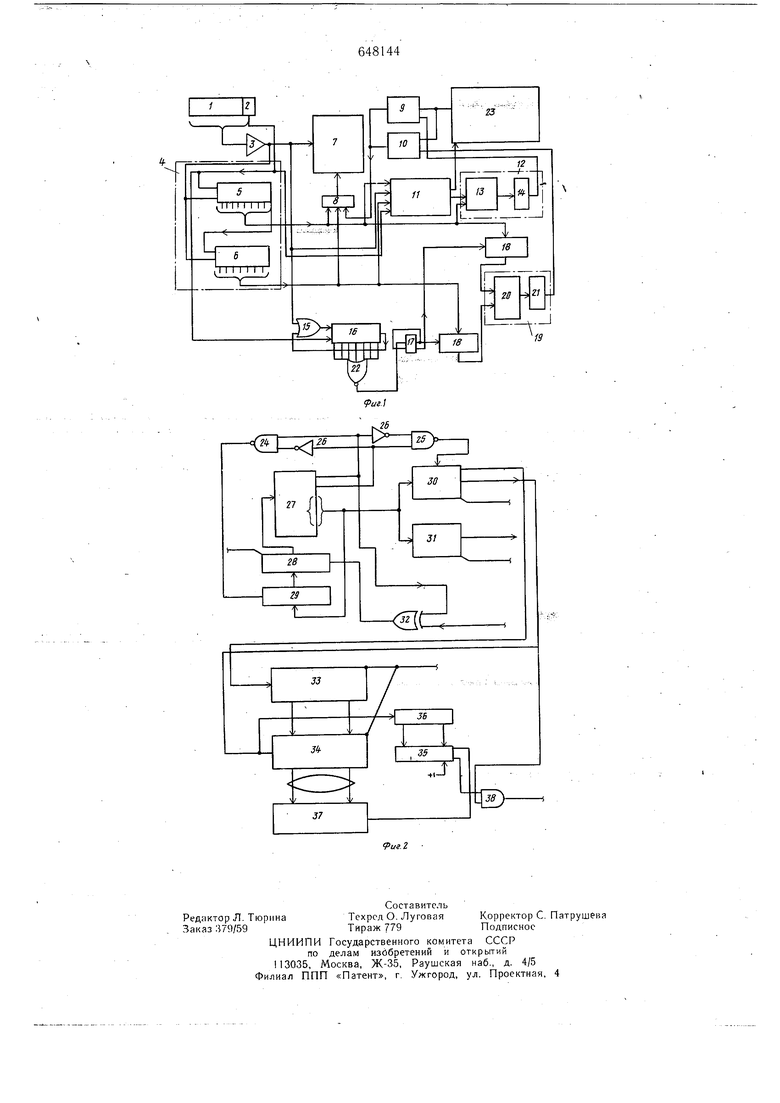

с первым регистром, вход которого подключен к генератору импульсов, и с триггером. Кроме того, в устройстве блок принятия решения содержит узел памяти, вход которого соединен с узлом формирования прирашеНИИ, а выходы подключены к элементам НЕ-И и к инверторам, соединенным с со-, ответствуюшими элементами НЕ-И, к узлу селекции координат и к первому регистру, соединенному с узлом формирования прираш,ений и с одним элементом НЕ-И, узел , . - - 64 сопряжения, подключенный к другому э. ементу НЕ-И, к узлу памяти, ко вторым регистрам, к счетчику и к элементу И, узел сравнения, входы которого соединены со счетчиком, а выход подключен к элементу И и к .узлу фиксации номера знака, и элемент ИЛИ, соединенный с узлами памяти и фор, мирования прираш,ений. На фиг. I представлена, блок-схема описываемого устройства; на фиг. 2 - конструктивное выполнение блока принятия решения.-Устройство включает блок сканирования 1, генератор импульсов 2, блок сравнения 3, блок формирования координат 4, содержащий счетчик колонок 5 и счетчик линеек 6, блок памяти 7, мультиплексер 8, сум.маторы 9 и 10, блок стробирования 11, первый вычислительный блок 12, содержащий узлы разности 13 и деления 14, элемент ИЛИ 15, первый регистр 16 сдвига, триггер 17, вторые регистры 18, второй вычислительный блок 19, содержащий узды разности 20 и деления 21, элемент ИЛИ - НЕ 22 и блок принятия решения 23, содержащий элементы НЕ-И 24 и 25, инверторы 26, узел памяти 27, узел формпро анйя npHpaiueF ifi 28, первый регистр 29, уз.ел солряж ения 30, узел селекции координат 31, элементИЛИ 32, вторые регистры 33 и 34, узел сравнения 35, счетчик 36, узел фиксации номера знака 37 и элемент И 38. Блок сканирования 1 формирует входные сигналы для блока 3 с тактовой частотой, определяемой генератором импульсов 2. Выходные сигналы блока 3 поступают на вход блока памяти 7. Адресные координаты, в свою очередь, обрабатываются двумя счетчиками необработанных адресов, т. е. счетчиком 5 колонок, который подсчить1вает последовательно тактовые импульсы от генератора импул сов 2 и который таким образом, квантует считываемый документ в дискретные ряды, и ечетчиком линеек 6, который подсчитывает наиболее значимый бит счетчика 5. Счетчики 5 и 6 собираются в виде одного адресного входа мультиплексера 8, который создает адресный вход (АДРЕС) для блока памяти 7 с произвольной выборкой. В данной форме содержимое памяти блока 7 образует необработанную матрицу, которая бит за битом и ряд за рядом находится в соответствии с изображением на документе. Любой знак внутри матрицы не привязан, являясь произвольно ра.сположенным в соответствии с отсчетом счетчиков 5 и 6 линий и колонок. Для того, чтобы различить верхний и нижние пределы знака, находятся белые и черные линии, разделяющие два вертикально прилегающих знака или две строки текста.. Это выполняется дальнейшим подключением последовательно выхода блока 3 к одному входу элемента ИЛИ 15, который на своем выходе запускает последовательный вход первого регистра 16 сдвига. Регистр 16 тактируется тем же генератором- импульсов и, таким образом, вводится в синхронизм с блоком сканирования I. Регистр 16 сдвига, кроме того, приспособлен для содержания числа битов, которое равно битовой длительности блока 1. Последовательный выход регистра 16 сдвига возвращается на другой вход элемента ИЛИ 15, образуя петлю рециркуляции, через которую сканирующая последовательность компрессируется по вертикали. Параллельные выходы регистра 16 сдвига собираются на входе элемента ИЛИ-НЕ 22, который запускает делящий на два триггер 17 каждый раз, когда все выходы регистра 16 сдвига являются низкими. Триггер 17 своим выходом стробирует регистр 18 верхних белых отсчетов для подачи на этот регистр одновременно содержимого счетчика линеек 6. Другой выход триггера 17, в свою Очередь, стробирует еще один регистр 18, который запомйнает следуюп.;ий последовательный отсчет ряда чистых колонок со счетчика 5. Регистры 18, в свою очередь, подключаются к узлу фиксации разности 20 блока 19, которая вычитает два отсчета и фиксируетразность отсчетов. Эта раз1тость отсчетов затем делится пополам в узле 21, создавая фактическое.смещение центра линеек в памяти с произвольной 1зы-. боркой. Аналогично исследуются горизонтальные границы знака для определения ширины знака. Однако в отличие от определения границ линеек колонка ограничивает требуемую дополнительную реализацию. Для выполнения этого обобщения блок 11 объединяет выходы блока 3, счетчика линеек 6 и счетчика колонок 5 с генератором импульсов. Блок 11 стробирует соответствующие отсчеты колонок из счетчика колонок 5, при которых появляется полностью чистая колрнка для первого и второго случаев. Она стробируется еще на одном узле разности 13 блока 12, который снова через узел деления 14 создает горизонтальный фактический центр знака. В дополнение один из выходов блока 11 дает сигнал, возникающий во втором случае чистого столбца, который начинает цикл распознавания знака. Само распознавание знака вьшолняется блоком 23, содержащим узел памяти 27, который на. своих выходах выдает биты информации; из них бит поля подается в узел сопряжения 30, узел селекции координат 31и адресный регистр 29. Два бита предназначены для кода команды, предварительно идентифицированной как класс. Аналогично другие биты через соответствующие инверторы 26 собираются на образующих дополнения элементах НЕ-И 24 и 25. Элемент НЕ-И 24 управляет загрузкой регистра 29, тогда как элемент НЕ-И 25 управляет узлом 30.

Таким образом, адресное поле оказывается загруженным либо для создания выходного сигнала, либо следуюш,ей адресной команды.

Регистр 29, в свою очередь, соединяется через узел 28 с адресным входом узла 27. Узел 28 либо создает прираш.ение, либо загружает в соответствии с полярностью ключа исключающего элемента ИЛИ 32, который на своем входе собирает биты, соответствующие элементу изображения в памяти блока и другом биту. Селекция битовых координат выполняется узлом 31, который вырабатывает координаты линейки и колонки для сумматоров 9 и 10, транспонированные центрирующим сдвигом.

Поскольку иногда возможно иметь две или более идентификации знака для одних элементов изображения, вводится дополнительная логика, через которую проверяются все знаки, и распознавание регистрируется только, если идентифицируется один знак. Эта дополнительная логика содержит регистр 33 текущего знака, который получает код знака с узла 30. Когда, в узле 30 вырабатывается код, содержимое этого регистра загружается в регистр 34 распознанного знака. Одновременно счетчик 36 накапливает последовательные сигналы «Конец файла, которые затем сравнив-аются в узле 35, чтобы посмотреть, не возникло ли более, чем одно распознавание. Если это, так, то имеется два похожих знака, и на выходе элемента И 38 возникает подавление. Если распознается только один знак, узел 37 стробируется, чтобы зарегистрировать идентификационный номер знака.

Введение новых блоков и новых конструктивнь х связей позволяет существенно повысить точность распознавания.

Формула изобретения

I. Устройство для распознавания знаков, содержащее блок сравнения, соединенный с блоком сканирования, вход которого

подключен к генератору импульсов, с блоками памяти,формирования координат и с элементом ИЛИ, подключенным к первому регистру, .мультиплексер, входы которого соединены с блоком формирования координат, подключенным к генератору импульсов, а выход соединен с блоком памяти, первый вычиCv итeльный блок, подключенный к блоку формирования координат, вторые регистры, соединенные с блоком формирования координат и с триггером, и блок принятия рещения, отличающееся тем, что, с целью повыщения точности распознавания, оно содержит блок стробирования кодов, входы которого соединены с блоками сравнения,

формирования координат и с генератором импульсов, а выходы подключены к первому вычислительному блоку и к блоку принятия, рещения, второй вычислительный блок, соединенный со вторыми регистрами, сумматоры, подключенные к блоку принятия рещения, мультиплексеру и к вычислительным блокам, и элемент ИЛИ-НЕ, соединенный с первым регистром, вход которого подключен к генератору импульсов, и с триггером. 2. Устройство по п. 1, отличающееся

тем, что блок принятия рещения содержит узел памяти, вход которого соединен с узлом формирования приращений, а выходы подключены к элементам НЕ-И и к инверторам, соединенным с соответствующими элементами НЕ-И, к узлу селекции координат и к первому регистру, соединенному с узлом формирования приращений и с одним элементом НЕ-И, узел сопряжения, подключенный к другому элеме,нту НЕ-И, к узлу памяти, ко вторым регистрам, к счетчику и к элементу И, узел сравнения, входы которого соединены со счетчиком, а выход подключен к элементу И и к узлу фиксации номера знака, и элемент ИЛИ, соединенный с узлами памяти и формирования приращений.

Источники информации, принятые во BIHIмание при экспертизе

1.Патент ФРГ j4o 1524407, кл. G 06 К 9/14, 1975.

2.Патент Японии № 50-18343, кл. 97(7) В41, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Генератор символов | 1989 |

|

SU1633386A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Генератор нормально распределенных случайных чисел | 1984 |

|

SU1226450A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1265782A1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1543442A1 |

| Знакоформирующее устройство | 1984 |

|

SU1259330A1 |

Авторы

Даты

1979-02-15—Публикация

1977-09-30—Подача