(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

HdiR информаднонаых выходов устройства, выход регнстра состовшвй и первый выход регистра данных соедивены с соотве1х:твующими выходами на грутгаы ив({ж1рмацвокаых выходов устройства, вторые вход и выход регистра данных подключены к соответствующим входам н выходам из грутты ивформапионных входов и выходов устройства, третий йход регистра данных и второй вход блока шифрапнн команд соедвневы с группой информационных входов устройства, второй выход блока сшакронизации подключен к четвертому входу регистра данных, ко вторым входам регистра адреса и регистра состояний и к третьему входу блока дешифрации команд t23 ,

Однако это устройство имеет низкое быстродействие, поскольку поиск запрос связи реализуется путем последователь ноге олроса состояний всех функдиональных модудей 1юрвферийной системы.

Целыо изобретения является повыше нне быстродействия устройства.

Достигается это благодаря тому, что в устройство введены блок управ- пения обменом, шифратор ссютояний, соединенный выходом с первы - входом блока формирования адреса запроса связи, второй, третий н четвертый входы которого соединены соответственно с грутаюй информационных входов устройства, вторым выходом блока синхронизации в выходом блока дешифрации адреса, информационные входы ат4фатора состояний соединены с вторыми входом а Выходом регистра данных, а управля- вмдий вход подключен к второму выхо ду блока сннхроншзааья и первому вхо- ду блока управления обменом, первый йыход которого соединен с пятым вхо«дом блока синхронизации, выход блоха формирования адреса запроса связи соединен с адресным выходом устройства два выхода вызова и вход ответа кото рого соответственно подключены s второму и третьему выходам и второму входу блока управления обменом.

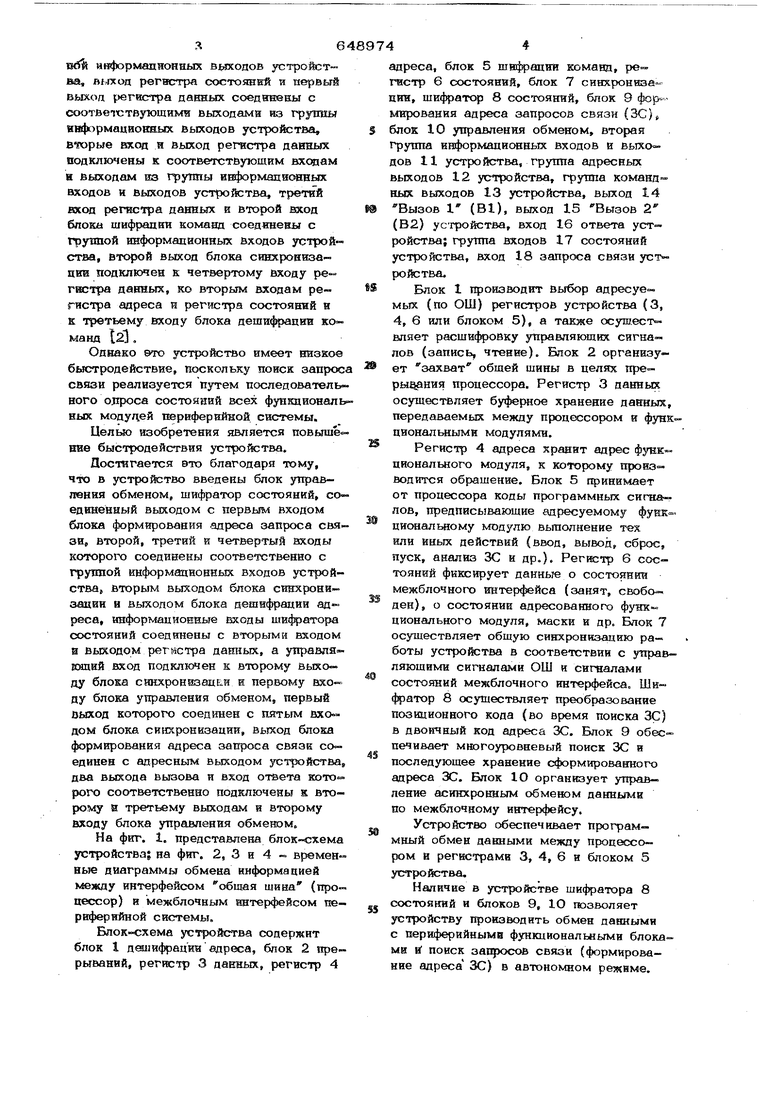

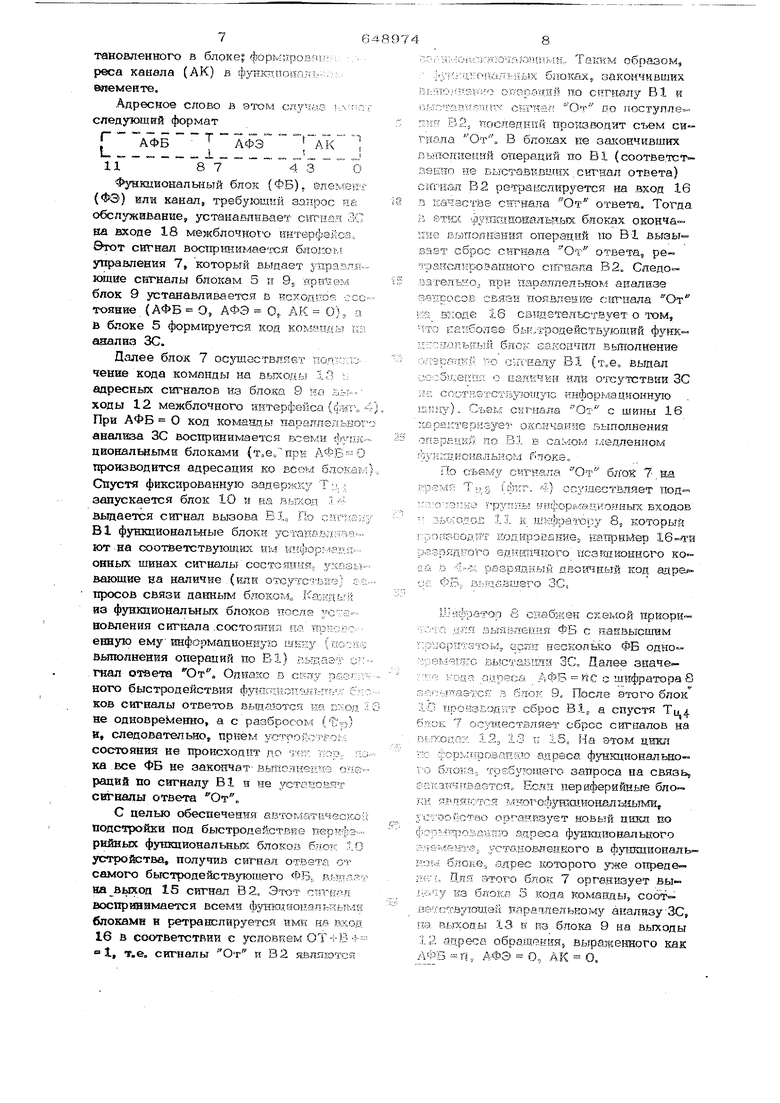

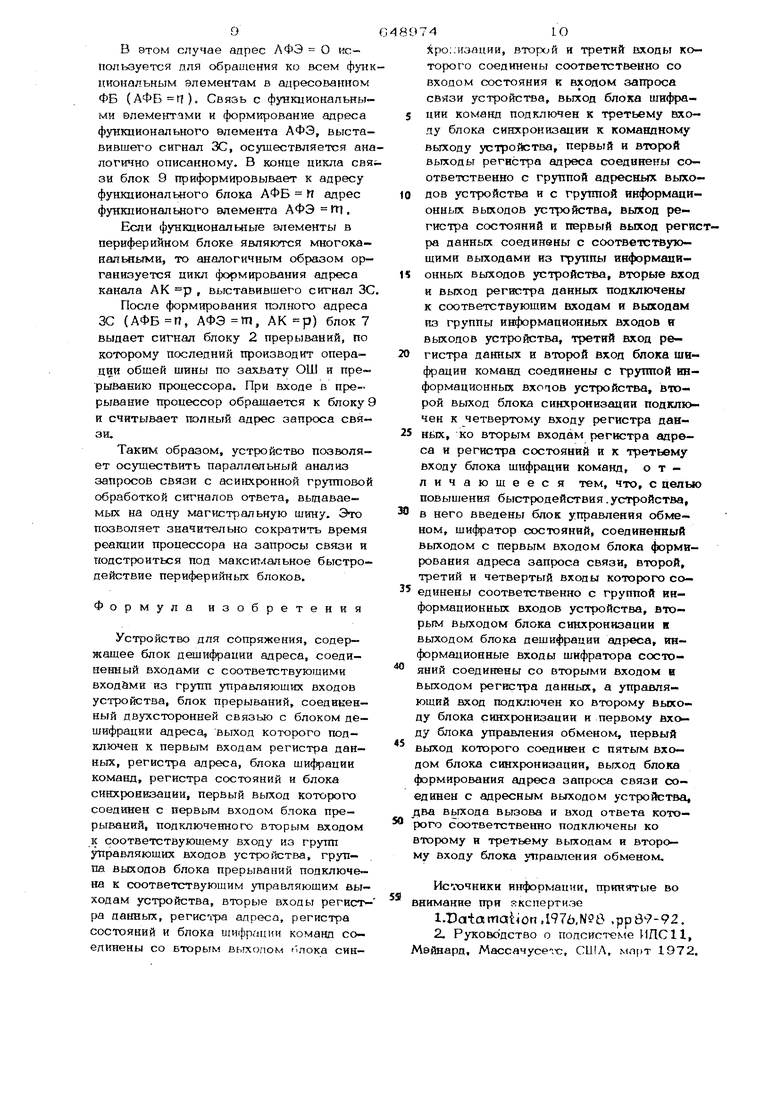

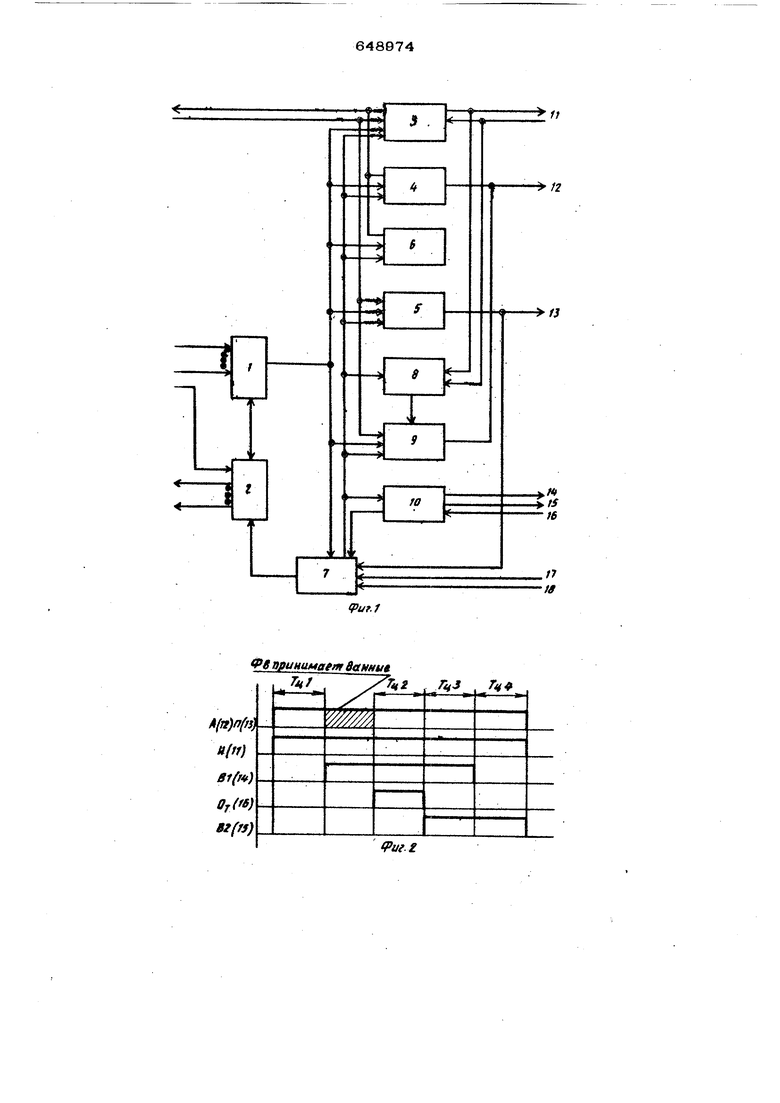

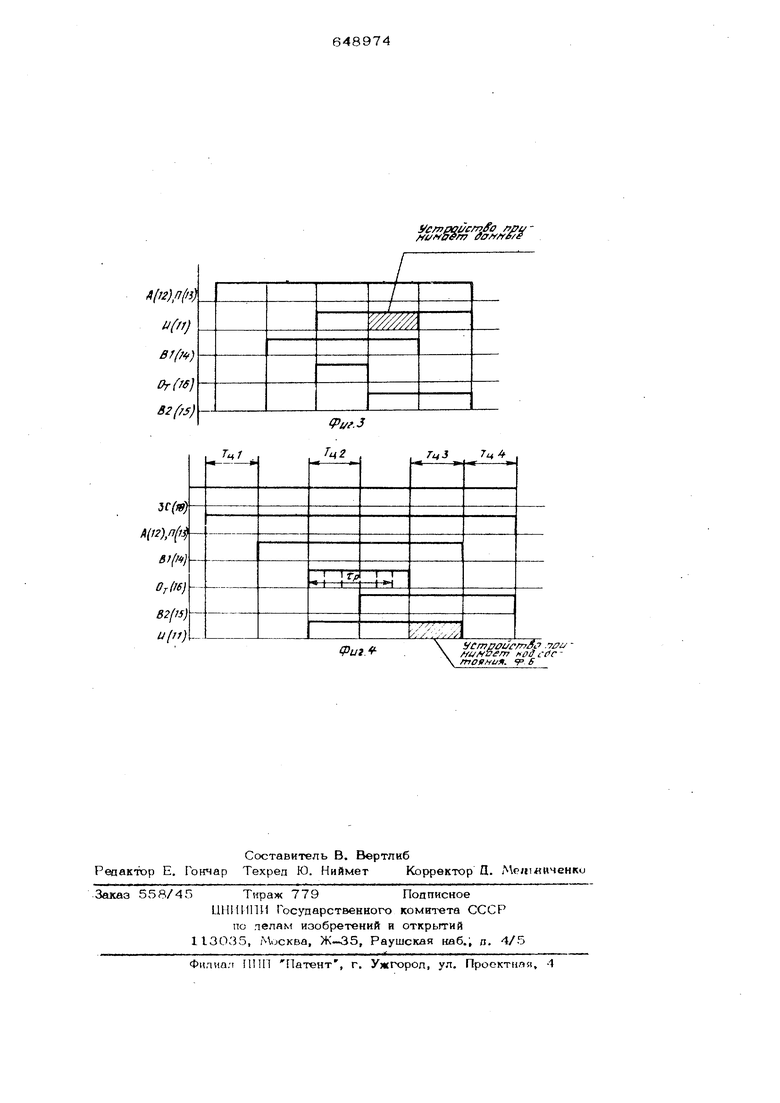

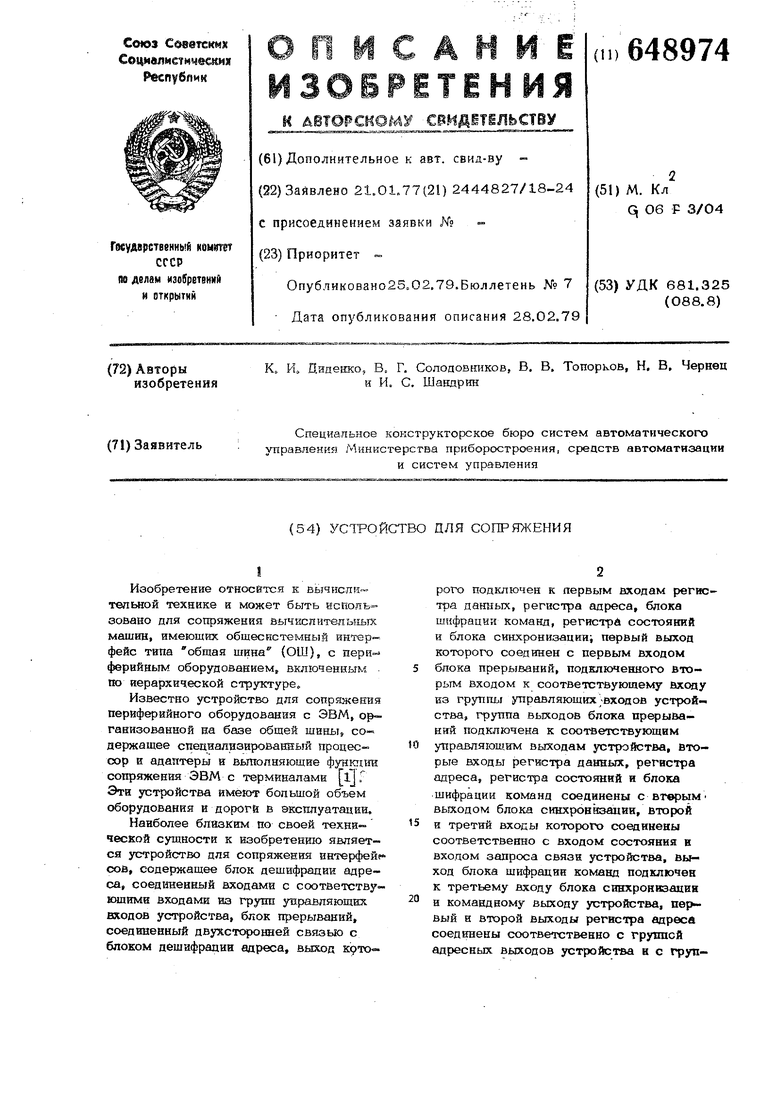

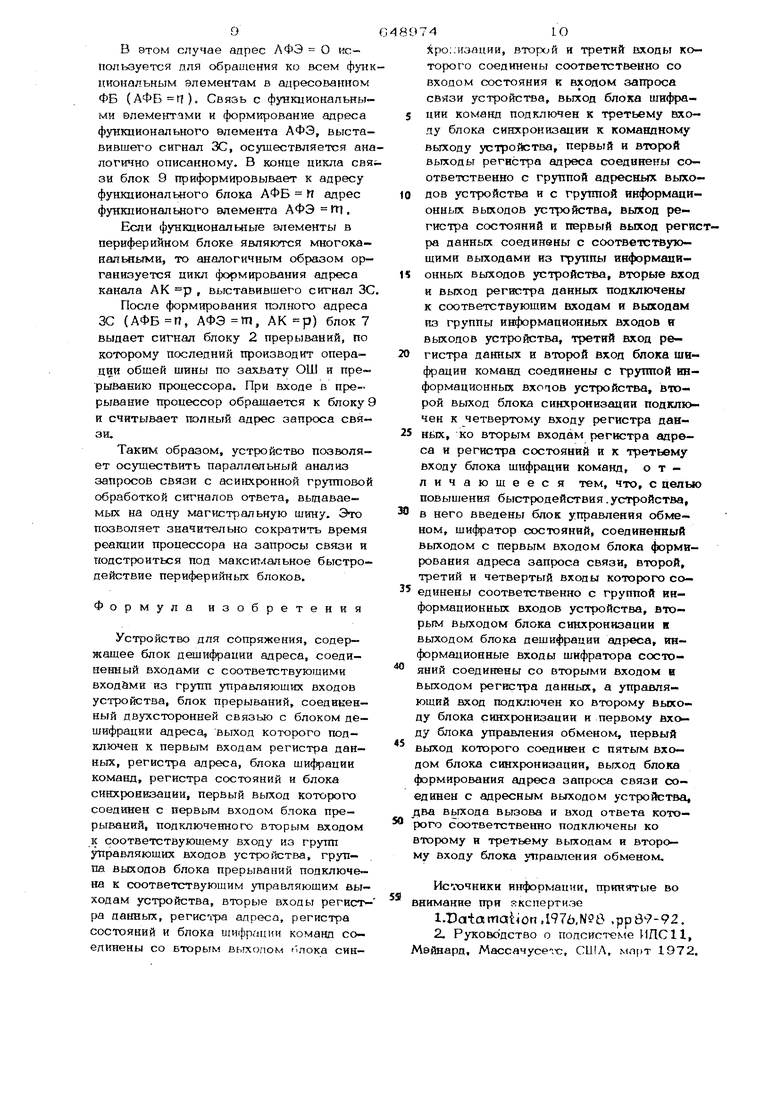

На фиг. 1. пpeдcтajaлeнa блок-схема устройства; на фиг, 2, 3 и 4 - временнью диаграммы обмена информацией между интерфейсом общая шина (процессор) и межблочным автерфейсом периферийной системы.

Блок-схема устройства содержит блок I детии(}фацни адреса, блок 2 прерываний, регистр 3 данных, регистр 4

адреса, блок 5 шифрапин команд, ре. гистр 6 состояний, блок 7 синхроннвв ЦЕН, шифратор 8 состояний, блок 9 фор мнрования адреса запросов связи {ЗС}, блок 10 управления обменом, вторая Группа ивоформационных входов и выходов 11 устройства, группа адресных выходов 12 устройства, rpytma командных выходов 13 устройства, выход 14 Вызов 1 (В1), выход 15 Вызов 2 (В2) устройства, вход 16 ответа устройства; группа входов 17 состояний устройства, вход 18 запроса связи устройства.

Блок 1 производит выбор адресуемых (по ОШ) регистров устройства (3, 4, 6 или блоком 5), а также осуш.ест вляет расшифровку управляющих сигналов (запись, чтение). Блок 2 организует захват общей шины в целях преры ния процессора. Регистр 3 данных осуществляет буферное хранение данных передаваемых между процессором и фунциональными модулями.

Регистр 4 адреса хранит адрес функционального модуля, к которому производится обращение. Блок 5 принимает от процессора коды программных сигналов, предписывающие адресуемому функ циональному модулю вьгаолнение тех ИЛИ иных действий (ввод, вывод, сброс, пуск, анализ ЗС и др.). Регистр 6 состояний фиксирует данные о состоянии межблочного интерфейса (занят, свободен), о состоянии адресованного функционального модуля, маски и др. Блок 7 осуществляет общую синхронизацию работы устройства в соответствии с управляющими сигналами ОШ и сигналами состояний межблочного интерфейса. Шифратор 8 осуществляет преобразование позиционного кода (во время поиска ЗС) в двоичный код адреса ЗС. Блок 9 обеспечивает многоуровневый поиск ЗС и последующее хранение а|юрмированного aaf)eca ЗС. Блок 1О организует управление асинхронным обменом данными по межблочному интер)фейсу.

Устройство обеспечивает программный обмен данными между процессо{юм я регистрами 3, 4, 6 и блоком 5 устройства.

Наличие в устройстве шифратора 8 состояний и блоков 9, 1О гюзволяет устройству производить обмен данными с периферийными функциональными блоками и поиск 3aiqxxx B связи (формирование адреса ЗС) в автономном режиме. Устройство работает следующим образом. Связь процессора с устройство осуществляется на уровне регистров устройства, а пересылка данных ме5вду устройством и периферийными блоками и поиск запросов связи производится без участия процессора. Регистры 3, 4, 6 и блок 5 доступны процессору и последний может производить обравде- ние к ним в режимах записи и чтения в соответствии с апгорвплоы фушшион рования интерфейса ОШ. Обращение процессора к регистрам устройства осуществляется в следующи целях: засылка в регистр 3 или чтение данных с регистра 3; засылка в регистр 4 адреса фушшионального м дуля, к которому требуется произвести обращение для ввода или вывода иофор- мапии; засылка в блок 5 сигналов, пре писывающих. адресуемому функдяонально му модулю те или иные действия (ввод вывод, пуск, сброс и т.д.), чтение кода состояний вз регистра 6, а также уста новка масок в регистре 6. Процедура передачи данных из пропесхюра в фзгнкционал1яый модуль заключается в следующем, Процессор производит засылку данных в регистр 3, адреса обращения в регистр 4 и программного кода, соответствующего режиму ьвод, в блок 5. После ВТОГО процессор отключается и устройство автономно организовывает цикл связи с адресуемым фувкциональЕым модулем по межблочному интерфейсу в соответствии с диаграммой, приведенной на фиг. 2. В начале пикла на вторую группу информационных входов - выходов II из регистра 3 выдаются данвые, на группу адресных выходов 12 из регистра 4 значение адреса обращения и на группу командных выходов 13 - эвачение кода команды. Спустя фиксированную задержку Тщ времени необходимую для опознавания адреса функциональным модулем, запускается блок 10 и на выходе 14 устанавливает ся сигнал В1. Адресуемый функциональный блок (алемент) по сигналу В1 начинает выпопненва предписанной операции (в даввом случае прием данвиох со второй группы внформацвонных входов и выходов II) и после ее выполнения извещает устройство об этом сигналом ответа От по входу 16. По сигналу От блок Ю через время выдает на выход 15 сигнал В 2, который ретранслируется в функциональном блоке, как прием игнала От. Блок 1О после исчезновения сигнала ответа От делает выдержку Тц , после чего сбрасывает сигнал В1 и извещает блок 7 о, состоявшемся сеансе связи. 7, спустя задержку Тц., выдает управляющий сигнал, по которому производит ся отключение информационных, адресных и командных сигналов, а также сигналя В2 от магистрали интерфейских связей. На этом процедура передачи данных из процессора в функциональный блок заканчивается. Передача данных из футасцвовапьвого Модули в прсщесжор осушествляется следующим . Г оцессор производит засылку в ре- 4 адреса - бращения и в блок- 5 - командного кода, соответствующего режиму вывод. Далее, устройство осушесталяет аВтсжомный цикл связи с функциональвым модулем (см. фиг. 3). Блок 7 организует подключение адресных сигналов из регистра 4 на rpytmy адресных выходов 12 и сигналов вз блока 5 на группу командных выходов 13. Спустя время Тщ запускается блок 10 и на выходе 14 устанавливается снгвиш вызова В1. Адресуемый функциовальаыв модуль в режиме вывод по снгвалу В1 выдает иоформацвонвые сигналы на вход из группы информационных входов н выходов 11 .сигналы состояния на входы 17 и извещает об этом устройство сигма- лом ответа От. По сигналу От блок 1О выдает сигнал В 2, что приводит к сбросу сигнала От. Далее в течение времени устройство производит прием данных с входов и выходов 11 в регистр 3 и сигналов состояния в регистр 6, после чего организуется отключение связи с функциональвым модулем - сбрасываются сигналы с выходов 12, 13 и 15. Съем данных с репютра 3 процессор может произвести в режиме программного обмена лвбо по прерыванию. Устройство обеспечивает автонок ный (без участия процессора) параллельный анализ запросов связи и формирование адреса ЗС по трем уровням: формирование адреса функционального блока (АФБ); формирование адреса функционального элемента (АФЭ), ус76танрвленного в блоке; форыяровяи / реса канала (АК) в функдпонл;.:-..;: вяемеите. Адресное слово и этом слу-шз следующий формат АФБ АФЭ И в 7 4-3О Функционалы ый блок (ФБ), епеме-гг (ФЭ) или канал, требующий запрос не обслуживание, устанавпавает cirrHan 3G ва входе 18 межблочног-о интерфейса,, Этот ситная восгфтщимаех-ся бло.ко5Л утфавпения 7, который выдает управляющие Сигналы блокам 5 н 9 1рн5:ем блок 9 устанавливается в исходкое ссстояние (АФБ О, АФЭ О, АК О), а U блоке 5 формируется код команды г;;;. аяалиэ ЗС. Далее блок 7 осущаствляет под г:то чение кода команды на выходьз 13 -i адресных сигналов из блока 9 на .&-;-. ходы 12 межблочного интерфейса (4;иг., 4 При АФБ О код команпь параггпельного анализа ЗС востфинимается ь:;еми ф;а1Кциокалшыми блока1 1и (.прн производится адресация ко всеы бяокагл) Спустя фиксированную задержку Т: i ; запускается блок Ю а на й.ьгкод т - выдается сигнал вызова Е1, По сиг-ш;:; В1 функциональные блоки устапавлива-. ют на соответствующих им инфоргладя.: онных шйнах сигналы состоявшая,; указывающие ва наличие (или отсутствие ге;просов связи данным блоком, Какдьгй из функциональных блоков поспэ стзвовления сигнала .состопикл кя ттрксесевную ему информадиоЕную шкну {ио:-:к выполнения операций по В1) йыдаат , гнал ответа От Опнако в с;шу него быстродействия фугпсчиоп гльп-Г;/; б-:: ков сигвалы ответов выдаются на вход К не одновреК енно, а с разбросам (f™) н, следовательно приём устгокс-ррогл состояния не происходит по тк коэ :чо ка .все ФБ не закончат- вьшслкеЕЧ-э операций до сигналу В1 я не СТРНОВЯТ сигналы ответа От. С целью обеспечения автоматической подстрюйки под быстродействие керт-т-Ьз-.рийных фушшйональ аых блоков блок 10 устройства, получив сигнал ответа от самого быстродействующего ФБ. выявит на выход 15 сигнал В 2, Этот воспривнмается всема ф5Т1Кцаональн.ымк блоквмн и ретранслируется ими на .вход 16 в соответствии с усповиеы 1, т.е. сигналы От и В2 явпгнотся -:,:Г;-и-;О1г -;кл;:очйго5)иь;к,. Таккм образом, .:ц;:оп:ап1:«ых бпокЕх, закончивших гг;ато. опэряннй по сигналу В1 и :iM;--raS ;-:vin- сЕгна-гг От до посгупле пид В2, послэпний производит съем сигиапа От,, В бпосах не закончивших выпоянений оиераций по В1 (соотве.тст.58Ц-НО не выставившей;, ответа) сйгнбл В 2 ретракслируетт;я на вход 16 Q качастйе сигнала От ответа. Тогда в фунтакональйых блоках окончание ЕЬ5Попнзния операций по В1 выэы .вает сброс сигнала От ответа, ретазнслнроэанного сгггнапа В 2. Следо .изтельно при параллельном анализе ЗЯ РОСОВ свяаи появлецке сигнала От :.-: В1:оде 18 свидетельствует о том, гго наиболее быс.тродейстБующий фуюс ц;::яапьпъ1Й блок аакоачил выполнение :: /- эря7ти-« GSiVBny В1 {т.е. выдал сс :5:11::еЕП1Л о нлй о-шутствии ЗС i-Hi С1 отн5гстБу о1цу1с Информационную тпну). Съем сигнала с шины 16 херЕктеризуе ов:ончаиие выполнения опзрйцкй по BJ в самом иедленном фук:п;ионально л (поке По съему сшгкала От бяок 7.на ppevvifi T;.g (фт;г. 4) осуществляет под- г;1;о-;:э -ие группы иифорг..аиконньгх входов : зм.о.до.с 11 к гпйфраа-ору 8 который : роггрооднт коднрзвакиег ЕаттрньЛер Хб-я-и разрядЕого едиипчного псзгщноЕНОГо ко- аи .U разрядньгй ПВОИЧЕЫЙ код адре Cii ФБ- в.щЕ.ашэго ЗС, Шифратор 8 снабжен скемой прйорИ :--1п .цгя зыягзпецйя ФБ с наивысигам np:JOptiTSroi«j если несколько ФБ одно iviRiv-i TTijc выставили ЗС, Далее аЕаче г:-ч кода адреса АФВ ЯС с штсфратора 8 заг;улается: з блок 9„ После этого блок л.О пронзЕ.одйт сброс В I. а спустя Тц jSблок 7 осуществляет сброс сигналов на пь;т:оцет: 12, 13 и IS, На этом цакл :;: ;sopMtjpo.BaHS5o адреса функционального блотга, требующето запроса на связь рйканчгшайтся Есла периферийные бло у;;и з.рлятг:тся мкогофушщиональяыми, .рсгоочсТво oDrasriBjreT новьзй цикл по формщтозаиггю адреса функционального элемегйз, установленЕого в функцнональиоьл бло1;.е.5 адрес котх)рого уже опреде- ккi. Для ВТОГО блок 7 оргадиаует выдачу вз блока 5 кода команды соот- ведсгвующай |лараллельному анализуЗС, та вьрсодь 13 н Ез блока 9 на выходы 12 адреса обраш ккя выралсешюго как АФБ Г1, АФЭ О, АК О. о в ВТОМ случае адрес ЛФЭ О ксполгэзуется для обращения ко всем фун циональным элементам в адресованном ФБ (), Связь с функциональными влементами и формирование адреса функционального элемента АФЭ, выставившего сигнал ЗС, осуществляется ан логично описанному, В конце цикла свя зи блок 9 приформировывает к адресу функционального блока АФБ П адрес функционального элемента АФЭ П1, Если функциональные э;тементы в периферийном блоке являются многоканальными, то аналогичным образом организуется цикл формирования адреса канала АК р , выставившего сигнал ЗС После формирования полного адреса ЗС (, , АК р) блок 7 выдает сигнал блоку 2 прерываний, по которому последний производит операции обшей шины по захвату ОШ и прерыванию процессора. При входе в прерывание процессор обращается к блоку и считывает полный адрес запроса связи. Таким образом, устройство позволяет осуществить параллельный анализ запросов связи с асинхронной группово обработкой сигналов ответа, вьщаваемых на одну магистральную шину. Это позволяет значительно сократить время реакции процессора на запросы связи и подстроиться под максит альное быстродействие периферийных блоков. Формула изобретения Устройство для сопряжения, содержащее блок дешифрации адреса, соединенный входами с соответствующими входами из грутт управляющих входов устройства, блок прерываний, соединенный двухсторонней связью с блоком дешифрации адреса, выход которого подключен к первым входам регистра данных, регистра , блока шифрации команд, регистра состояний и блока синхронизации, первый выход которого соединен с первьпи входом блока прерываний, подключенного вторым входом к соответствующему входу из грутш управляющих входов устройства, группа выходов блока прерываний подключена к соответствующим управляющим выходам устройства, вторые входы регист ра данных, регистра адреса, регистра состояний и блока шифрации команд соединены со вторым BbJXonoM плока син- 741О ро:.изации, второй и третий входы которого соединены соответственно со входом состояния к входом запроса связи устройства, выход блока шифрации команд подключен к третьему входу блока синхронизации к командному выходу устройства, первый и второй выходы регистра адреса соединены соответственно с группой адресных выхо- дов устройства и с группой информационных выходов устройства, выход регистра состояний и первый выход регистра данных соединены с соответствующими выходами из группы информационных выходов устройства, вторые вход и выход регистра данных подключены к соответствующим входам и выходам из группы информационных входов и выходов устройства, третий вход ре- гистра данных и второй вход блока шнфрации команд соединены с группой информационных входов устройства, второй выход блока синхронизации подключен к четвертому входу регистра дан- ных, ко вторым входам регистра адреса и регистра состояний и к третьемувходу блока шифрации команд, отличающееся тем, что, с целью повышения быстродействия. устройства, в него введены блок управления обменом, шифратор состояний, соединенный выходом с первым входом блока формирования адреса запрюса связи, второй, третий и четвертый входы которого соединены соответственно с группой информационных входов устройства, вторым выходом блока синхронизации н выходом блока дешифрации адреса, информационные входы шифратора состояний соединены со вторыми входом в Выходом регшзтра данных, а управляющий вход подключен ко второму выходу блока синхронизации и первому входу блока управления обменом, первый выход которого соединен с пятым входом блока синхронизации, выход блока ормирования адреса запроса связи содинен с адресным выходом устройства, ва вьтхода вызова и вход ответа котоого соответственно подключены ко торому я третьему выходам и второу входу блока управления обменом. Ислэчники информации, принятые во нимание пря якспертизе l.Iiatamation,1976,№e ,рр89-92. 2. Руководство о подсистеме ИПС11, эйнард, MaccaHyce-i-c, США, мпрт 1972.

Vcfpoijcmfo fft/ Л7А/гА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с периферийными устройствами | 1981 |

|

SU960787A1 |

| Устройство управления блоками ввода-вывода вычислительной системы | 1973 |

|

SU497576A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для сопряжения | 1976 |

|

SU648972A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для сопряжения процессоров в однородной вычислительной системе | 1984 |

|

SU1179364A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения магистралей | 1990 |

|

SU1737460A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

Риг.З

iPut.fycmuffi c i . ffi/ffVfrrr nod тояния. f S

Авторы

Даты

1979-02-25—Публикация

1977-01-21—Подача