(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

Поставленная цель достигается тем,

что в устройство введены блок групповой синхронизации, три блока влементов ИЛИ и два блока элементов И, причем первый и второй входы блока групповой синхронизации подключены к соответствующим входам вызова устройства, а первый и второй выходы - к соответствукмцим выходам вызова устройства, третий выход блока групповой синхронизации соединен с третьим входом блока анализа состояния и вторым блоком индикации неисправности, третий вход ко.торого подключен к выходу дешифратора команды, первому входу первого блока элементов ИЛИ, управляющим входам первого и второго блоков элементов И и четвертому входу блока анализа состояния, первым, вторым и третьим выходами соединенного соответственно со вторым, третьим и -четвертым входами первого блока элементов ИЛИ, выход первого блока элементов ИЛИ соединен со вторым управл51ющим входом первого блока элементов И, первый вход и выход третьего блока элементов И подключены соответственно к командным входу и выходу устройства, первый выход дешифратора группового обращения соединен с первым входом четвертого блока элементов И, четвертым входом блока индикации неисправности, вторым входом третьего блока элементов И и третьим входом блока групповой синхронизации, четвертый вход которого подключен к третьему входу третьего блока элементов И пятому входу блока анализа неисправностей, второму входу четвертого блока элементов И и выходу второго блока элементов ИЛИ, первый вход которого подключен.к первому выходу дешифратора адреса, а второй - ко второму выходу блока группового обращения и шестому входу блока индикации неисправности, сед1А«)Й вход блока индикации неисправности соединен с третьим выхо дом дешв4ч аторй группового обращения и первым входом третьего блока элементов ИЛИ, второй вход и выход которого подключены соответственно со вторым выходом дешифратора адреса в вьк ходом адреса функционального элемента устройства, третий вход и выход четвертого блока элементов И соединены соответственно с адресным входом устройства и адресом канала устройства, вход дешифратора группового рбращения подключен ко входу дешифратора адреса.

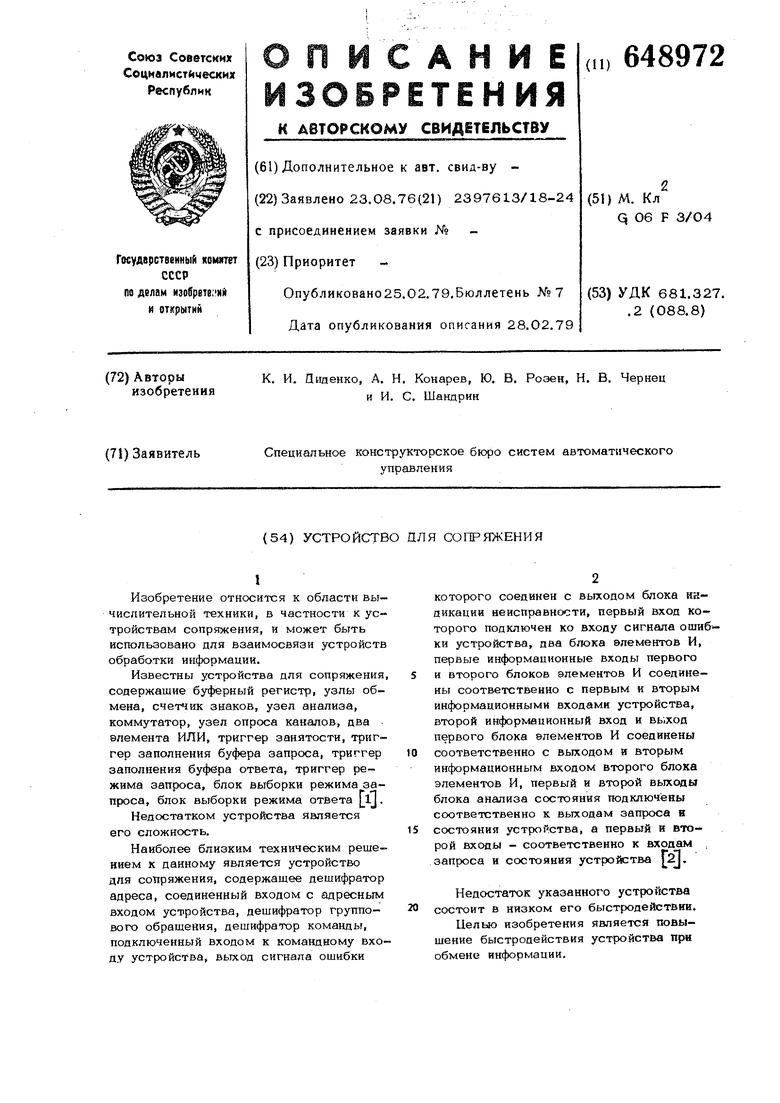

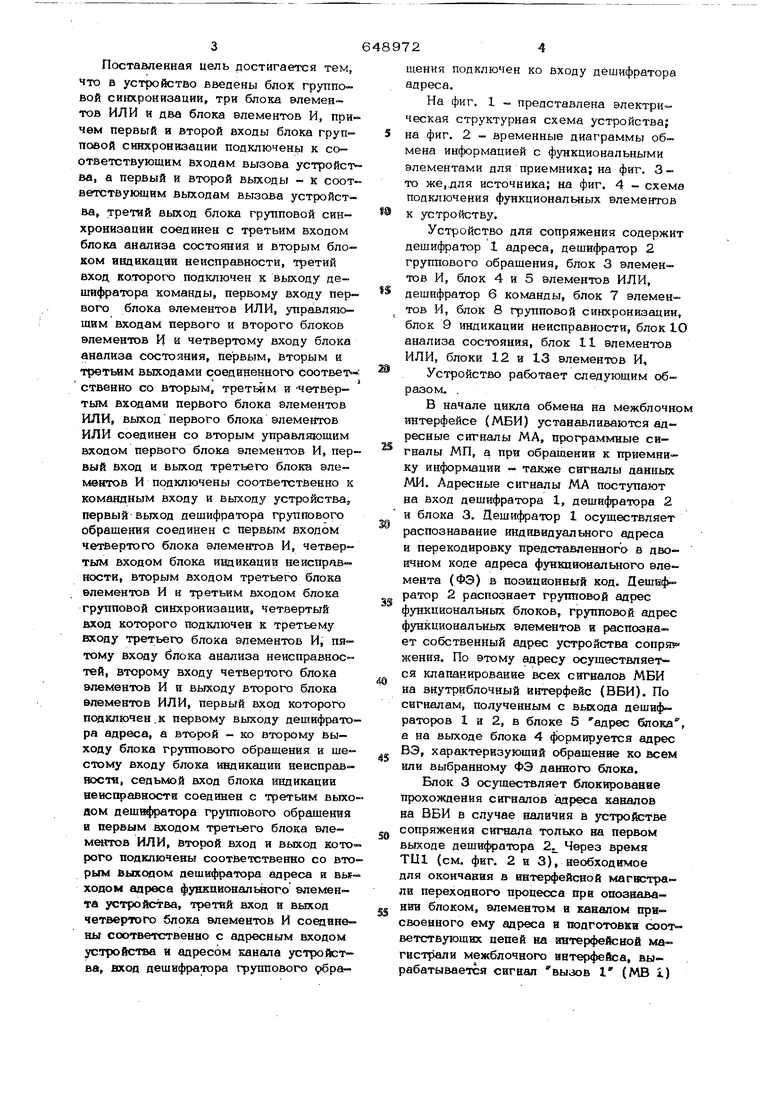

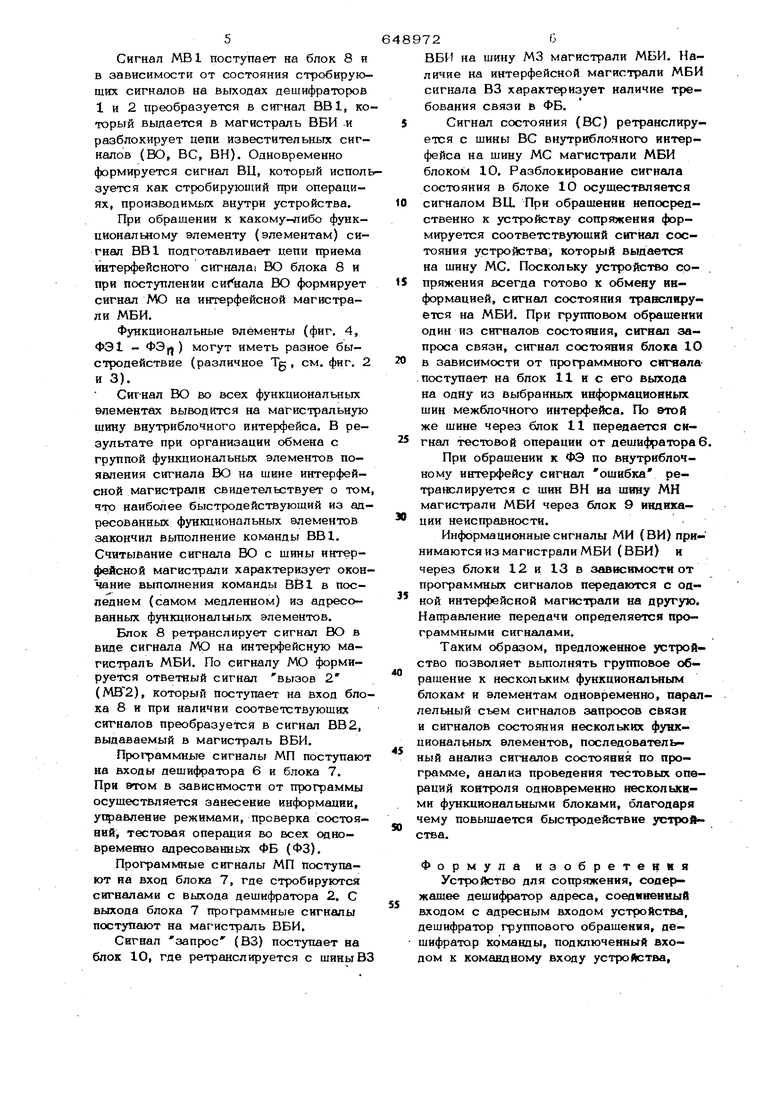

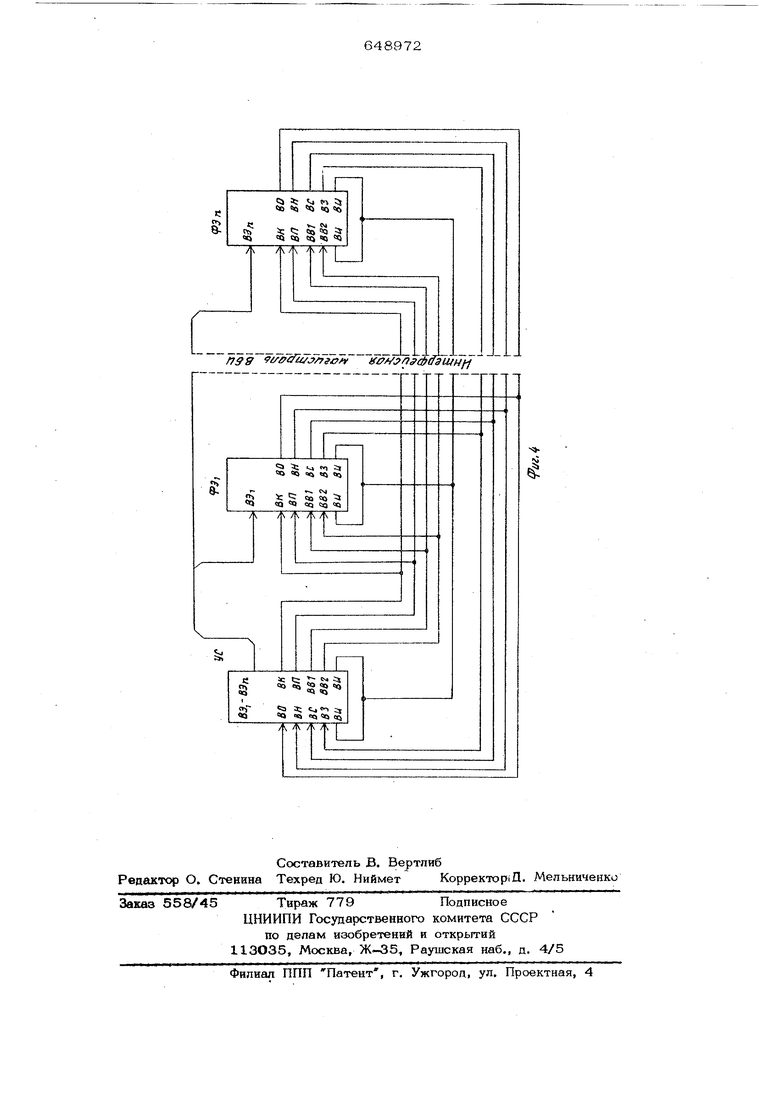

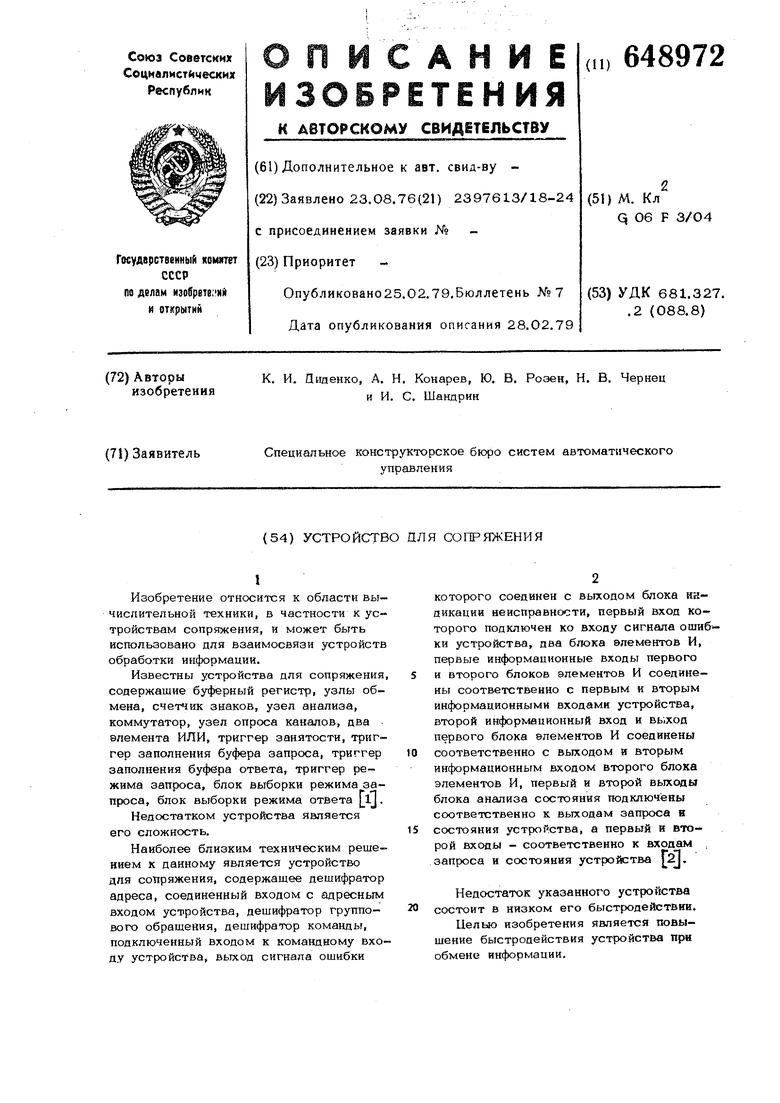

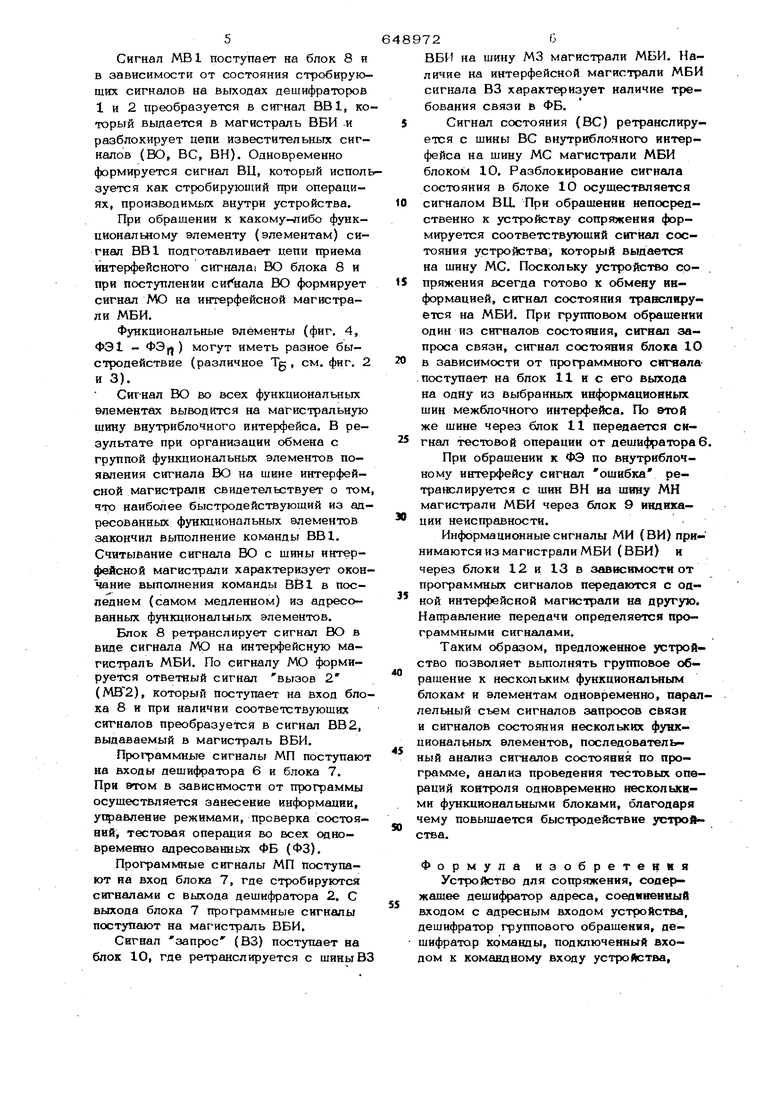

На фиг. 1 - представлена электрическая структурная схема устройства; на фиг. 2 - временные диаграммы обмена информацией с функциональными элементами для приемника; на фиг. 3 - то же,лля источника; на фиг. 4 - схема подключения функциональных элементов к устройству.

Устройство для сопряжения содержит дешифратор 1 адреса, дешифратор 2 группового обращения, блок 3 элементов И, блок 4 и 5 элементов ИЛИ, дешифратор 6 команды, блок 7 элементов И, блок 8 групповой синхронизации, блок 9 индикации неисправности, блок 10 анализа состояния, блок 11 элементов ИЛИ, блоки 12 и 13 элементов И,

Устройство работает следующим образом. .

В начале цикла обмена на межблочно интерфейсе (МБИ) устанавливаются адресные сигналы МА, программные сигналы МП, а при обращении к приемнику информации « также сигналы данных МИ. Адресные сигналы МА поступают на вход дешифратора 1, дешифратора 2 и блока 3. Дешифратор 1 осуществляет распознавание индивидуального адреса и перекодировку представленного в двоичном коде адреса функционального элемента (ФЭ) в позиционный код. Дешкс ь. ратор 2 распознает групповой адрес функциональных блоков, групповой адрес функциональных элементов и распознает собственный адрес устройства сопря « жения. По этому адресу осуществляется клапан кровен ие всех сигналов МБИ на внутриблочный интерфейс (ВБИ). По сигналам, полученным с выхода дешифраторов I и 2, в блоке 5 адрес блока а на выходе блока 4 формируется адрес ВЭ, характеризующий обращение ко всем или выбранному ФЭ данного блока.

Блок 3 осуществляет блокирование прохождения сигналов адреса каналов на ВБИ в случае наличия в устройстве сопряжения сигнала только на первом выходе дешифратора 2.. Через время ТШ (см. фиг. 2 и 3), необходимое для окончаная в интерфейсной магистрали переходного процесса при опозваванви блоком, элементом и каналом прв своенного ему адреса н подготовки соответствующих цепей на интерфейсной магистрали межблочного интерфейса, вырабатывается сигнал вызов I (МБ i) 5 Сигнал MB 1 поступает на блок 8 и в зависимости от состояния стробирую щих сигналов на выходах дешифраторов 1 и 2 преобразуется в сигнал ВВ1, ко торый выдается в магистраль ВБИ и разблокирует цепи известительных сигналов (Ю, ВС, ВН). Одновременно формируется ВЦ, который испол зуется как стробируюпшй при операциях, производимых внутри устройства. При обращении к какому-либо функциональному элементу (элементам) сигнал ВВ1 подготавливает цепи приема интерфейсного сигнала ВО блока 8 и при поступлении ВО формирует сигнал МО на интерфейсной магистрали МБИ. Функциональные элементы (фиг, 4, ФЭ1 - ФЭ ) могут иметь разное быстродействие (различное Tg , см. фиг. 2 и 3). Сигнал ВО во всех функциональных элементах выводится на магистральную шину внутриблочного интерфейса. В результате при организации обмена с группой функциональных элементов появления сигнала ВО на шине интерфейсной магистрали свидетельствует о том что наиболее быстродействующий из ад ресованных функциональных элементов закончил выполнение команды ВВ1. Считывание сигнала ВО с шины интерфейсной магистрали характеризует окон чание выполнения команды ВВ1 в последнем (самом медленном) из адресованных функциональных элементов. Блок 8 ретранслирует сигнал ВО в виде сигнала МО на интерфейсную магистраль МБИ. По сигналу МО формируется ответный сигнал вызов 2 (МВ2), который поступает на вход бло ка 8 и при наличии соответствующих сигналов преобразуется в сигнал ВВ2, выдаваемый в магистраль ВБИ. Программные сигналы МП поступаю на входы дешифратора 6 и блока 7. При этом в зависимости от программы осуществляется занесение информации, ущзавление режимами, проверка состояний, тестовая операция во всех одновременно адресованных ФБ (ФЗ). Программные сигналы МП поступают на вход блока 7, где стробируются сигналами с выхода дешифратора 2. С выхода блока 7 программные сигналы поступают на магистраль ВБИ. Сигнал запрос (ВЗ) поступает на блок 10, где ретранслируется с шиныВ 72 ВБИ на шину МЗ магистрали МБИ. Наличие на интерфейсной магистрали МБИ сигнала ВЗ характеризует наличие требования связи в ФБ. Сигнал состояния (ВС) ретранслируется с шины ВС внутрибло.чного интерфейса на шину МС магистрали МБИ блоком 10. Разблокирование сигнала состояния в блоке 10 осуществляется сигналом ВЦ. При обращении непосредственно к устройству сопряжения формируется соответствующий сигнал состояния устройства, который выдается на шину МС. Поскольку устройство сопряжения всегда готово к обмену информацией, сигнал состояния травслируется на МБИ, При групповом обращении один из сигналов состояния, сигнал запроса связи, сигнал состояния блока 10 в зависимости от программного сигнала поступает на блок 11 и с его выхода на одну из выбранных информационных щин межблочного интерфейса. По этой же шине через блок 11 передается сигнал тестовой операции от дешифратора 6. При обращении к ФЭ по внутриблоч- ному интерфейсу сигнал ошибка ретранслируется с шин ВН на шину МН магистрали МБИ через блок 9 индикации неисправности. Информационные сигналы МИ (ВИ) принимаются из магистрали МБИ (ВБИ) и через блоки 12 и 13 в зависимости от программных сигналов передаются с одной интерфейсной магистрали на другую. Направление передачи определяется программными сигналами. Таким образом, предложенное устройство позволяет выполнять групповое обращение к нескольким функциональным блокам и элементам одновременно, параллельный съем сигналов запросов связи и сигналов состояния нескольких функциональных элементов, последовательный анализ сигналов состояния по программе, анализ проведения тестовых операций контроля одновременно несколькими функциональными блоками, благодаря чему повышается быстродействие устройтва. Формула изобретеивя Устройство для сопряжения, содержащее дешифратор адреса, соединенный входом с адресным входом устройства, дешифратор группового обращения, дещифратар команды, подключенный входом к командному входу устро ;тва,

выхоп сигвапа ошибки которого соедиВ8ев с выходом блока индюшции невспpaBH«X3TH, первый вход которого подключен к входу снгнапа ошибкн устройства, . два блока BneMeHTCiB И, первые ввформацновные входы первого в ато рого блоков елемевтов И соедшевы соответственно с первым и вторым информапвоввыми входамв устройства, ВфороЁ внформагшовный вход в выход первого блока алементов И соединены сях тввэд твенно с выходом и вторым внформаввонным входом второго блока влементов И, первый в второй выходы блока анелвэа состоянвя подключены соответственно к выходам запроса и состояния устройства, а первый и второй Ёхоаы - соответс-шевно к входам запроса н состояния устройства, о т лвчающееся тем, что, с целью по&ышенвя быстродействия устройства, в вего введевы блок групповой синхронвдаавв, три блока влементов ИЛИ и два блока влементов И, причем первый и второй входы блока групповой синхро ввзаавн воаключены к соответствующим входам Ёызоаа устройства, а первый и второй выкопы к соответствуюшвм выходам вызова устройства, третвй выход блока груткзвой сввЕхронизадии соедв вюв с третьем входом блока анализа состо вя в вторым блоком индикации вевспраязоств, чретвй вход которого водвлючен к выходу дешифратора коман ды, первому входу первого блока элементов ИЛИ, управляющим входам первого в Второго блоков влементов И и четвертому входу блока анализа состояния первым, вторым и третьим выходами соедивенного соответственно со Bropы, третьем и четвертым (входами первого блока влементов ИЛИ, выход первого блока влементов ИЛИ соединен

со в-торым управляющим входом первого блока 9лементов И, первый вход и выход третьего блока влементов И подключены соответственно к командным входу и выходу устройства, первый выход дешифратора группового обращения соединен с первым входом четвертого блока элементов И, четвертым входом блока индикации неисправности, вторым Входом третьего блока элементов И и третьим входом блока групповой синхро нвзации, четвертый вход которого подключен к третьему входу третьего блок влементов И, пятому входу блока анализа неисправностей, второму входу четвертого блока элементов И и выходу Второго блока элементов ИЛИ, первый вход которого подключен к первом выходу дешифратора адреса, а второйко второму выходу блока группового обращения и шестому входу блока индикации неисправности, седьмой вход блока индикации неисправности соединен с третьим выходом дешифратора группового обращения и первым входом третьего блока элементов ИЛИ, второй вход и выход которого подключены соответственно со вторым выходом дешифратора адреса и выходом адреса функционального впемента устройства, третий вход и выход четвертого блока элементов И соединены соответственно с адресным входом устройства и адресом канала устройства, вход дешифратора группового обращения подключен ко входу дешифратора адреса.

Источники информации, принятые во внимание прв експертизе

1,Авторское свидетельство СССР № 443385, кл. Q 06 F 3/О4, 1971.

2.Авторское свидетельство СССР № 558274, кл. ( Об F 3/О4, 1974.

ня

НН) (

(ии иг.1

4 ,

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерфейсный блок для управляющей системы | 1981 |

|

SU1001075A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для сопряжения микропроцессора с периферийными устройствами | 1987 |

|

SU1434440A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для обмена данными | 1988 |

|

SU1599863A1 |

| Устройство для захвата магистрали ЭВМ | 1982 |

|

SU1075247A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Устройство для сопряжения абонента с магистралью в микропроцессорной системе | 1987 |

|

SU1538173A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

г I

§

1 I

i

л 5

«оСц«о tQ Ч)

С;5 OQ

J§

(JQ «О 41

nffs i ff ff J/fga Kff ftffdfffsuiHfj

g

Авторы

Даты

1979-02-25—Публикация

1976-08-23—Подача