(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ПЕРИФЕРИЙНЫМИ УСТРОЙСТВАМИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1977 |

|

SU648974A1 |

| Устройство для прерывания программ | 1985 |

|

SU1341636A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1989 |

|

SU1658163A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения процессоров в мультипроцессорной системе | 1984 |

|

SU1188747A1 |

| Мажоритарно-резервированная магистральная модульная вычислительная система | 1986 |

|

SU1457643A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

Изобретение относится к вычислительной технике и может быть использовано jofia сопряжения электронных вычислительных машин (ЭВК), имеющих общесистемный интерфейс типа Общая шина (ОШ), с цифровыми системами, в частносзд с системами реального времени. . ,.,; , -. . , ,

Известны устройства для сопряжения цифровой вычислительной машины с разнотипными по скорости передачи данных внешиими устройствагди, содержащир обратимый преобразователь послёдоватёльНОгб Кода в параллельный, блок согласования форматов, блок дешифрациипризнаков, блок буферной пагляти и дифференцирующий элемент

Пр. - : , - . ,- - .. .

Недостатком таких устройств являются большие затраты оборудования при ограниченных функциональных воз oжнocтяx.

Наиболее близким к предлагаемому пс Технической сущности является устройство для сопряжения ЭВМ с периферийным оборудованием, содержащее блок дешифрации адреса, соединенный вхоДс1Ми с соответствуюьшми входами из групп управлЯ1эву1х входов устройства, блок прерываний, соединенный

двусторонней связью с блоком дёшиф рации адреса, выход которого подключен к первым входам регистра данных, регистра адреса, блока шифрации команд, регистра состояний и блока синхронизации, первыйвыход ко.торого соединен с первым входом блока прерываний, подключенного вторьш

10 входом к соответствукадему входу из групп Управляющих входов устройства, блок управления обменом, шифратор СОСТОЯНИЙ, соединенный выходом с первым входом блока формирования адреса запроса связи, второй, третий

15 и четвертый выходаа Которого соединены соответственно с группой информационных входов устройства, вторым выходом блока синхронизации и выходом блока дешифрации адреса,

20 группа выходов блока прерываний под ключена к сорт.ветствуюгрим управляюцим выходам устройства, второй и третий входы блока синхронизации соедщнены соответственно с входом сос-т

25 тояния и входом запроса связи устройства, второй выход блока синхронизации подключен к четвертог у входу регистра данных, к вторым входам регистра данных, к вторым входам ре30гистра и регистра состояний и к третьемувходу блока шифрации команд, выход блока шифрации команд подключен к третьему входу блока синхронизации/ к командному выходу устройства, первый и второй выходы регистра адреса соединены срответственно с группой адресных выходов устройства и с группой информационных выходов устройства,, выход регистра состояний и первый выход регистра данных соединеныс соответ ствующиЛи выходами из группы инфор /Iaциoнныx выходов устройстве, вход и выход регистра данных подключены к соотввтствуквдим входам и выходам из группы информационных входов и выходов устройствау третий вход регистра данных и втсфой 6лс(ка шифрации KONjaHfl еоедщйен с группой инфop Jaциoнныx входов уст ройства, информационные входы шифра тора состояняй соёдинейы с входом и выходом регистра « управляивдий вход п9Д «лючел к второму кдходу; блока; синхрояйзаЦий и перво му BxojEiy блока управления еб1ие ном, первйй: вьгход которого соеди1нен ПЯ.ТЫМ входом блока сиихро ннзаиии, выход блока .мйрования адреса зап роса связи соединен с адрёснь выхр дом устра| ства, двс( вызова и BXQJ5 КОТОРОГО соответственно подкл1рчены к второму и третьему выходам и входу Вло« а управле ния обменом 123. Основным нёдосТаткалда этого уст ройства являются низкое ШсздЁ)одействие и ейэлыаой объем оборудования. Низкое стродействйе устройства обуелавли вается посл:едовательйопараллельным опросом состояний функ ционального МОДУ.ЙЯ (ФМ) .В частйос ти, определение: cwpec i функйиональногр: канала производится за три цик ла опроса г определение адреса функ циональногр блока МФБ) , определение адреса функцибнальнбго элемента (ФЭ), определение адреса кандла. Большой объем оборудования обуславливаетёя Необходимостью рёаЛизгщин в устройстве функции идентификации аапросов связи. Для поиску запросов в автбиомном режиме устройство .сопряжения снабжено блоком формирования адреса запросов и шифратором состояний, организувдими последовательно-параллельный опрос перифери1й ного оборудования и кодирование адресного слова. Кроме того, сложность блокаУправления обменом обусловлена необхо-, димобтью учета различного быстродей ствия периферийных устройств при их параллельном групповом опросе (введение сигнала Шзов 2). Целью изобретения является повышение быстродействия и сокращение объема оборудования путем исключеНИН процесса идентификации запроса связи и совмещения процессов опроса состояния и обмена й анными. Поставленная цель Достигается тем что в устройство, содержащее блок дешифрации адреса, соединенный группой входов с группами адресных и синхронизируюпщх входов устройств, блок прерываний, соединённый пераыми входом и выходом соответственно с первыми выходом и входом блока дешифрации адреса, второй выход которого подключен к первым входам регистра данных, регистра адреса, блока дешифрации команд, регистра состояний и блока синхронизации, первый вьгход которого соединен с вторым входом блока прерываний, подключенного /третьим входом к группе Синхронизирующих входов устройства, группа выходов блока прё1нлваний подключена к группе ущ авляю щих выходов устройства, выход блока Дешифраций команд подключен к командно выходу устройства, первый выход регистра адреса соединён . с ГРУППОЙ адресных выхоДоВ ycTpotiства, а второй с первыми выходами регистра состояний и регистра данных и первсЛ группой информационных выходов устройства, вторые вход и йаХодреГ:нстра данных подключены соответственно, к вторым группам инфор мацйойных входов и выходов устройства, третий вход ре- , гистраданньве и второе вход блока дешифрации команд соединены с первой группой ийформационных входов, устройства, ввёдейы лассивного обмена (ВПО) иблок активного обмена (BAOJI , причем первый выход блока активного обмейа соединен с вто|Ж1м входом блока синхронизации, второй етя;}сод которого соединен с пертзм входом блока активного обмена; а третий Выход - с первым входом блока пассивного обмена, вход- выход которого соединен с входом-выходом регистра состояний, второй выход которого соединен с чётве1 тым входом блока прерываний, первае и вторые группы входов блока прерываний и блока пассивного обмена соединены соответствейно с Группой входов команд и группой входов квитирующих адресов устройства, первый выход блока пассивного обмена соединен с третьим входом блока синхронизации, а второй выход блока, пассивного обмена - с. третьим входом регистра данных, второй выход блока активно го обмена соединен с четвертым вхо дом регистра данных, третьими входами регистра адреса и блока дешифрации команд, группа выходов которого соединена с группой командных выходов устройства, группа входов-выходов, второй вход и группа выходов

блока активного обмена соединены соответственно группой входов-выходо захватов канала, выходом Вызов и группой выходов квитирующего адреса устройства, группа входов регистра состояний соединена 2 группой входо состояния устройства и вторым входо блока активного обмена, третий вход которого соединен с входом ответа устройства, второй выход регистра адреса соединен с пятым входом блока прерывания, третья группа входов и третий вход блока пассивного обмена соединены соответственно с группой входов сшреса и входом вызова устройс ва, а третий и четвертый выходы блока пассивного обмена соединены срответственно с выходом, ответа и выходом состояния устройства .третий выход блока активного обмена .соединен с. третьим входом регистра состояний, причем блок активного обмена содержит регистр, четыре элемента И, два триггера, элемент ИЛИ, элемент НЕ, усилитель и четыре элемента задержки, причем первый вход первого элемента И соединен с первым входом блока активного обмена, второй - с нулевым выходом первого триггера и первым входом второго триггера, а выход с первыми входами второго и третьего элементов И, иахрды которых соединены соответственно с выходами Из группы входов-выходов блока активного обмена и втор1ш входом втрРОГО триггера, выход которого подключен к первому входу четвертого элемента И, вторые входы второго и третьего элементов И подключены к срответству1эщим входам, из группы вхдов-выходов блока активного обмена, второй вход второго элемента И подключён через лемент НЕ к второму входу третьего элемента И, второй вход четвертогр элемента И соединен с входом первого элемента задержки, выход которого подключен к второму выходу блока активного обмена, через регистр - к пятому выходу блока активного обмена.и через второй элемент задержки - к четвертому выходу блока активного обмена и входу третьего элемента задержки, аисрдом соединенного с третьим выходом блока активного обмена и первым входом элемента ИЛИ, второй и третий входы которого подключены соответственно к второму и третьему входам блока активного обмена, а выход через четвертый элемент эадержки - к первому выходу блока активного обмена и входу сброса первр|го триггера, счетным входом соединеного с выходом четвертого элемента И, а вторым выходом через усилитель с входом первого ..элемента задержки, причем блок пассивного обмена содержит дешифратор, шесть элементов И, три элемента ИЛИ, элемент НЕ и элемент задерл;ки, причем первые входы первого и второго элементов И соединены с выходом третьего элемента И, вторые входы - с второй группой входов блока пассивного обмена, выход первого элемента И соединен с вторым выходом бло.ка пассивного обмена и первым входрм первого элемента

0 ИЛИ, входы дешифратора подключены к третьей группе входов блока пассивного обмена, а выходы - к первым входам третьего и четвертого элементов И, вторые входы которых соединены с третьим входом блока пассив5ного обмена, выход второго элемента И соединен с первыми входа1 ш пятого элемента И и второго элемента ИЛИ, вторым входом подключенного к выходу первого элемента ИЛИ и через эле0мент задержки - к третьему выходу блока пассивного обмена, а выходом к первому выходу блока пассивного обмена, второй вход и выход пятого элемента И соединены соответственно

5 с первыми входом и выходом блока пассивного Обмена, входы третьего элемента ИЛИ подключены соответственно к входу-гвыходу и первому входу блока пассивного обмена, а выход - к тре0тьему входу четвертого элемента И и через элемент НЕ - к третьему входу третьего элемента И, первый, второй входы и выход шестого элемента И под сЛючены соответственно к выходу де5шифратора, второй группе входов блока пассивного обмена и входу-выходу блока пассивного обмена, второй вход первого элемента ИЛИ соединен с выходом пятого элемента И.

0

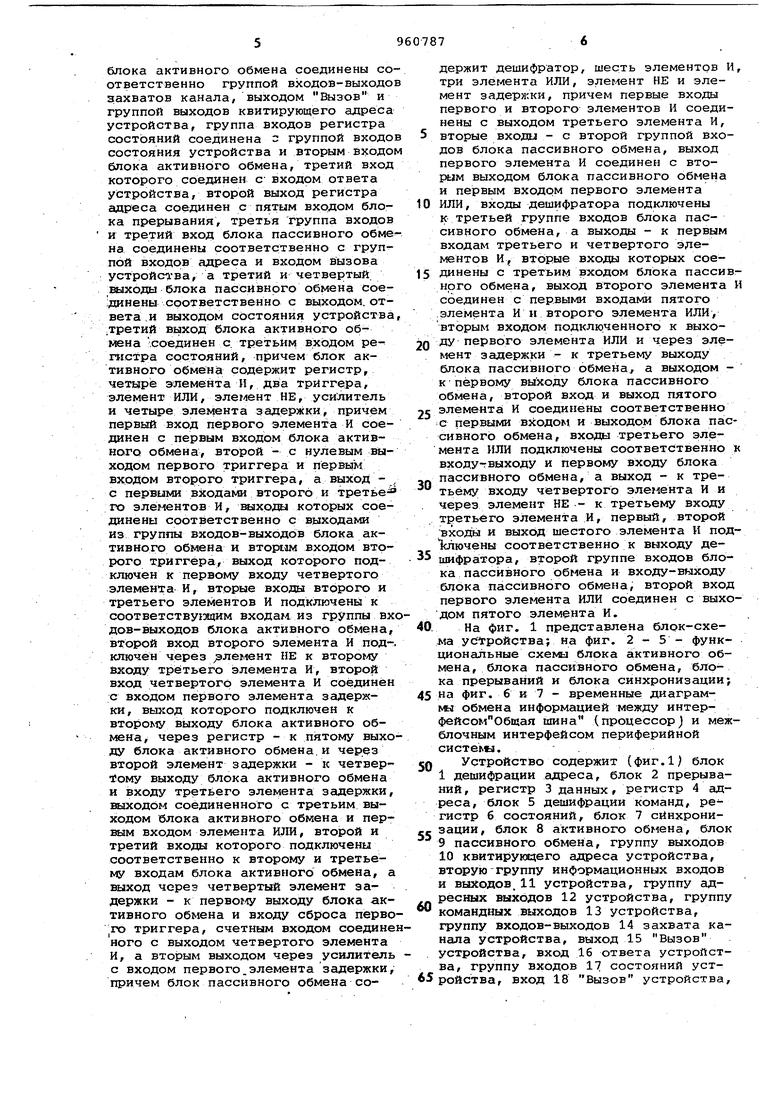

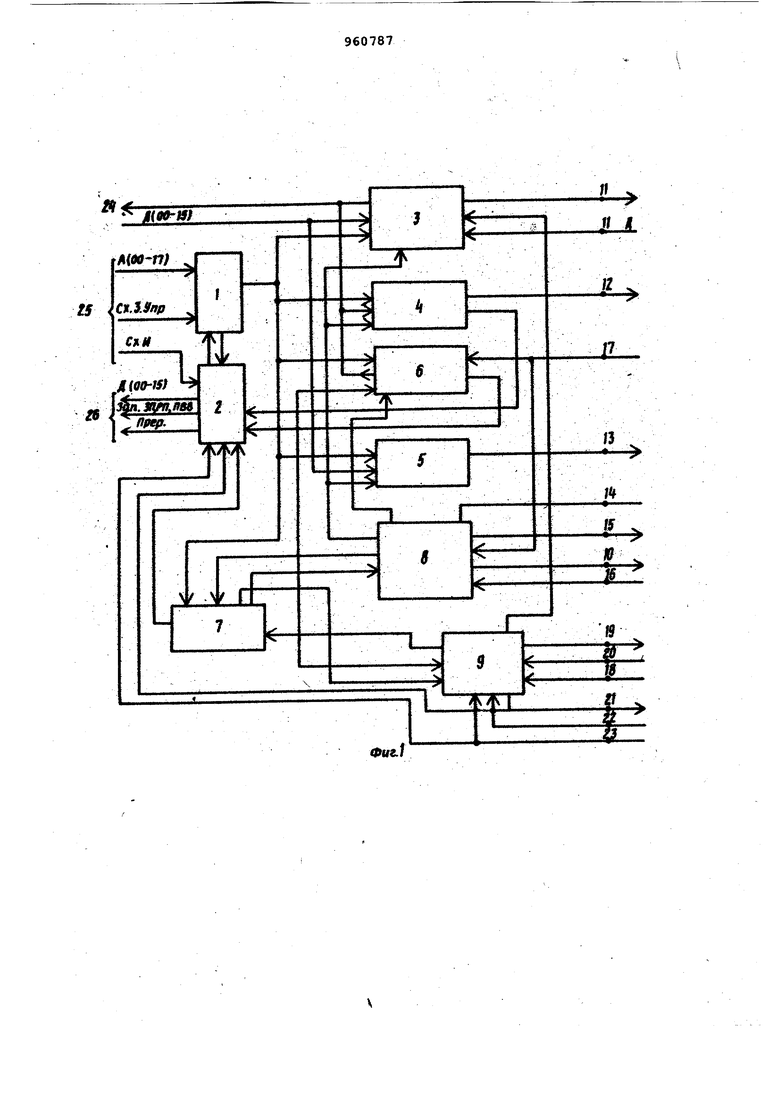

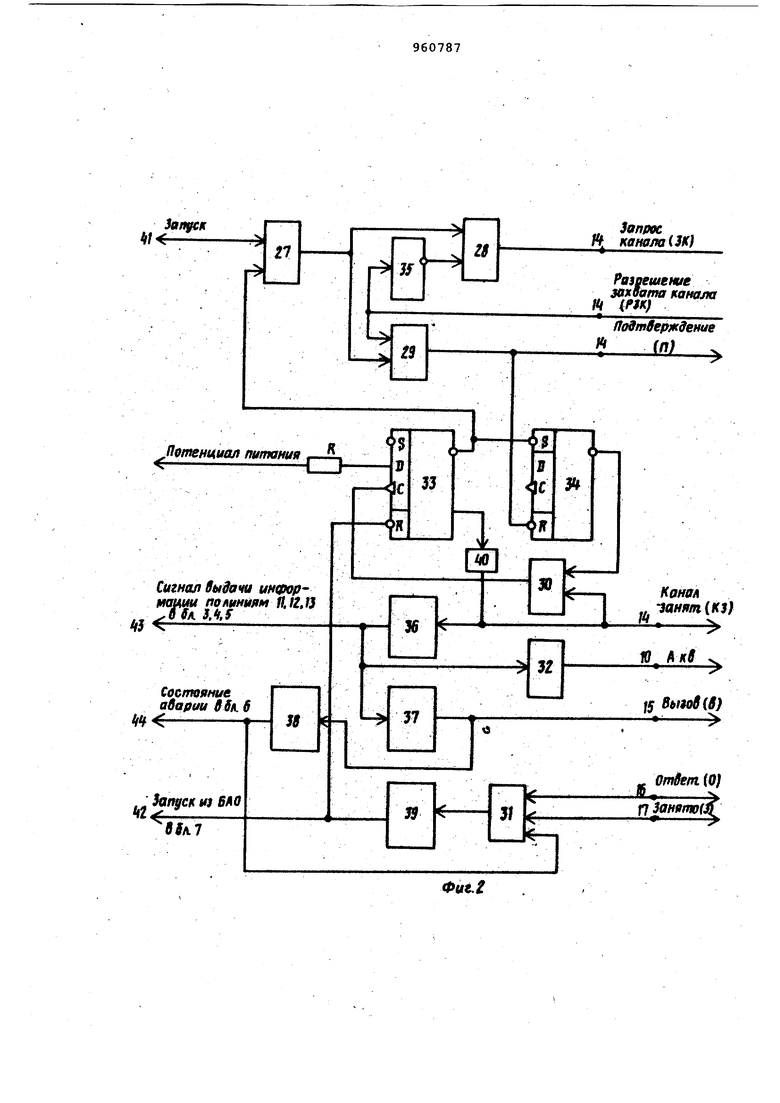

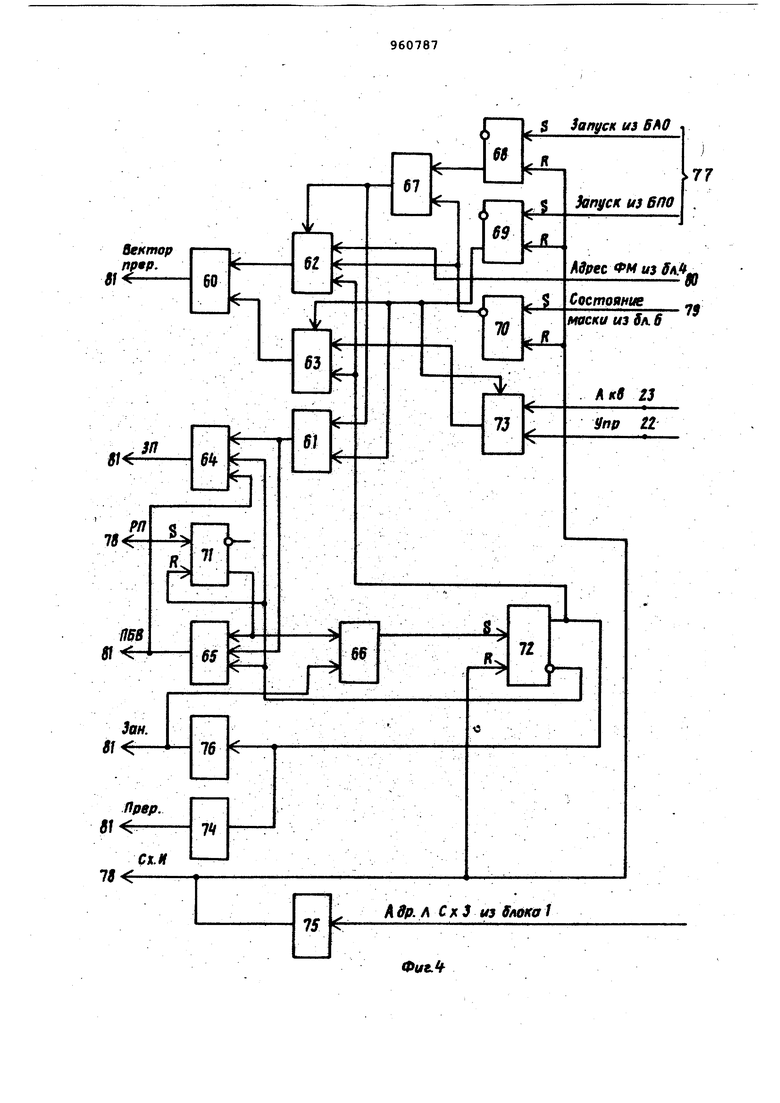

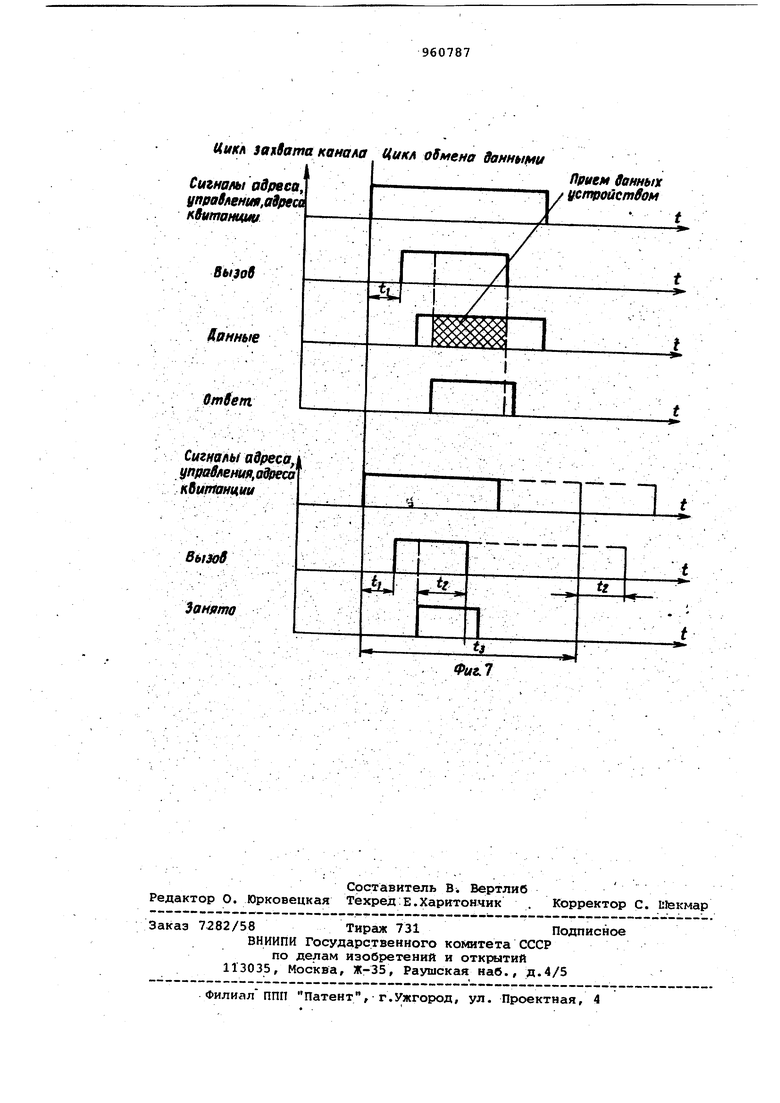

На фиг. 1 представлена блрк-схема ус ройства; на фиг. 2 - 5 - функциональные схемы блока активного обмена, блока пассивного обмена, блока прерываний и блока синхронизации; на фиг. 6 и 7 - временные диаграм5мы обмена информацией между интерфейсом Об1цая шина (процессор) и межблочным интерфейсом периферийной систем.

Устройство содержит (фиг.1) блок

0 1 дешифрации адреса, блок 2 прерываний, регистр 3 данных, регистр 4 адреса, блок 5 дешифрации команд, регистр б состояний, блок 7 синхронизации, блок 8 активного обмена, блок

5

9пассивного обмена, группу выходов

10квитирующего адреса устройства, вторую-группу информационных входов и выходов,11 устройства, группу адресных выходов 12 устройства, группу

0 командЕШХ выходов 13 устройства, группу входов-выходов 14 захвата канала устройства, выход 15 Вызов устройства, вход 16 ответа устройства, группу входов 17 состояний уст5ройства, вход 18 Вызов устройства. выход 19 ответа устройства, группу входов 20 адреса устройства, выход 21 состояния устройства, группу входов 22 команд устройства, гру пу входов 23 квитирующих адресов ус ройства, входы и выходы...24 первой группы информационных входов-выходо устройства, входы 25 группы управля кхцих входов устройства,. адресные и синхронизиругодие (управлякмдае ) выхо ды 26 устройства. Блок 1 дешифрации адреса производи выбор адресуекыхСпо ОШ) регистров устрЬйства, а также осуществляет расшифровку управлявших сигналов (запись, чтение . Блок 2 прерываний организует захват Ьбщей шины в целях прерывания процессора, формирует и хранит значение вектора прерывания. Блок 8 активного обмена содер/сит (фиг. 2) элементы И 27-30, элемент ИЛИ 31, регистр 32, триггеры 3 и 34, элемент НЕ 35, элементы 36-39 задержки, усилитель 40, перввй вход 41, первый, второй и третий выхо- ды 42-44. Блок 9 пассивного обмена содержит (фиг. 3) элементы И 45 - 50, элементы ИЛИ 51-53, дешнфратор 54, элемент НЕ 55, элемент, 56 задержки, первый вход 57 блока, вход-Выход 58 блока и второй выход 59 блока. Блок 2 прерываний содержит (фиг. элементы ИЛИ 60 и 61, элементы И 6267, триггеры 68-72 регистр 73, элементы 74 и 75 задержки, усилитель 7 входы 77-80 блока и выходы 81 группы выходов блока,. , . .„.. Блок 7 синхронизации (фиг. 5) содержит дешифраторы 82-84, элементы И 8 и 86, триггер 87у элемент НЕ 88, уси литель 89, элемент 90 задержки, входы 91 - 93 и вауода 95 - 96 блок На чертежах приняты следующие сок ращенные обозначения входов и выходов со стороны интерфейса СЯЯ: Д(00-15) - группа шин Даншле А(00-17} - группа шин nfit. , Адрес СхЗ; - Синхронизация заДатчика, -группа шин Управление - Синхронизация исполнителя, - Занято, -группа ишн Запрос передачи, -группа шин Разрешение передачи, - Подтверждение выборки - Прерывание. Устройство работает следукадим образом, РассмотЕШм вначале работу устройства при обмене данными по инициативе процессора. , Связь процессора с устройством ос 1а1ествляется на уровне регистров устройства, а пересылка данных между устройством и периферийными блоками и поиск запросов связи производится без участия процессора. Регистры 3, 4 и 6 и блок 5 доступны ;процессору, и последний гложет производить обращение к ним в режимах записи и чтения в соответствии с алгоритмом функционирования интерфейса ОШ. Обращение процессора к регистрам устройства осуществляется в следующих целях: засылка данных в регистр 3 или чтение данных с регистра 3; . засылка в регистр 4 адреса функционального модуля, к которому требуется произвести обращение для ввода или вывода информации; з асылка в блок 5 сигналов, предписывающих адресуемому функциональному модулю те или иные действия (ввод, вывод, пуск, сброс и т.д.); чтение кода состояний из регистра 6; а также установка масок в регистре 6, Процедура передачи данных из промессора в функциональный модуль заключается в еле думцем. Процессор производит засылку данных в регистр 3, адреса обращения в регистр 4 и программного кода, соответствующего режиму Ввод, в блок 5. После этого процессор откЛ1очается и устройство автономно организоаывает цикл обмена по межблочному интерфейсу в соответствии с диаграммой (фиг, 6)i Блок 7 синхронизации запускает блок 8, Блок 8 организовывает захват межблочного интерфейса. Затем на вторую группу информационных входов- выходов 11 из регистра 3 данных выдаются данные, на группу адресных- выходов 12 из регистра 4 адреса - значение адреса обращения, на группу командных; выходов 13 - значение кода команда управления и на группу выходов 10 адреса квитанции код адреса квитанции устройства в адресах межблочного интерфейсного канала. Спустя фиксированную задержку врегдани t, необходимую для распознавания адреса и команд управления ФМ, блок 8 . на выходе 15 сигнал Вызов. Адаесуенвлй ФМ по СИР налу .Вызов начииает рыпо нение предписаний команды управления (в данном случае, прием данных с второй груп1ш информационных входов-выходов 11) и посла ее выполнения извё1цает устройство об этом сигналом Ответ по входу 16, По сигналу Ответ блок 8 через фиксированпую задержку t снимает сигнал , адресные, команд«je и информационные сигналы с магистрали интерфейса, В случае, если адресуемый ФМ занят или неисправен, он в ответ на сигнал Шзов выдает соответственно сигнал Занято или ничего не вьщает (через время t после сигнала Вызов это воспринимает ся устройством как признак неисправ ности .ОМ, который передается в регистр б состояний). В обоих случаях блок 8 через фиксированную задержку снимает сигнал Вызов, адресные, командные и информационные сигналы с магистрали ин терфейса. Затем бло.к 8 через блок 7 запускает блок 2 прерываний. Блок 2 формирует вектор прерываний В по признакам: В Код адреса ФМ Л При нак состояния ФМ, которые поступают на соответствующие входы блока 2 из регистра 4 .и регистра, 6. Зате блок производит операцию Прерывание в соответствии с процедурами ОТ. Так.им образом, процессор узнает о том, что переданный байт информации не принят ФМ. При этом в межблочном Интерфейсе происходит совмещение операции опроса состоя ния ФМ с операцией передачи байта информации. : . На этом процесс передачи данных . из процессора в ФМ заканчив ается. Передача данных из ФМ в процессор осуществляется следующим образом. Процессор производит засылку ад,реса сообщения в регистр 4 адреса и (кода команды управления Вывод в блок 5 депшфрации команд. Далее ус: ройство осуществляет автономный цикл обмена с ФМ (фиг.7). Блок 7 синхронизации запускает блок 8, который организует захват межблочного иытер йса. подклгоче- ние адресных сигналов из регистра 4 адреса на группу адресных выходов 12,. сигналов блока 5 деыифрации команд на группу командных выходов 13 и на группу выходов 10.адреса квитанции - код адресаквитанции .устройства-. Спустя время t 8 выдает сигнал Вызов. АдоесуёмыйФМ в режиме Выврд по сигналу Вызов выдает информационные сигналы на вхо из группы информационных входов -выходов 11 и выдает сигналы Ответу (данные выставлены) или только Заня то, или ничего не выдает, если он несправен (Авария). По сигналу -Занято или Авария блок В через выдержку времени t-j снимает сигнал Вызов и затем адресные и командные сигналы. По сигналу Ответ уст ройство принимает данные, затем снимает сигнал Вызов. По снятию сигнала Вызов ФМ снимает сигнал Отве После этого блок 8 через блок 7 запускает блок 2 прерываний. При этом формируется соответствующий вектор прерывания в соответствии с информацией из регистра 4 адреса и регистра 6 состояний. Процессор про изводит съем данных из регистра 3 , по соответствующему вектору прерыва ния.Обмен данными по инициативе ФМ происходит следукяцим образом. На входы блока 9 поступают следующие сигнал) из межблочного. интерфейса; на вход 20 - адреса устройства; на вход 22 и вход блока 2 прерываний - команд управления; на вход 23 и вход блока 2 прерываний адреса ФМ. На вход 11 регистра 3 данных в случае режима ввода в процессор сигнал информсщии. Перечисленные сигналы анализируются блоком 9. , По сигналу Вызов, поступаквдему на вход 18 блока У пассивного обме:на с задержкой t относительно перечисленньЬс выше сигналов, блок 9 пассивного обмена выполняет, предписанную команду управления. Перед началом выполнения команды управления блок 9 анализирует состояние маски прерывания по дсоду адреса квитанции ФМ, поступающему на вход 23. Если маска по этому адресу не разрешает прерывания, то блок 9 не выполняет команды управления, поступивше.й от ФМ, и выдает в ответ на сигнал Вызов ответный сигнал Занято по выходу 21, . по которому ФМ снимает все остальные сигналы с магистрали интерфейса. Если маска разрешает прерывание по адресу данного ФН, блок 9 приступает к выполнению команд управления. В случае, если была команда ввода данных в процессор, блок 9 производит запись информации в регистре 3 данных, через блок 7 синхронизации запускает блок 2 прерываний, который по информации на входах 22. и 23 формирует вектор прерывания. Затем блрк 9 выдает сигнал Ответ (данные приняты) по выходу 19, по которому ФМ снимает все сигналы.с интерфейсного канала. Блок 2 производит операцию Прерывание в ОШ и процессор считывает информацию с регистра 3 данных. В случае, если была команда вывода данных из процессора, блок 9 через блок 7 запускает блок 2, который по информации на входах 22 и 23 формирует вектор прерывания, требующий вывода информации, В Адрес квитанции ФИ Л Код команды управления. Процессор засылает информацию в регистр 3 данных и через -блок 7 извещает блок 9 о том., что данные находятся в регистре 3. По этому сигналу блок 9 выдает информацию на вторую группу информационных входов-.выходов 11 и выдает сигнал Ответ (данные выданы). ФМ по сигналу Ответ, производит прием данных и снимает сигналы с входов 18, 22 и 23. При снятии сигна:ла Вызов блок 9 снимает сигнал ответ. На этом цикл обмена данными по инициативе ФМ заканчивается. Блок 2 прерываний работает следзпощим образом. Работа блока 2 прерывания {фиг.4 начинается с прихода по входу 77 сигналов Запуск из БЛО или Запуск из БПО, поступающих из блока синхронизации. При приходе сигнала Запуск из БАО на выходе, триггера 68 появляется сигнал разрешения, который при разрешении прерывания триггером 70 подготавливает элемент И 62 и через элемент ИЛИ 61 поступает на входа элементов И 64 и 65. В исходном сое тонкий с инверсного выхода триггера 72 поступает разрешакяций сигнал, поэтому при приходе разреша кнцего си нала на вход элемента И 64 последний выдает сигнал Запрос передачи « интерфейс Ш в случае, если- в СЯИ нет сигнала Подтверждение выборки В случае наличия этого сигнала элемент И 64 ожидает его окончания. В ответ на сигнал Запрос пербдачй из СЯИ приходит сигнал Разрешение передачи, который опрокидывает триггер 71 и на его выходе появляе разрешанхций сигнал, по которому .элемент И 65 выдает в ОШ сигнал По тверждение выборки, так Kcuc на его других входах уже установлены разрешающие сигналы. По сигналу Подтверждение выборки ОШ снимает сигнал Разрешение передачи, а элемен И 64 снимает Запрос передачи. Эле мент И 66 анализирует состояние шины Занято ОШ. Если в СЯИ уже установлен сигнал Занято, то элемент И 66 ожидает его окончания, если же сигнал Занято отсутствует, то элемент И 66 опрокидывает триггер 7 с инверсного выхода которого через усилитель 76 выдается сигнал Занято в ОШ и разрешается прохождение вектора прерывания через элементы.И 62 и ИЛИ 60 на шины данных Д(00-07) ОШ и через элемент 74 задержки ййь дается сигнал Прерывание в ОШ. По сигналу Прерыва 1ие ЭВМ воспринимает .вектор прерывания и выдает на вход 78 сигнал Синхронизация исполнителя, -который поступает на входа сброса триггеров 68, 69 и 72,/устанавливая их в исходное состояние. Триггер 70 управляется сигналом из блока 6, поступавядам в кюмент, когда ЭВМ устанавливает в блоке 6 состояние ФМ, адрес которого записан в блоке 4. Таким образом, состо|1ние триггера 70 отображает состояние маски прерывания того ФМ, с которым в текущий момент времени производится обмен информацией. На этом цикл работы блока прерывания заканчивается. При поступлении гго входу 77 сигнала Запуск из БПО блок прерывания работает аналогичным образом за исключением того, что сигнал разрешения появляется на выходе триггера 69, по которому подготавливается элемент И 63, а вектор прерывания формируется в регистре 73 по кодам на входы 22 и 23 и при наличии разрешакадего сигнала на выходе триггера 69. При обращении к устройству сопряжения состороны ЭВМ последняя выставляет на шинах интерфейса ОШ код адреса устройства, команду управления и сигнал Синхронизация задатчика, по которым в блоке 1 дешифрации адреса формируется сигнал А др.ЛСхЗ, который поступает на вход элемента 75 задержки, который после задержки t-j формирует сигнал Синхронизация исполнителя в ОШ. Блок 7 работает следующим образом. В режиме обмена данным по иници- ативё процессора последний (фи г.5) обращается к блокам 6, 3, 4 и 5 в указанной последовательности, т.е. обращение к:. блоку 5 однозначно определяет начало aBTciHoNiHorp обмен.а устройства сопряжения через межблочный интерфейс с зада«ньш в блоке 4 ФМ. Поэтому при поступлении из блока 1 адреса блока 5 дешифратор 82 нвдаёт сигнал, ус-Ганавливагадий триггер 87 в единичное состояние, при котором с прямого выхода поступает разрешакнций сигнал на вход элемента И 85. Если при этом из блока 9 нет сигнала Запуск из БПО (т.е. нет обращения какого-либо ФМ по межблочному интерфейсу к устройству сопряжения), то на выходе элемента НЕ 80 также устанавливается разрешашций сигнал. ПРИ этом элемент И 85 выдает сигнал Запуск в блик 8 и на вход усилителя 89, с выхода кото рого сигнал Занйто поступает в блок 9. После окончания авт о-номного цикла обмена по межблочному интерфейсу из блока 8 поступает сигнал Запуск из БАО,по которому триггер 87 Опрокидывает в исходное состояние и тогда снимаются сигнаинд Запуск и Занято и в блок 2 запускается цикл прерывания ЭВМ. При обращении ЭВМ к блоку 3 с командой записи дешифраторы 83 и 84 выдают разрешакяцие сигналы на входы элемента И 86, при этом за- пускает элемент 90 задержки. Через время задержки на выходе элемента 90 задержки появляется сигнал Зат пись данны:; в блоке 3 окончена, который поступает в блок 9. Блок 8 активного обмена осуществляет опергщию асинхронного обмена данными по межблочному интерфейсу по инициативе процессора и работает, следующим образом. Работа блока 8 (фиг.2) начинается с прихода сигнала Запуск из блока 7 на вход элемента И 27. Триггер 33 в исходном состоянии разрешает прохождение сигнала Запуск на входы элементов И 28 и 29./;В исходном состоянии сигнал Разрешение эах вата канала на входе 14 отсутствует, поэтому сигналь на входах элемента И 28 формируют сигнал Запрос канала. В ответ на сигнал ЗапросГ канала приходит сигнал Разрешение захвата канала, по которому .снимается сигнал Запрос канала и элементом И 29 формируется сигн Подтверзкдёние, который поступает в канал и на вход триггера 34,, при ;этрм единичный сигнал с нул евого выходу поступит на первый вход элемента И 30. В ответ на сигнал Подтверж дение снимает сигнал Разреше ние захвата канала, при этом снимается сигнал Подтвераденйе. При отсутствий сигнала Канал занят сигнал с выхода элемента И 30 устанавливает, в единичное состояние триг гер 33. Сигнал с нулевот выхода триггера 33 запрещает повторное про хождение сигнала Запуск через элемент И 27 и приводит триггер 34 ,в исхрдаое состояние, а с прямого выХоДа сигнал поступает на вход усилителя 40. G выхода усилителя 40 фор мируется сигнал Канал занят, который поступает в канал для сигнали,зации ФМ о том, что канал занят устройством через элемент 36 задержки и на вход элемента И 30, запрещая повторный запуск триггера 33. Через заданную задержку элемент 36 задержки лдает сигнгш выдачи данных, алреса квитанции .и команды управления в блоки 3 - 5 и регистр 32 Одновременно этот сигнал поступает на вход элемента 37 задержки, интервала задержки с в ахода ко торогр в канал поступает сигнал Вызов и запускается элемент 38 задержки. Лалее может быть два варианта. Первый вариант. По входу 16 прцходит сигнал Ответ на вход элемен та ИЛИ 31, который запускает элемент 39 задержки. Через время задержки сигнал с этого элемента возвращает исходное состояние триггер 33 (при этом снимается сигнал Канал занят который сбрасывает элементы 36 и 37 задержки (при этом снимаются сигналы Вызов на выходе 15 и выдачи ин формации по линиям 10-13) и поступа ет в блок 7 синхронизации для организации прерывания (сигнал Запуск из ВАО). При снятии сигнала Вызов снимается сигнал Ответ. Бели с мо мента выдачи сигнала Вызов сигна Ответ не пришел в течение заданно го времени, то сигнал с выхода элемента 38 задержки устанавливает признак неисправности ФМ и через элемент ИЛИ 31 ПРОИЗВОДИТ действия аналогичные сигналу Ответ, На этом цикл по первому варианту заканчивается. -Второй вариант. Приходит -сигнал Занято по входу 17. В этом случае устанавливается признак ФМ занят в блоке б. В остальном сигнал Занято через элёь мент ИЛИ 31 производит действия, аналогичные действиям сигнала Ответ в первом варианте. Блок 9 пассивного обмена осуществляет операции асинхронного обмена данными по межблочному интерфейсу по инициативе функциональных модулей и работает следующим Образом. Работа блока (фиг. 3) начинается с прихода по входам .20 кода адреса присвоенного устройству сопряжения. В этом случае сигнал с выхода двшифратора 54 подготавливает элементы И 47, 48 и 50. Сигналы команд управления (Запись или Чтение) по вхоW 22 поступают на элементы И 45 (Запись) и 46 (Чтение). Сигналы на входах 23 определяют адрес ФМ, обратившего к устройству, и поступают черезЭлемент И 50 в блок 6, откуда на Элемент ИЛИ 53 поступает соответствующий сигнал, разрешающий или запрещающий работу устройства опряжения с данными ФМ. Кроме того, на другой вход элемента ИЛИ 53 может поступить сигнал Занято из блока 7. Сигнал запрещения ра;боты с ФМ поступает на вход элемента И 48 с выхода элемента ИЛИ 53. При этом при появлении сигнала Вызов на выходе элемента И 48 появляется сигнал Занято, выдаваемый на выход 21 и сигнализирующий о занятости устройства сопряжения для данного ФМ. В этом случае сиг-налом с выхода элемента НЕ 55 запрещается прохождение сигнала йлзов через элемент И 47. В случае разрешения работы с данным ФМ.с 5гНал с выхода элемента ИЛИ 53 запрещает по элементу И 48 выдачу ригнала Занято а с выхода элемен 55 разрешает прохождение сигнала Выаов на входа элементов И 45 и 46. ЕСЛИ при этом была команда За- s пись то с выхода элемента И 45 сигнал записи данных поступает в :блок 3 для стробирования данных :и на вход элемента ИЛИ 51, с выхода которого сигнал запускает элемент 56 задержки, который через заданное время выдает в канал сигнал Ответ Сигнал с выхода элемента ИЛИ 51 одновременнр через элемент ИЛИ 52 выдает сигнал Запуск из БПО в блок 7 о необходимости прерывания ЭВМ. На этом цикл записи в устройство сопряикения заканчивается. Если была команда Чтение, то с выхода элемента И 46 через элемент ИЛИ 52 .выдается сигнал Запуск из БПО в блок 7. После окончания записи данных процессором в регистр 3 данных поступает сигнал окончания записи данных, по которому сигнал с выхода элемента И 49 стробирует выдачу дан ных на выходах 11 канала и через элемент ИЛИ 51 элемент .56 задержки для выдачи сигнала Ответ. На этом цикл чтения данных из устройства сопряжения по инициативе ФМ заканчивается . Таким образом, введение в устрой ство блоков активного и пассивного обмена позволяет вести обмен данными между процессором и ФМ по иницит ативе процессора, совмещая при этом в межблочном интерфейсе цикл опроса состояния ФМ и цикл обмена информацией, и по инициативе ФМ, исключая при этом цикл вдентификации инициативного ФМ. Это позволяет сократить объем оборудования и увеличит быстродействие обмена, особенно важное в .системах реального Bpetieни. Формула изобретения Устройство для сопряжения вычислительной машины с периферийными устройствами, содержащее блок детаиф рации адреса, соединенней группой входов с группой адресных и синхронизирующих входов устройства, блок прерываний, соединенный первыми вхо дом и выходом соответственно с первым выходом и входом блока дешифрации адреса, выход которого Подключен к первым входам регистра данных /регистра адреса, блока дешифра ции команд,регистра состояний и 1блока синхронизации, первый выход которого соединен с вторым входом блока прерываний, подключенного третьим входом к группе синхронизирующих входов устройства, группа выходов блока Прерываний подключена к группе управляющих выходов устройства, выход блока команд прд слючен к командному илходу устройства, первый выход регистра адреса соединен с группой адресных у стройства, а второй вход - с перрыми выходами регистра состояний и .регистра данных и первой группой ин формационных выходов устройства, вторые вход и выход регистраданных подключены соответственно-. к вторым группам информационных входов и выходов устройства, третий вход регистра данных и второй вход блока. дешифрации команд соединены с первой группой информационных входов устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок пассивного обмена и блок активного обмена, причем первый выход блока активного обмена соединен с вторым входом блока синхронизации, второй выход которого соединен с первым входом блока активного обмена, а третий выход - с первым входом блока пассивного обмена, вход-выход которого соединен с входом-выходом регистра состояний, второй выход которого соединен с четвертым входом блока прерываний, первые и вторые группы входов блока прерывания и блока, пассивного обмена соединены соответственно с группой входов команд и группой квитирующих адресов устройства, первый, выход блока пассивного обмена соединен с третьим входом блока синхронизации, а второй выход блока пассивного обмена с третьим входом регистра данных, второй выход блока активного обмена соединен с четвертым входом регистра данных, третьйют входами регистра адреса и блока дешифрации команд, группа выходов которого соединена с группой командных выходов устройства , группа входов-выходов,второй вход и группа выходов блока активного обмена соединены соответственно с группой входов-выходов захватов канала, выходом Вызов. и группой выходов квитирующего адреса: устройства, группа входов регистра состояний соединека с группой входов состояния устройства и вторам входом блока активного обмена, третий вход которого соединен с входом ответа устройства, второй выход регистра адреса соединен с пятым входом блока прерывания, третья группа входов и третий вход блока пассивного обмена соединены соответственно с группой входов адреса и входом вызова устройства, а третий и четвертый выходы блока пассивиогю обмена соединены соответственно с выходом ответа и выходом состояния устройства, третий выход блока активного обмена соединен с третьим входом регистра СОСТОЯНИЙ, причем блок активного обмена содержит регистр, четыре элемента И, два триггера, эле.меит ИЛИ, элемент НЕ, усилител.ь и (четыре элемента задержки, причем первый вход первого элемента И соединен с первым входом блока активного обмена, второй - с нулевым выходом первого тригх ра и первом входом второго триггера, а выход - с первыми входами второго и третьего элементов И, выходы которых соединены соответственно с выходами из группы входов-выходов блока активного обмена и втоЕжям входом второго триггера, выход которого подключен к первому входу четвертого элемента И, вторые

входы второго и третьего элементов И подключены к соответствующим входам из группы входов-выходов блока активного обмена, второй вход второго элемента И подключен через элемент НЕ к второму входу третьего элемента И, второй вход четвертого элемента И соединен с входом первого эле гмента задержки, выход которого подключен к второму выходу блока активного обмена, через регистр - к пятому выходу блока ак- ивного обмена и через второй элемейт задержки - к четвертому выходу блока активного обмена и входу третьего элемента задержки, выходом соединенного с третьим выходом блока активного обмена и первым входом элемента ИЛИ, второй и третий входы которого подключены соответственно к второму и третьему входам блока активного обмена, а выход через четвертый элемент задержки - к первому выходу блока активного обмена и входу сброса первого триггера, счетным входом соединенного с выходов четвертого элемента И, а вторым выходом через усилитель - с входом первого элемента задержки, причем блок пассивного обмена содержит дешифратор, шесть элелюнтов И, три элемента HJIH, элемент НЕ и элемент задержки причем й перкле входы первого и второго элементов И соединены с выходом третьего элемента И, вторые входол - с второй группой входов блока пассивного обмена, выход первого элемента И . соединен с вторым выходом блока пассивного обмена и первым входом первого элемента ИЛИ, входы дешифратора; подключены к третьей группе входов блока пассивного обмена, а выходы к первым входам третьего и четвертого элементов И, вторые входы кото.рых соединены с третьим входом блока пассивного обмена, выход второго элемента И соединен с первыми входами пятого элемента И и второго элемента ИЛИ, вторым входом подключенного к выходу первого элемента ИЛИ и через элемент задержки - к третьему выходу блока пассивного обмена, а выходом - к первому выходу блока пассивного обмена, второй

5 вход и выход пятого элемента И соединены соответственно с первыми входом и выходом блока пассивного,обмена, входы третьего элемента ИЛИ подключены соответственно к входуQ выходу и первому входу блока пассивного обмена, а выход - к третьему входу четвертого элемента И и через элемент НЕ - к третьему входу третьего элемента И, первый, второй входы

5 и выход шестого элемента И подключены соответственно к выходу дгаиифратора, второй группе входов блока пассивного обмена и входу-выходу блока, второй вход первого элемента ИЛИ соединен с выходом пятого элеdмента И.

Источники информации, принятые во внимание при экспертизе

5

Фиг.

5

t w

55

77

Запуск u) бПО

6t

60

63

51

4

5

РП

75 7/

е

Ш

J

Jff//. 5f

76

81

74

CK.H

75

Адресам из ffл.f,

90 79

Состояние

маска из 5л. 6

i

Акв 23

Упр П

73

.

7Z

А 9р. А из SMKO 1

Фиг.

Из блока /

П

87

«t«.

г- ВУлок2

:

9if

S SAOK2

Запуск из бПО

HtfMKa

W

91

S8

/

33

Занятой

6д

6SK.9

Фиг.6

UuKK захвата канала ЦикА оИмена данными

Сигмам адрвси, 11пра8мнив,а9ресй к9итан14ии

вызов

Данные

Omfen

Сигналы адреса, управлений, кОигпаиции

Вмзов Занято

Авторы

Даты

1982-09-23—Публикация

1981-02-11—Подача