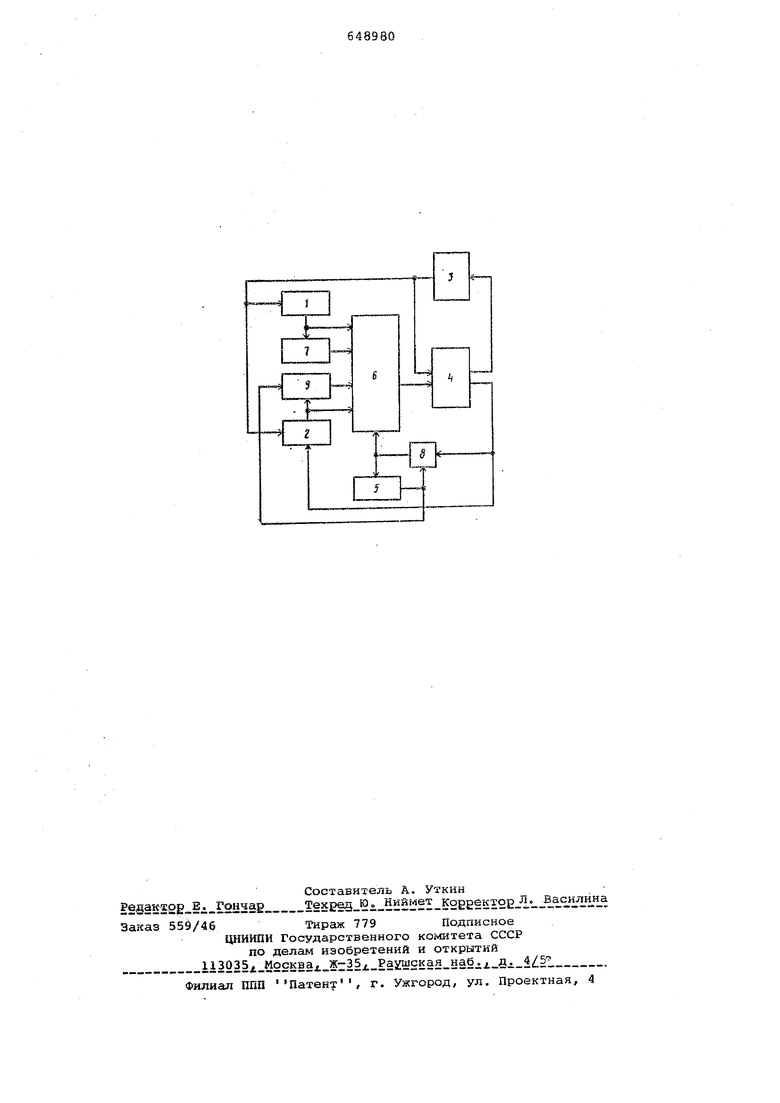

тичных произведений 4, блок упразлёния 5, блок 6 формирования частичных произведений г б.пок 7 .пекия обратной величины, элемент И В ком.мутатор множителя 9,, Устройство работает оладую1П11м образом. Операции умножения и деления вы-долняются над п-разрядиыми г ор:мали-эованными числами f величии ч KOTDIJHX заключена в диапазоне от --- до 1, где m - основаий,е систе м счислепия, При выполнении операции умнсжеь:ий множитель располагается в регистре 2 множимое - в регистре 1, про-изаеденке образуется в регистре 2 (сзтар1 разряды) , в регистре 3 (младшие разряды),элемент И 8 сигналом из блока управления 5 закрыт Блок б формирования частмчг;ь}л произведений вырабатывает частичные произведения множимого на группы из К () разрядов множителя, поступающие из регистра 2 через коммхтатор множителя 9. Коммутатор 9 cHi налом из блока управления 5 переключается таким образом.- что при уыьожении очередная группа разрядо.в мп.ожителя выбирается из К старших разрядов регистра 2, а при ддалении . из К младших разрядов этого же ре-Гкстра. Cy 1мaтop частичных пронззедений 4 выполняет сложение со еряснгдо го регистра 3 с очередньЕ 1 част 1чным произведением, результат сложеЕ;ия записывается в регистр накол.чемия 3 разрядность которого увеличена на К+1 разряд. Перед началом умножен ;-; которое начинается со старлмх ргкзря дов, регистр 3 сбрасывается в кколь, В первом цикле умножения на вкод блока 6 формирования частичных lipoизведений поступают мнокимое из ре-гистра 1 и К старших разрядов множи теля из регистра 2 через кок -гута гор множуггеля 9, в блоке 6 выполняется их перемножение и частичное дение поступает на вход суммсПо за частичных произведе п-1й 4, где склад вается с содержимым регистра 3, Результат сложения записывается в, регистр 3. Затем производится сдвиг влево на К разрядов регистров 2 и 3 при этом содержимое старших регистра 3 передается в раз ряды регистра 2, В каждом последующем Ц)кле у.з старших 1:эазрядов регистра 2 -герез Йоммутатор 9 выбирается очередная группа разрядов множителя- и описган«ые действия повторяются. Возникающие при суммихзовании час тичных произведений- переносы в стар шие разряды, перешедшие из регистра 3 в регистр 2, подаются с выхода су матора 4 на счетный вход регистргг 2 который выполнен в виде регистрасчетчика.- После выполнения циклов , где п - разрядность coMi-ToKsrreП4ен,р регистре 2 образуется И старших азрядов произведений, в регистре падшая половина произведений, на том процесс умножения заканчивается. При выполнении деления вначале деiKMos размещается в регистре 2, а деитель - Е регистре 1. Операдия делеия разбивается на 2 этапа. На первом тапе определяется приближенное знаение обратной величины делителя аходятся значения DO.E де С - делимое; В - делитель; D,, - приближенное значение велиопределения величины D -по-Г1ж; а быть такой, чтобы обеспечивассь выполнение условия .-H.-m-)-D,- (3) Величина Dp определяется с помощью б-iiOKa вычисления обратной ве шчины 7, ксторый может быть выполнен, наприглео,- на основе таблицы обратных ве-;v4Hti , Не; ВХОД б-пока 7 из регистра 1 подается КМ-2 старших разрядов делителя к.,- 0,, ,.. Ь., о .В соответствии им в 1 ;.i6j; me обратных величин блока 7 поставлено (К+1) разрядное число D,.,, inaeii.cTcTiHJiHKjiJiee собой (К+1) старший ра;;ря,а частного от деления деления на . ъели нну (О , Ь Ь, И Cinova 1 величина D,-, подается в fxiioi-; б формирования частичных произве:::eii -ii;, одновременно на другой вход &-1к;ка б поступает делитель из регистра 1. Произведение B-DO образуется за 2ни-лла, В первом цикле в блоке б фг.;рг,йтрования частичных произведений 1и-1::олнг :ется перемножение делителя В Не) пу-леаой разряд величины П полученii-jt ластичное прсизведение через сумм.;;;.--ор 4 передается в регистр 3 . Затем в -блоке 6 образуется произведение 3на К дробных разрядов величины Dp н полученное частнчшое произведение -;рибавляется к предварительно сдви- нутому влево содержимому регистра 3. Величина Е находится как дополнекиа произведения 1. В соответствии с условием 2, в старших разрядах с нулевого до (К-1)-й величина Е с-.одержит нули. Для их устранения ироизводдктся сдвиг регистра 3 влево на К разрядов и затем его содержимое передается в регистр 1, Для вычисления величины ;io С DO на вход блока 6 формирования части.чных произведений подаются делимое С из регистра 2 из блока 7, и величина. D. Их произна 2 циквел.енке также выполняется и результат образуется в регистт--, .с . аторои этап деления основан на с-.ле.цующих соотношениях. Пусть частное , умножив числитель и энам натель на D получим А: A-A.EA A,-tE(a,.,.(K-il R-1 I-V...), группа из К разрядов час где а . ного; -номер старшего разряда г -номер младшего разряда г Так как условия 1 и 2 выполнены то величины А и Ад совпадают с то ностью до 1 (К-.) разряда. Следова тельно, при проведении вычислений по формуле (3), в первом цикле в к честве множителя может быть исполь зована группа К старших разрядов ад 1. величины А . , После выполнения цикла умно5кени полученное частичное произведение oK--f прибавляется к величине АО , в результате чего в (К--1)-й разряд суммы может возникнуть 1 пе носа Р,, , что эквивалентно увелич нию множителя на 1 младшего разряд группы и должно быть учтено дополн тельным прибавлением величины Е т к ранее полученной сумме. В реэуль тате вьшолненных действий получим величину (ао.-.р.т суммарное приращение которой .m Е(ао, по отношению к величине А не превышает 1 (К-1)-го разряда. Подстави значение величины выражение (3 получим (a,,,..,., Величины д и 1 совпадают с точность до 1 {2к-1)-го разряда, поэтому в качестве второй группы разрядов мно жителя примем соответствующие разря ды величины А - а и выполним действия аналогичные oпиcaнны i, в результате чего получим величину ,(a,,vn А .зк-ч t . Чс(,4к.м- № Выполним аналогичные вычисления получим -(.п-tK-O А А л (« ПП К-l -(П1-2к-1) °п к,ц.2кч ...) так как величина,стоящая в скобках меньше 1 то -(n-VK-O ,А А : -1-т к г.е. ошибка вЕаГЧИсления частного пос ле - циклов не превышает 1(пгк-1) разряда. Например; пусть m 2, зтк К - 4, С 0.11011011,8 0,10001200, на 1-ом этапе деления определяем DO 1,1100 и выт-1исляем АО- 1.011111110100, Е 0.00001011, Второй этап деления начинаем с умножения Е на 4 старших разряда величины Ар,При этом К старших нулей величр ны Е учитываются начальным сдвигом Ар на К разрядов влево. 1011 1111 1010 АО 0111 1001 .Е X 1011 1100 0111 ООНРз 10000 ,1011 Е X РЯ 1100 0111 1110 Сдвиг А.у влево на К разрядов 11000111 1110 0000 0100 1101 11001000 ООН 1000 Сдвиг Ai влево на К разрядов 3. Е X ООН AJ (Р,. 0) Сдвиг А 2 А(Р,5 -0) Сдвиг Лд 1100 10000011 1000 0000 0010 0001 1100 100000 11 1.010 1100 100000111010 0001 0000 оно 1110 1100100.о оqi 1 К) 10 0111 1110 1100 1000 ООН 1010 0111 1110 0000 ак как дробь периодическое, то альше будут повторяться шаги 2,3,4, Прямое деление дает следующий реультат : D.1100 11011 i-iOCiCOOOOi-HC1C1000001ti 0.10001100 равнение результатов показывает, то ошибка после 4-х циклов вычислеий менее 1 19-го разряда. Предлагаемое устройство в процесе выполнения 2-го этапа деления ункционирует следующим образом. По игналу из блока управления 5 комутатор множителя 9 переключается на ыборку групп К младших разрядов реистра 2, а также открывается элеент И 8 для прохождения сигнала пееноса с выхода cyrvUviaTopa 4. Ввиду того, что величина Е была двинута влево на К разрядов, то в ачале 1-го цу-Лч-ла производится сдвиг егистров 2 и 3 таклсе на К разрядов лево, при этом содержимое старших К разрядов регистра 3 переписывается в младшие разряды регистра 2, откуда через коммутатор 9 поступает в блок формирования частичных произведений, одновременно на другой вход блока 6 поступает множимое из регистра 1. В блоке б сомножители перемножаются и частичное произведение подается на вход сумматора 4, где складывается с содержимым регистра 3. Перенос с выхода сумматора 4 поступает на регистр 2 и одновременно, через элемент И 8 - в блок управления 5 и в блок формирования частичны произведений б. Блок управления 5 за прещает передачу разрядов множителя через коммутатор 9 на вход блока б формирования частичных произведений через который в это время по сигналу от элемента И 8 множимое из регистра 1 подается на вход сумматора 4 для дополнительного сложения с содержимым регистра 3. Результат дополнител ного сложения с выхода сумматора 4 также записывается в регистр 3. Пос ле выполнения дополнительного сложе ния производится переход к выполнению второго цикла. Если при выполне нии суммирования содержимого регист ра 3 и частичного произведения, сиг нал переноса из сумматора 4 не поступает, то сигнал на вьссоде вертиля дополнительного сложения 8 отсутствует и переход к следующему циклу вычислений производится непосредственно после прибавления частичного произведения, без выполнения дополнительного сложения. Второй цикл вычислений также начинается со сдвига регистров 2 и 3 влево на К разрядов, в результате которого в младших разрядах регистр 2 оказываются К очередных разрядов множителя. И все вычисления выполня ются аналогично 1-му циклу. После выполнения -т- циклов в регистре 2 будут находиться N старших разрядов частного, в регистре 3 - число, которое совпадает с последующими разрядами частного с точностью (п+к-) го разряда. Предлагаемое устройство обеспечи вает выполнение умножения за - ци лов, каждый из которых включает в себя получение и накопление частичн го произведения. Для выполнения дел ния дополнительно требуется четыре аналогичных цикла при вычислении ве личин Е и А ,а также от О до -- ц лов сложения. Таким образом, в зави симости от длительности и количеств дополнительных циклов сложения, время деления 1 в 1,5-2 раза превышает время умножения. При этом аппаратура ускорения операции умножения в блоке частичных произведений полностью используется и при выполнении деления. Формула изобретения Устройство для умножения и деления нормализованных чисел, содержащее сумматор частичных произведений, первый регистр, второй регистр, блок вычисления обратной величины, блок управления, блок формирования частичных произведений и регистр накопления, выход которого соединен с входом первого регистра и первым входом второго регистра и сумматора частичных произведений, второй вход которого соединен с выходом блока формирования частичных произведений, первый выход сумматора частичных произведений соединен с входом регистра накопления, выход первого регистра соединен с входом блока вычисления обратной величины и первым входом блока формирования частичных произведений, второй вход которого соединен с выходом блока вычисления обратной величины, а третий вход блока формирования частичных произведений соединен с выходом второго регистра, второй выход сумматора частичных произведений соединен с BTOpbjM входом второго регистра, отличающееся тем, что, с целью упрощения устройства и увеличения быстродействия при выполнении деления, в него введены элемент И и когдмутатор множителя, первый вход которого соединен с выходом блока управления, а выход - с четвертым входом блока формирования частичных произведений, второй вход коммутато-ра множителя соединен с выходом втоторого регистра, первый вход элемента И соединен с вторым выходом сумматора частичных произведений, второй вход элемента И - с выходом блока управления, выход элемента И соединен с пятым входом блока формирования частичных произведений и входом блока управления. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3591787, кл. 235-159, 1971. . 2.Авторское свидетельство СССР № 305475, М.Кл G 06 F 7/39, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1971 |

|

SU313828A1 |

| Арифметическое устройство | 1978 |

|

SU763894A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ | 1973 |

|

SU385273A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения | 1988 |

|

SU1615706A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| Множительное устройство | 1978 |

|

SU752335A1 |

Авторы

Даты

1979-02-25—Публикация

1976-04-19—Подача