1

ИзобретеЕие отнОСИтСЯ к цИф,роБой вычислительной технике, в частности .к электронным клавишиьш вычислительнЫМ м.ашинам.

Известные устройства для умножения и деления чисел с -естественной запятой содер,жат схемы для сдвига множимого на один разряд BmpaiBo перед ,ал0:М «собственно умножения, л-ля сдвига миожимого м произведения на один разряд влево после выполнения «coi6cTBeHiHo умножения, для сдвига делимого и делителя на один разряд вправо перед началом «собственно деления и для сдвига частного и делителя на один разряд влево после вы1пол1не1Н1ия «зсабюпвенно делени-я.

Недостатком известных устройств «вляется (ИХ сложность.

Целью .из.обретен ия явл1яется сокращение оборудования.

Указанная цель достигается за счет того-, что выходы cxeiMbi С1пр1еделения положен ия запятой соединены со входом схед1ы под готовки ум:ножеииЯ, выход кюторой, соединен со входом схемы сдвига влраво. Выход схемы подготовз(и деления через схему вычитания соеди1нен со входом схемы сдвига влево, выходы схем сдвига влево и вправо соединены с соответствующими входами блока нормализации.

Схема определения толожения запятой содержит триггер, вход установки «1 которого

соединен с щинои «деление, вход установки «О - с шиной «умножение, 1счетный вход тригге,ра через схему «ИЛИ соединен с выходом первого бло.ка запятых и .выходом счетчика управления, выход триггера через И соединен со входом второго блока запятой.

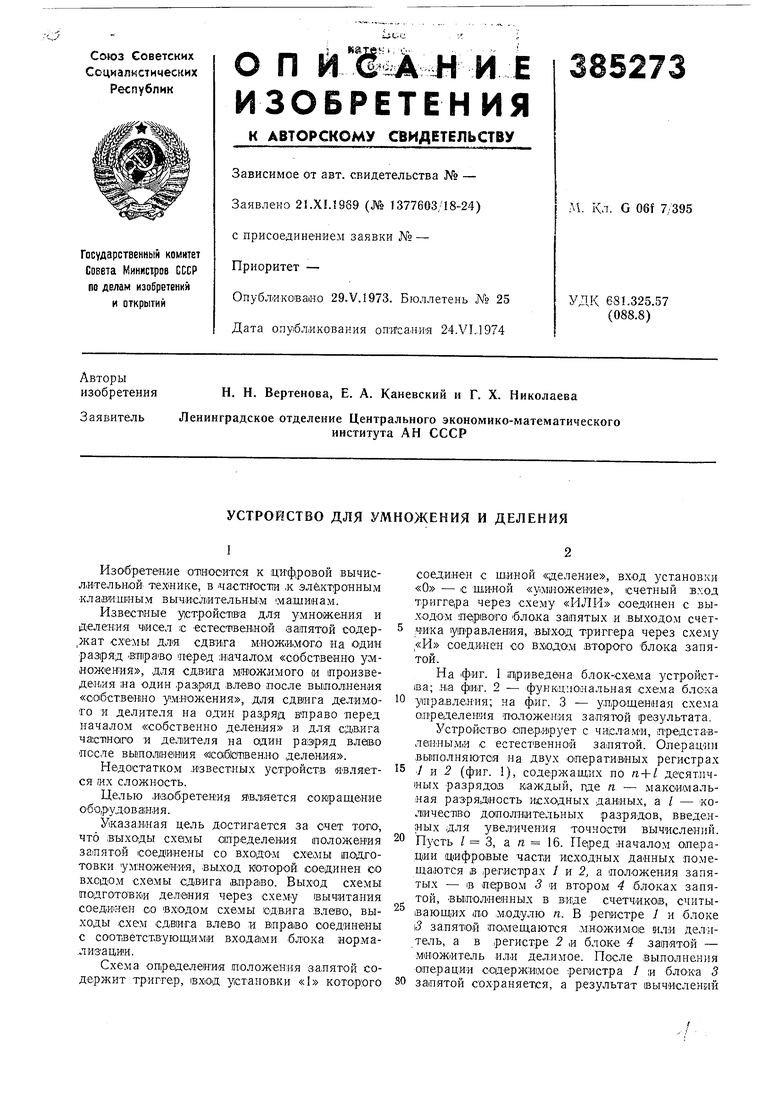

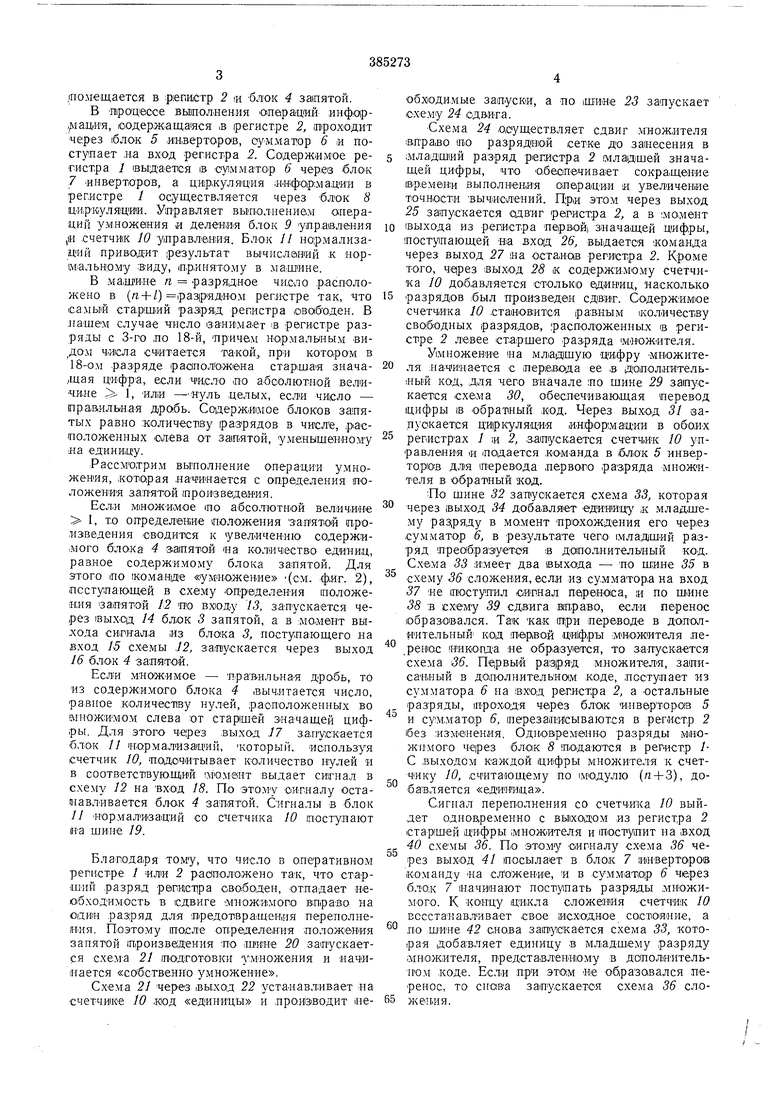

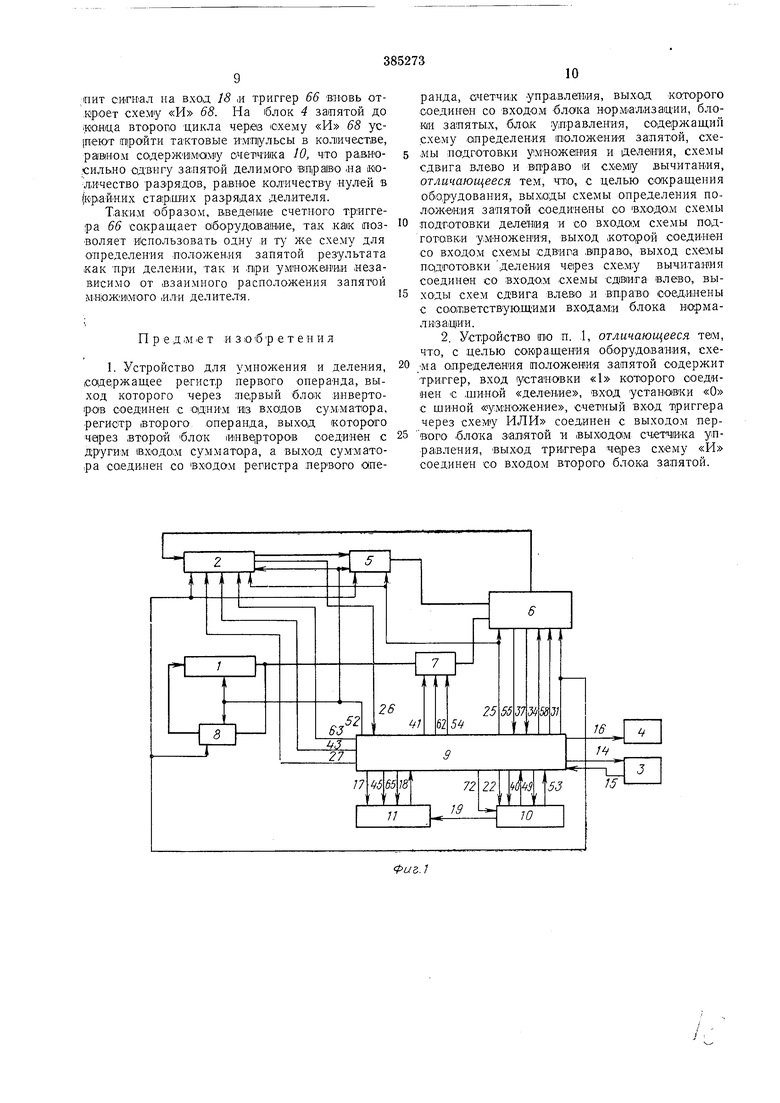

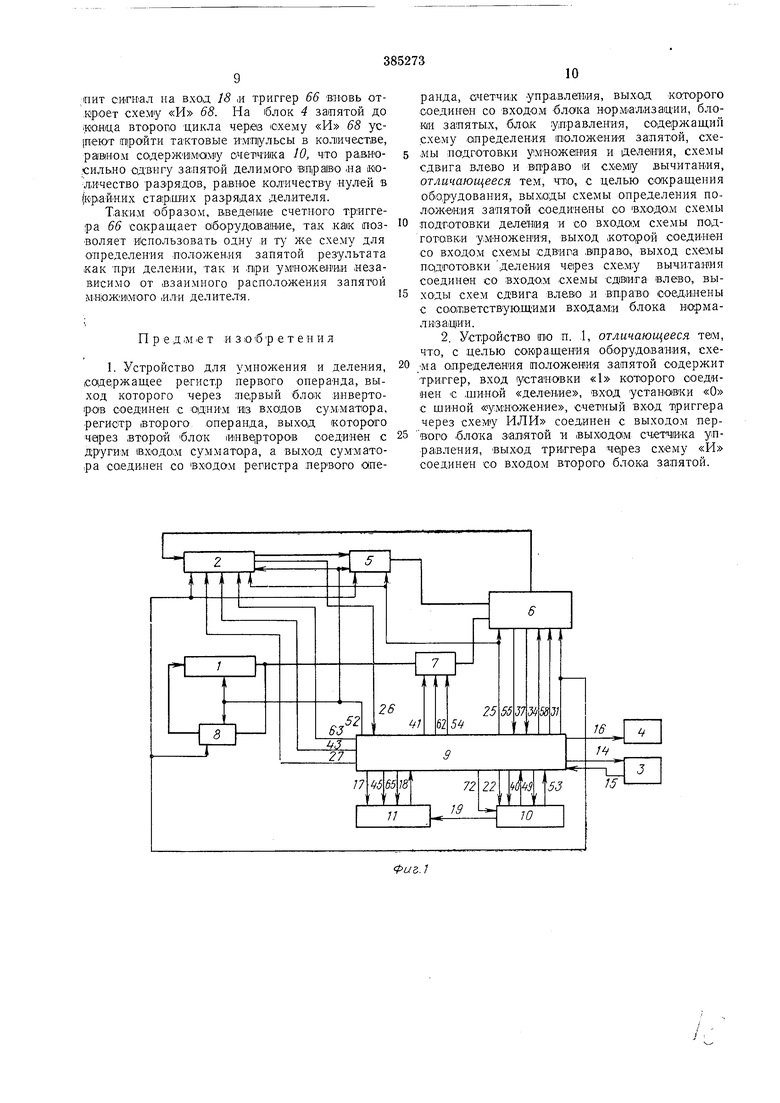

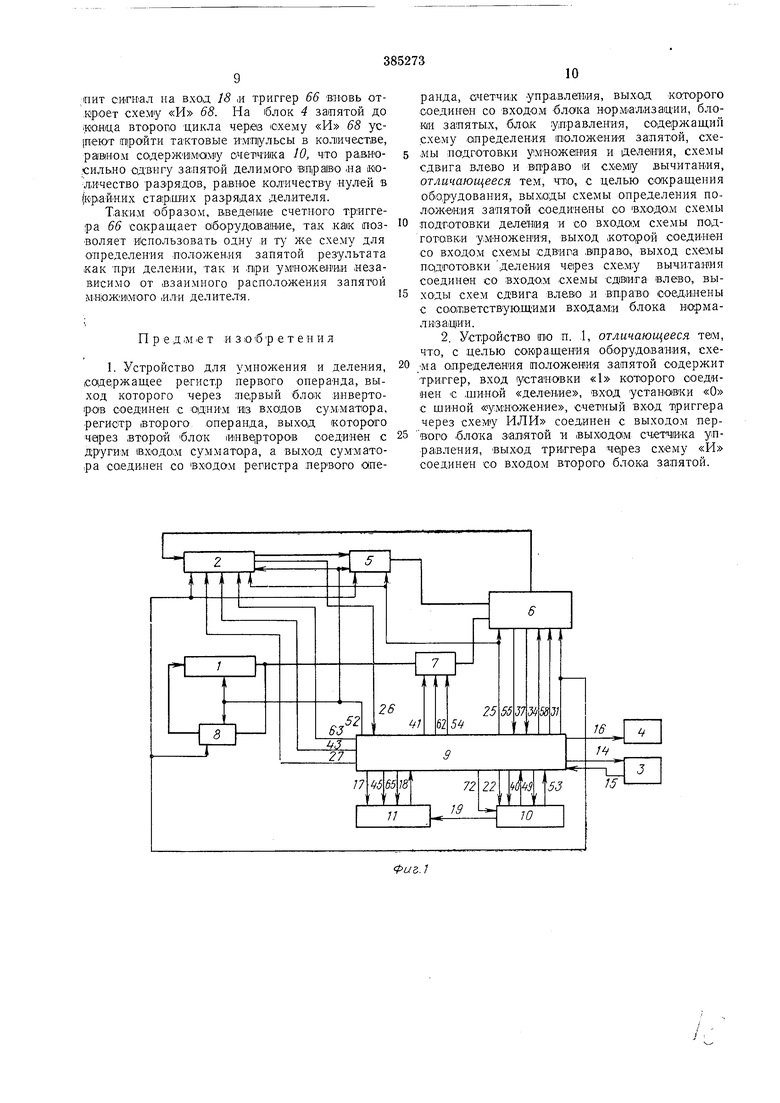

На фиг. 1 приведена блок-схема устройства; н,а ф|иг. 2 - функд:ю;нальная схема блока

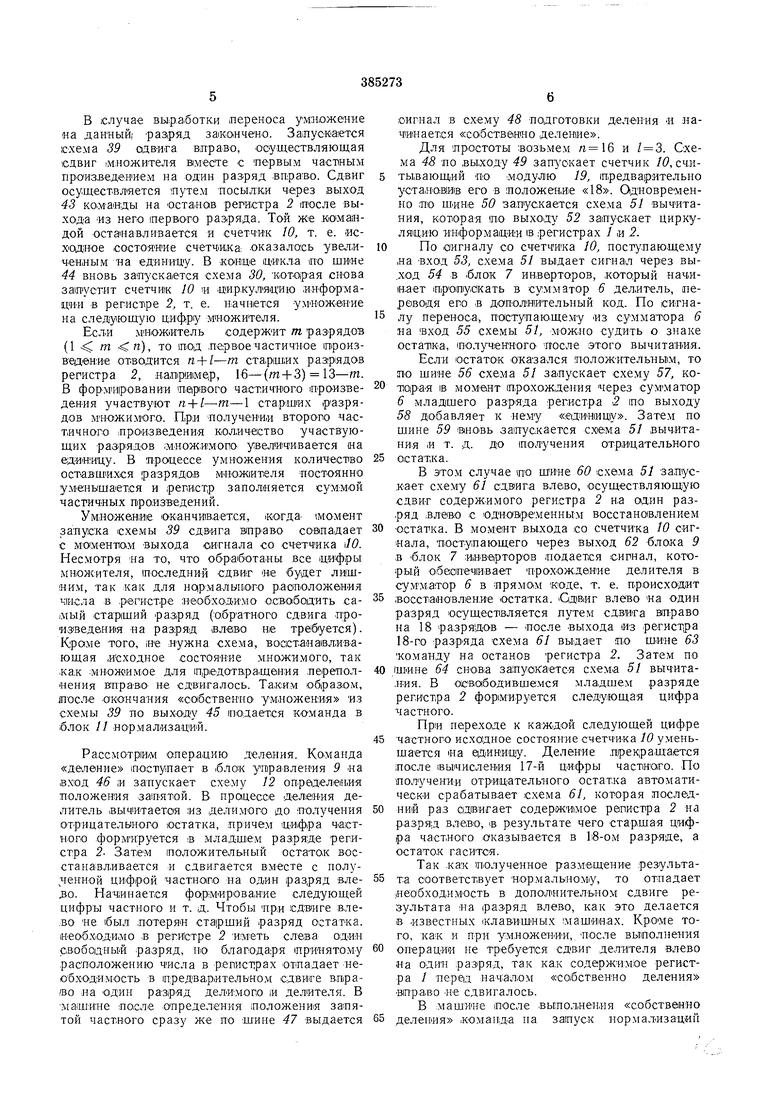

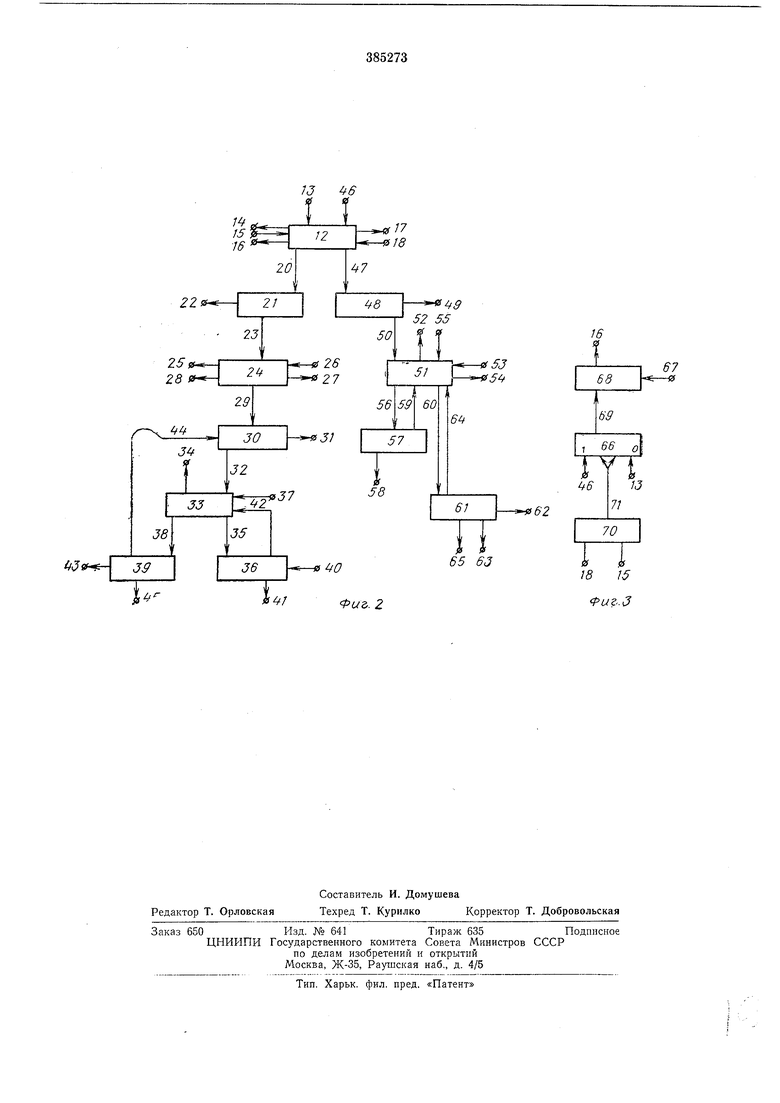

управления; на ф|Иг. 3 - упрощенная схема олределешия положения результата.

Устройство .оперирует с чиелами, представлеенымй с естественной запятой. Операдии выполняются на двух оперативных регистрах J и 2 (фиг. ), содержащих по п + 1 десятичных разрядов каждый, где п - максимальная разрядность исходных данных, а / - коЛ1ичест1во дополнительных разрядов, введенных для увеличения точности вычислений. Пусть / 3, а п 16. Пе1ред началом операции цифровые части исходных данных помещаются в регистрах У и 2, а положения запятых - IB .м 3 и втором 4 .блоках запятой, выполненных в виде счетчиков, считывающих по .модулю п. В регистре 1 и блоке 3 запятой помещаются .множимое иля делителъ, а в регистре 2 и бло.ке 4 занятой - множитель или делимое. После выполнения операции ссяержи1мое регистра / и бло;ка 3

запятой сохраняется, а результат вычислений

.(Помещается в релистр 2 и блок 4 запятой.

В Працеосе выполнения OneipauMfi инф С11р.мация, содерж-агдляся (В iperHicrpe 2, (проходит через (блок 5 .инверторав, сумматор 6 и поступает .на вход регистра 2. Содержимое регистра 1 выдается в сумматор 6 черкез блОК 7 инверторов, а цир.куля1ция ;и«фор:мацИи в регистре / осуществляется через -блок 8 цирк уляции. Управляет вьтола1ением операций умножения и деления блок 9 улр.авления ,1И счетчик 10 управлбвия. Блок // нормализации приводит результат вычиславий к нор1М1альному :в:иду, прлнятому в ма;шине.

В машиие л разрядное число раслоложено в (rt-f/) раз|рядном регистре так, что самый старший раз1ряд регистра овабоден. В :на;шем случае число ваиимает в регистре разряды с 3-го ло 18-й, пр:ичем нормальным видом ч.исла считается такой, при котором в 18-ом разряде растолОжена старшая знача,,щая цИфра, если Числ10 по а-боолютной величине J 1, ИЛИ -нуль целых, если число - правильная дробь. Содержи1мое блоков запятых равно количеству разрядов в числе, piacттоложенных слева от запятой, уменьщенному «а едини.цу.

Рассмотрим выполнение операции умножения, котарая .начинается с определения положения запятой (произведения.

ЕСЛ.И М1ножи;мое ino абсолютной велячиве 1, то определевие положения аалятой проИ31ведения сводится к увеличению содержиiMoro блока 4 запятой ща количество единиц, равное содержимому блока запятой. Для этого по команде «умножение (см. ф,иг. 2), псступающей в схему Определения положения запятой 12 ио входу 13, зап-ускается через IBыход 14 блок 3 запятой, а в момент вылода сигнал.а из блока 3, поступающего на вход 15 схе.мы .12, запускается через выход 16 блок 4 запятой.

Если множимое - прав.нльная дробь, то из содержимого блока 4 .вычитается число, равное количеству нулей, р.аоположенных во множимом слева от старшей значащей цифрь. Для этого через выход 17 3:апу;сКается блок // нормализации, который, используя счетчик 10, подсчитывает количество нулей и в соответствующий 1момант выдает сигнал в схему 12 на вход 18. По этому сигналу остаиавливается блок 4 запятой. Сигналы в блок // -нормализации со счетчика 10 поступают иа шине 19.

Благодаря тому, что число в оперативном регистре / или 2 раШОложено так, что старший разря.д perHCTlpa свободен, отпадает необходимость в сдвиге множимого вправо на один разряд для предотвращения перенолнен.ия. Поэтому после определения полож1ения занятой произведения по |ШИ1не 20 запускается схема 21 подготовки лмножения и начинается «собственно умножение.

С.хема 21 через вы.ход 22 устанавливает на счетчи1ке 10 ,кюд «единицы и прО:И31Водит ееобходи..мые запуски, а по |ши«1е 23 запускает схему 24 сдвига.

Схема 24 осуществляет сдвиг множителя вправо 1ПО разрядной сетке до занесения в

младший разряд регистра 2 младшей значащей цифры, что обеспечивает сокращение времени выполнения операции и увеличение точН|Ости выч нслений. При этом через выход 25 запускается -сдвиг регистра 2, а в 1момент

0 выхода из регистра перв-ой) значащей цифры, поступающей иа вход 26, выдается команда через выход 27 :на останов регистра 2. Кроме того, ч-е|рез выход 28 к содержимому счетчика 10 доб,авля1ется столько единиц, насколько

разрядов ;был праизведен сдвиг. Содержимое счетчика 10 становится равным 1количеству свободных разрядов, :расположенны,х щ регистре 2 левее старшего разряда множителя. У|множение на мл1адшую цифру -мвожителя ;нач1Инается с 1пер1евода ее в дюполнитель:ный код, для чего вначале по шине 29 запускается схема 30, обесп-ечивающая перевод цифры 1В обратный код. Через выход 31 аап -скается циркуляция информации в обои-х

репистрах 1 и 2, з.апускается счетчи к 10 управления 1И подается ком-анда в ,блок 5 инверторов для (перевода первого разряда множителя в обратный код.

По шине 32 запускается схема 33, которая

0 через выход 34 добавляет единицу к младшему разряду в момент прохождения его через сум.матор 6, в результате чего младший разряд преобразуется в дополнительный код. Схема 33 имеет два выхода - по шине 35 в

схему 35 сложения, если из сумматорл на вход

37не тоступил сигнал переноса, я по шине

38В схему 39 сдвига вправо, если перенос (Образовался. Так как три переводе в донолнительныЙ код (первой цифры множителя пер-ен10,с викопДа не образуется, то запускается схема 36. Первый разряд множителя, записан ный в дополни те л ьно(м .коде, поступает из сумматора 6 на вход регистра 2, а остальные разряды, проходя через блок и.нверторО(в 5 и сум.матор 6, перезаписываются в регистр 2 без изме;нения. ОдНОвременно р.азряды множимого через блок 8 подаются в регистр 1С выходом каждой цифры множителя к счетчику 10, считающему по (модулю (я + 3), добавляется «единица.

Сигнал переполнения со счетчика W вый.дет одновременно с вьиходом из регистра 2 старшей цифры ;множителя и (поступит на вход 40 схемы 36. По этому сигналу схема 36 через выход 41 посылает в блок 7 инверторов команду на сл ожение, и в сумм1ат.о|р 6 через бло.к 7 нaчннaют поступать разряды множимого. К Концу (цИКла слОжения счетчи1К 10 восстанавливает Свое исходное состояние, а

по ШИне 42 снова запускается схема 33, которая добавляет единицу в мла.дшему разряду мНОЖ-ителя, представленному в дсполнительиом .коде. при этом не Образовался перенос, то снова запускается схема 36 сло5 жеп,ия.

В случае вы;р,аботки переноса умножение на данный разряд заканчено. Запускается схема 39 одвига вправо, осуществляющая сдвиг 1М;НОжителя вмвсте с первым часиным произведением на один разряд вправо. Сдвиг осуЩествл яется шутем посылки через выход

43ко.Мавды на ocTainoB регистра 2 пюсле выхода ИЗ него 1первого раз.ряда. Той ж« кюмаидой останавливается и счетчяк 10, т. е. исходное состояНие счетч.ика оказалось увеличенным на единицу. В конце адиклл по шине

44вновь запускается схема 30, кото|рая снова за1П|устит счетчик 0 м дмркуляадию ;и«формацИИ в регистре 2, т. е. Н:ачн1ется улгножение на следующую цифру миожителя.

ЕсЛИ м ножитель содерЖит т разрядов (1 ; m tt), то 1ПОД первое частичное ороизведен:ие отвадится п + -т старших раз1р1ядов регистра 2, даприм р, 16-(т + 3) 13-т. В фор м1и|ровани:и inapiBoro частичного произведения участвуют п + старших разрядов мНОжимого. При получении второго частичного произведения количество участвующих разрядов ;МНОЖи мого увеличивается иа . В процессе умножения количество оставшихся разрядов множителя постоянно уменищается и регистр заполняется €ум:мой частичных произведений.

Ум:Ножвн;ие оканчи1в,ается, «огда момент запуска схемы 39 сдвига втр-аво совпадает с моментом выхода сигнала со счетчика ilO. Несмотря на то, что обработаны все цифры множителя, 1последнИй сдвиг «е будет лишним, так как для ндрмалвн.ого рлоположения числа в piepHCTpe нео-бходимо освободить са1мый старший разряд (обратного сдвига произведбнвя на разряд вле&о не требуется). Кроме того, не нужна схема, восстанавливающая исходное состояние множимого, так как :множ ИМ|Ое для предотвращения переполнения в:пра-вО не сдвигалось. Таким образом, окончания «собственно умгножения из схемы 39 по выходу 45 подается команда в блок // нормализации.

Рассмотрим операцию деления. Команда «деление поступает в (блок управления 9 «а в.ход 46 и запускает схему 12 определения положения запятой. В працесае деления делитель вычитается из делимого до получения отрицателыного остатка, причем цифра частного формируется в младшем разряде регистра 2- З.атем положительный остаток восстанавливается и сдвигается вместе с полученной цифрой частного на один разряд вледо. Начинается формирование следующей цифры частного и т. д. Чтобы при сдвиге влево не был потерян старший разряд остатка. необХОдидю в реги1стре 2 иметь слева один свободный разряд, по благодаря 1принятому расположению числа в репист рах Отпадает необходимость в предварительном -сдвиге anipa во на один разряд делимого и делителя. В ма1шине после определения по.южения запятой частного сразу же по шине 47 выдается

сигнал в схему 48 подготовки делеНия и нач инается «собственно деление.

Для простоты возьмем и . Схема 4S по выходу 49 запускает счетчик /С, считывающий по 1модул ю 19, 1предва1ритель ю уста,нови1в его в положение «18. Одновременно то Щине 50 запускается схема 51 вьгаитания, которая по выходу 52 запускает Циркуляцию информации IB регистрах / и 2. По сигналу со счетчика 10, поступающему на вход 53, с.хема 51 выдает сигнал через вы.ход 54 в .блок 7 инверторов, который начи1Н.ает пропускать в сумматор 6 делитель, переводя его в дополнительный код. По си;гналу переноса., поступающему из сумматора 6

на ВХОД 55 схемы 51, можно судить о знаке

остатка, полученного этосле этого вычитания.

Если остаток оказался положительным, то

по шине 56 схема 51 запускает схему 57, которая IB момент прохождения через сум .матор 6 младщего разряда регистра 3 по выходу 58 добавляет к нему «единицу. Затем по щине 59 вновь запускается с.хема 51 вычитания и т. д. до получения отрицательного

остатка.

В этом случае по шине 60 схема 51 запускает схему 61 сдвига влево, осуществляющую сдвиг содержимого регистра 2 на один разряд влево с одновре.менным восстановлением

О;статка. В момент выхода со счетчика Ю сигнала, поступающего через выход 62 блока 9 в блок 7 инвврторов .подается сигнал, КОТОрый обеспечИВает Прохождение делителя в су.мм.атор 6 в прямом коде, т. е. происходит

восстановление остатка. .Сдвиг влево «а Один разряд осуществляется путем сдвига вправо на 18 разрядов - .после выхода из регистра 18-го разряда схема 61 выдает по ш.ине 63 команду на останов регистра 2. Затем по

1шине 64 снова за:пуак:аеТСЯ схема 5} вычиталия. В ОСвабодившемся младшем разряде регистра 2 формируется следующая цифра частнОго.

При переходе к каж.дой следующей цифре

частного исходное состояние счетчика 10 уменьщается «а единицу. Деление прек;ращается после вычисления 17-й цифры частного. По получении отрицательного остатка автоматически срабатывает схема 61, которая последНИИ раз адЕигает содержи1мое репистра 2 на р-азряд влево, в результате чего Старшая цифра частного оказывается в li8-OM разряде, а остаток гасится.

Так как полученное размещение результата соответствует нормальному, то отпадает необходимОсть в допОЛннтелЬНОм сдвиге результата на раз.ряд влево, как это делается в .известных клавишных маши1Н.ах. Кроме того, как и при умножении,, носле выполнения

онерации не тр-ебуется сдвиг делителя Влево на ОДин разряд, так ка,к содержимое регистра / перед нач:алом «собственно деления ВПраво Не сдвигалось.

В :машИ1не после выполнения «собственно

деления коман:да па запуск нормал.изаций

выдается mo выходу 65 непасредственно со схемы 61.

Рассмотрим (более подросло про-цесс определения положения запятой частного и ;п,ро.изведения. Код, .хранящийся в блоке з апятой, равен .количеству разрядов, расположевных слева от запятой, уманыш0н Н|01му н,а единицу. ,. для числа 824,512 содержимое блока запятой p asHio- двум, а для чи-оел 8,824 и 0,000017 - нулю.

Определение положения заиятой результата сводится к увеличению или уменьше нию содержи.мого блока 4 запятой в зависимости ,от кода операции и от поЛОжения зашятой множимого или делителя. Так, при умноже,йии могут и:меть место два случая:

1)М1ножи мое - целое ч.исло или смешанная дробь,

2)множимое - травильная дробь.

В перво м случ-ае к содержимом у второго блока 4 за1пятой до|бавляется садфжнмое |пе;р|Вого -блока 3 запятой. Во вторО1М случае из содержимого блока 4 запятой вычитается числю, раювое количеству нулей, р.асположеняых тао множи1 1О1м слева от старшей значащей ц:И|фры.

При определении запятой частного могу иметь месфо два случая:

1)делитель -: целое чи1ало или смешанная. Д|рО|бъ, тогда из содержимого бло.ка 4 выч:итается содержимое бл-ока 3;

2)делитель - 11равиль.н.ая дробь, тогда к содержимому блока 4 добавляется число, равное количест1ву «улей -в делителе, раоположеняых левее стар.шей значащей цифры.

iFIycTb содержи..мое 3 запятой равно А, а содержи1мое блока 4 запятой - В.

К|0м:анда «умн ожение, поступаю.щая в схему 12 1ПО входу 13, устанавливает счетный триггер 66 iB состояние «нуля (фиг. 3). Одновре.менно через вход 67 на схему «И 68 начинают п.ост у1пать та.ктовые импульсы, которые -не П1роходят через эту схему, так как она ПО ш;и1не 69 связана с вдин:ичнъ1м выходом триггера 66. Ком.андой «умножение через выход 14 запускается также и блок 3 запя.той, т. е. «а его вход тоже подаются тактовые импульсы.

Всего за цикл работы машины иа вхо.д 67 и в блок 3 запятой ооступит ио п тактов. Так как счетчики запятых считают ino .модулю п, то сигнал с блока 3 выйдет после то.го, к:а.к на его вход п.оступят я-А импульсов. Оигнал с выхода блока 3, поступающий «а схему 12 ио входу 15, через логическую схему 70 «ИЛИ глодается по 1ШВне 71 на счетный в,ход триггера 66 и перебрасывает его в состояние еди|НИ|цы. С ЭТ01ГО момента через cxeiMy «И 68 )И выход 16 «.а вход бл-ока 4 запятой начинают поступать тактовые импульсы. К концу цикла содержимое блока 4 увеличится на Л €ДИ1Ниц, т. е. станет равным А+В.

Если Множимое оказалось правильной дробью (/4 0), то сигнал с выхода блока 3 поступит на счетный вход тр и;ггера 66 только

после прохождения последенго (я-то) тактового 1им.пульса, т. е. схема «И 68 не уовеет на первом цикле пропустить в блок 4 ви одного тактового импульса. С-одержимое бло.ка 4 в этом случае после первого цикла останется без изменений.

Счетчик 10 во время .первого цикла водсчитывает количество нулей, расположенных левее старшей значащей цифры в числе, находящемся в р1егистре / (мН|ОЖ:имое или де0литель). Во втором цикле тактовые импульсы из (блока упр.авлениЯ 9 (подаются по шине 72 №а вход счетчика 10, а через вход 67 - на схему «И 68.

Триггер 66 после пфвюго цикла остается в единичиом состоянии, поэтому на вход блока 4 через 1вых10д 16 схемы 12 продолжают поступать тактовые Импульсы. Закрывается схе.ма «И 68 .по сигналу со счетчика W, так как на счетный вход триггера 66 в момент выхода сигнала со счетчика 10 через в.ход 18 поступает сигнал .из блока 11 нормализации. Счетчик 10 в ЭТО..М режиме считает по мо.дулю, поэто му до имомента выхода сигнал.а со

5 счетчика к с-одержимому блока 4 добавятся единицы в колич1еств1е, равном .дополнению содержи.мопо счетчика 10 до п. Действие вычитания, таким образом, заменяется действием сложения.

0

Если .мложи.мое ino .а(бсолютной величине }, то после первого цикла содержимое счетчика 10 .останется равным нулю. Во втором ци.кл1е сигн.ал со счетчика 10 выйдет в тот ;мо.мент, (когда через с.хему.«И 68 пройдут все

5 тактовые импульсы, т. е. содержимое блока 4 снова примет-значение Л-f В.

При о(пределен:ии положен.ия запятой частного автоматически срабаты,вают те же цепи и в ТОЙ же последовательности. О.тличме со0стоит в том, .что команда «деление, поступающая в схему 12.nio входу 46, устанавливает три;ггер 66 не в нулевое оо;стоя.ние, а в еди(ничное. Так же, как и при умножении, в пер(®OM цикле на вход блока 5 запятой и на (вход

5

67схемы «И 68 подается по я такто1вых импульсов, га на счетчике 10 по(Д1Считыв.ается количество нулей, расположенных в делителе левее старшей значащей цифры. Схема «И

68в первом цикле будет открыта с начала

0 Ц(Икла и .до момента выхода сигнала из блока 3, .п.осту1п.ающего, как .и при умножении, .на вход /5. На вход блока 4 запятой через выход 16 за это в(ремя (поступит я-А тактовых импульсов, что ра(вношльно вычитанию из

5 содержН;МОГО| блока 4 соде,ржимого блока 3.

Если дел.итель - правильная дробь (Л 0), то на вход блока 4 поступят все я импульсов, т. е. блок 4 к концу первого цикла восстановит свое исходное со(стояние В. Одн-ако в сл(у0чае на счетчике 10 к началу второго цикла будет Получено число, равное 1 оличеству нулей в крайних старших разрядах делителя. Во втором цикле на «xoiii счетчика 10, как и при умножении, (ПО шияе 72 поступят я тактов, а

5 ,в момент выхода сигнала со счетчика 10 «поступит сигиал на вход 18 л триггер 66 вновь от.кр-оет схему «И 68. На блок 4 заоятой до «оица второго цикла черев с-хему «И 68 усртеют оройти тактовые импульсы в кол1ичестве, рав|ном С01держимам1у счетчика 10, что равио«ильно одвигу запятой делимого вцраво .на йодИЧество разрядов, равное количеству Нулей в (к райних старших раЗ(рядах делителя.

Та.ки.м образом, в,веде11,И1е счети.ого тр:иггера 66 сокращает оборудование, так как позволяет иtпoльзoвaть одну ,и т;, же схему для определения положения запятой результата как п.ри делении, так и три умножении независимо от взаимного расположения запятой мйОЖИ1МО.го или делителя.

Пред iM е т из о б р е т е и и я

1. Устройство для умножения и деления, содержащее регистр первого операида, выход которого через первый блок инверторов соединен с одним из входов сум матора, регистр второго операнда, выход которого че|рез второй блок 1И1Нве(рторов соединен с другим 1в,ходо:м сумматора, а выход сумматора со1еди,нен со входом регистра первого операнда, счетчик упр-авлеиия, выход которого соединен со входом блока норм ализаадии, блоК(и запятых, блок управления, содержащий схему определения иоложенИЯ запятой, схе-МЫ подготовки умножееия и деления, схемы сдвига влево и вправо я схему вычитания, отличающееся тем, что, с целью сожращения оборудования, выходы схемы определения поЛОжония запятой соединены со в,ходо.м схемы

подготовки деления и со входо1М схемы подготовки умножения, выход кото,рой соединен со входом схемы сдвига .вправо., выход схемы п.С|Д ротовки деления через схему выч.итаиия соединен со входом схемы сдвига влево, выходы схем сдвига влево .и вправо соединены с соО)Хветствую.щими входами блока Н1армализации.

2. Устройство по п. 1, отличающееся тем, что, с целью сокра.щения оборудования, схе,ма определения полож&вия запятой содержит триггер, вход установки «1 которого соединен с .шиной «деление, вход установки «О с шиной «умножение, счетный вход триггера через схему ИЛИ соединен с выходом первого блока 31аиятой и выходам счетчика управления, выход триггера схему «И соединен со входо:М второго блок.а запятой.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для умножения и деления | 1975 |

|

SU600555A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

Фиг,. 2

16

67 65 63

Авторы

Даты

1973-01-01—Публикация