(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1982 |

|

SU1043741A1 |

| Запоминающее устройство с коррекцией дефектных элементов памяти | 1981 |

|

SU980165A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Постоянное запоминающее устройство | 1975 |

|

SU733025A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство с коррекцией информации | 1981 |

|

SU957273A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

| Запоминающее устройство | 1975 |

|

SU714496A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

Изобретение относится к вычислительной технике и может быть использовано в электронной промышленности при изготовлении больших интегральных схем запоминающих устройств.

Известны полупроводниковые интегральные запоминающие устройства с произвольной выборкой с разрядной организацией, которые содержат матрицу элементов памяти и схемы логики обрамления, позволяющие производить обращение при записи и считывании информации только к одному любому элементу памяти матрицы 1.

Это устройство имеет низкую надежность.

Наиболее близким к изобретению техническим решением является запоминающее устройство, содержащее дешифратор адреса слова, соединенный с адресными шинами матрицы элементов памяти, разрядные шины которой соединены с выходами первых вентилей и информационными входами блока считывания, управляющие входы которого подключены к выходам дешифратора адреса разряда и к первым входам первых вентилей, вторые входы которых соединены с шиной записи, а третьи входы - с шиной управления

первым входом выходного блока и входами обоих дешифраторов и шину разрешения записи 2. Однако такое устройство будет приводить к ошибкам хранения информации при наличии дефектных элементов памяти, которые возникают из-за дефектов изготовления в процессе производства. Поэтому при производстве такие запоминающие устройства отбраковываются.

Целью изобретения является повышение надежности запоминающего устройства.

Достигается это тем, что оно содержит дополнительные элементы памяти в каждом слове, блок коррекции ошибки, вторые вентили, два элемента И, инвертор, элемент ИЛИ и в каждом разряде последовательно соединенных два элемента 2И, входы первых элементов 2И подключены к разрядным шинам матрицы элементов памяти, выход первого элемента 2И соединен с

первым входом блока коррекции оши&ки, второй вход второго элемента 2И соединен с первым входом соответствующего первого вентиля и с вторым входом блока коррекции ошибки, выход

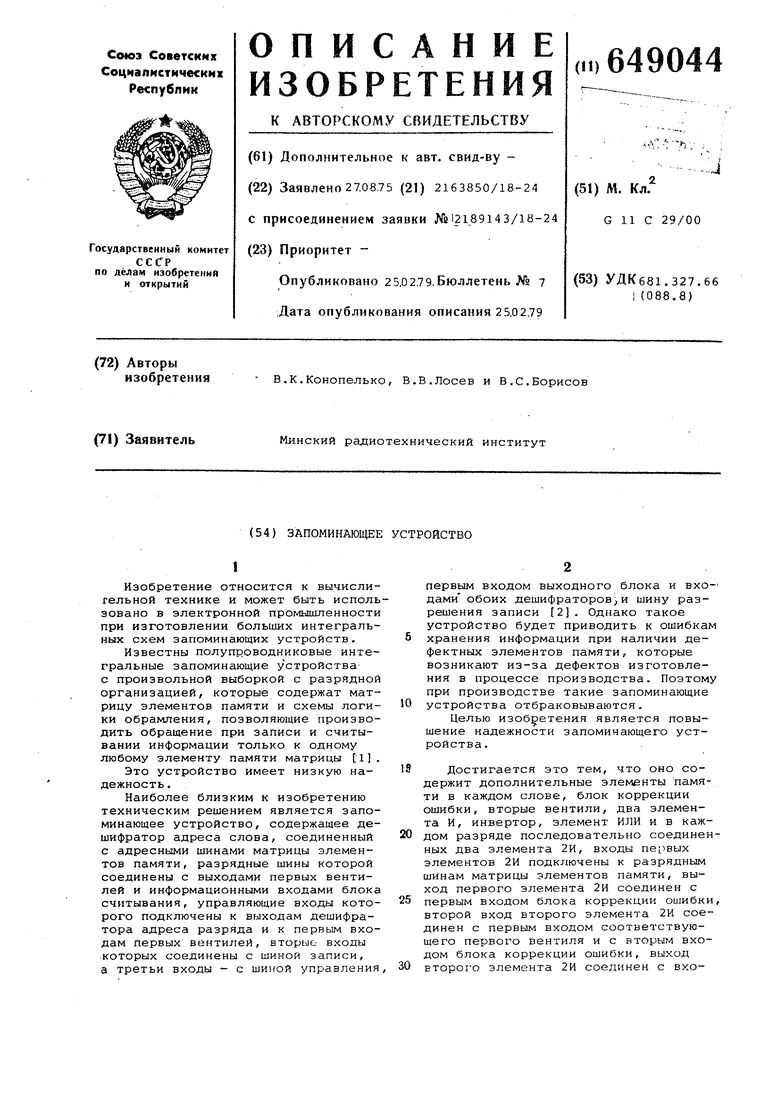

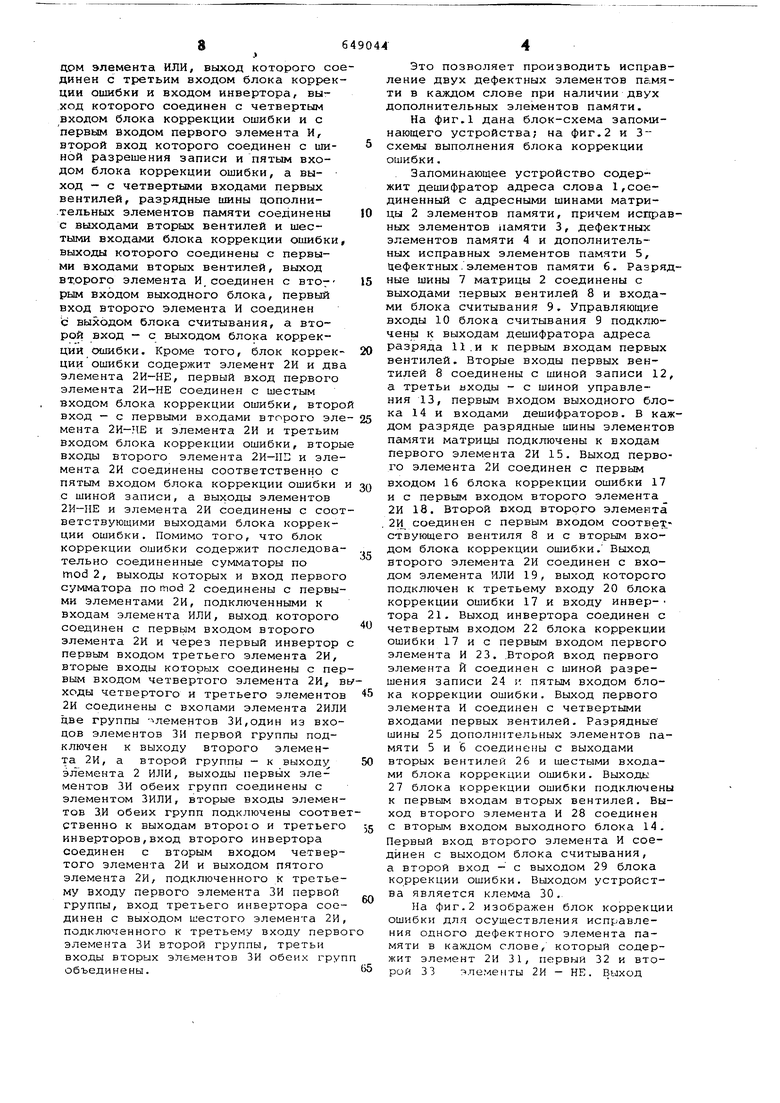

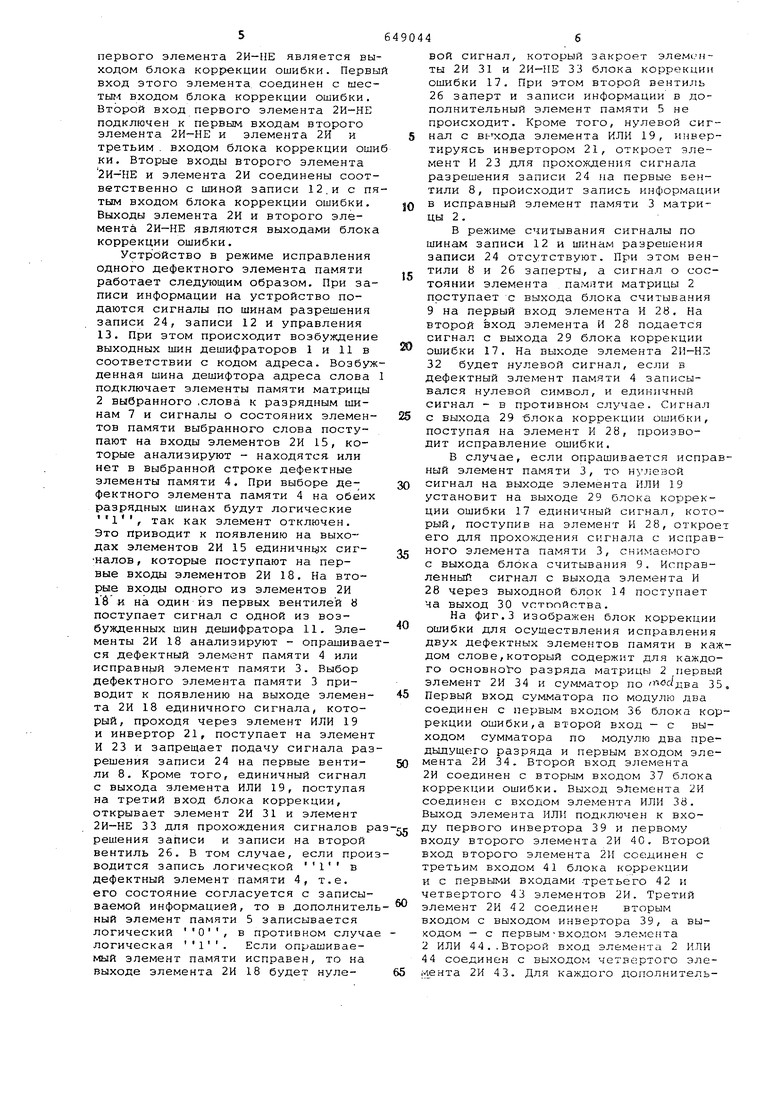

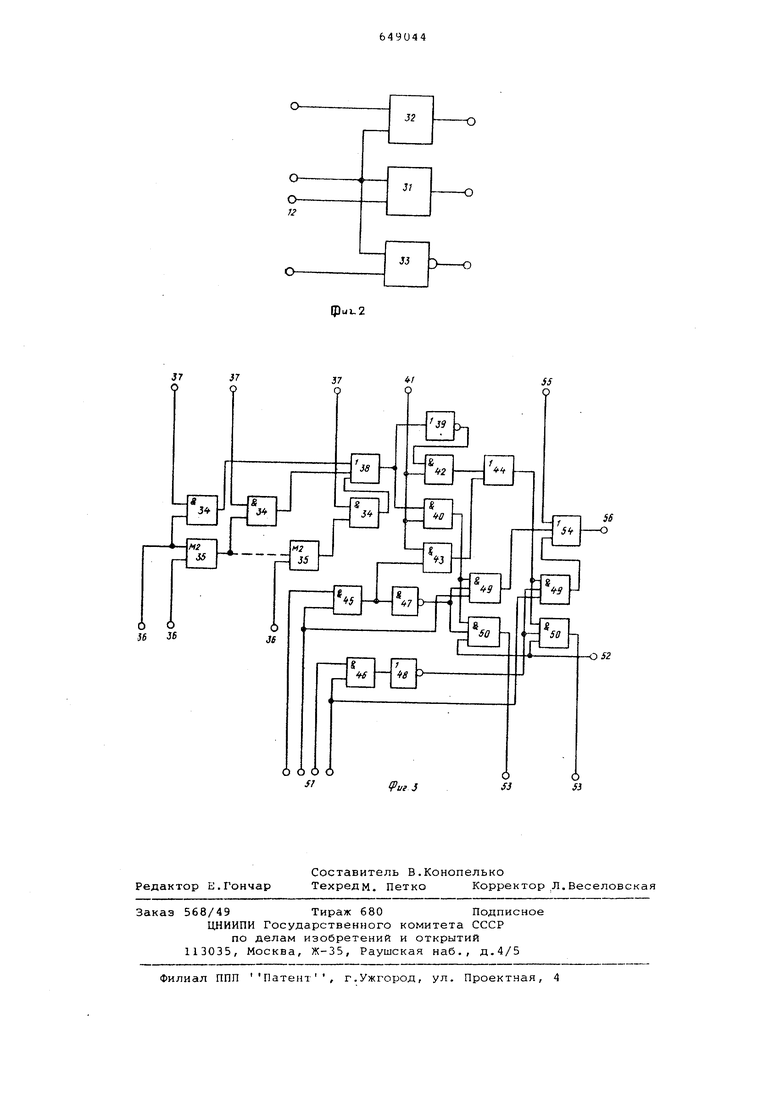

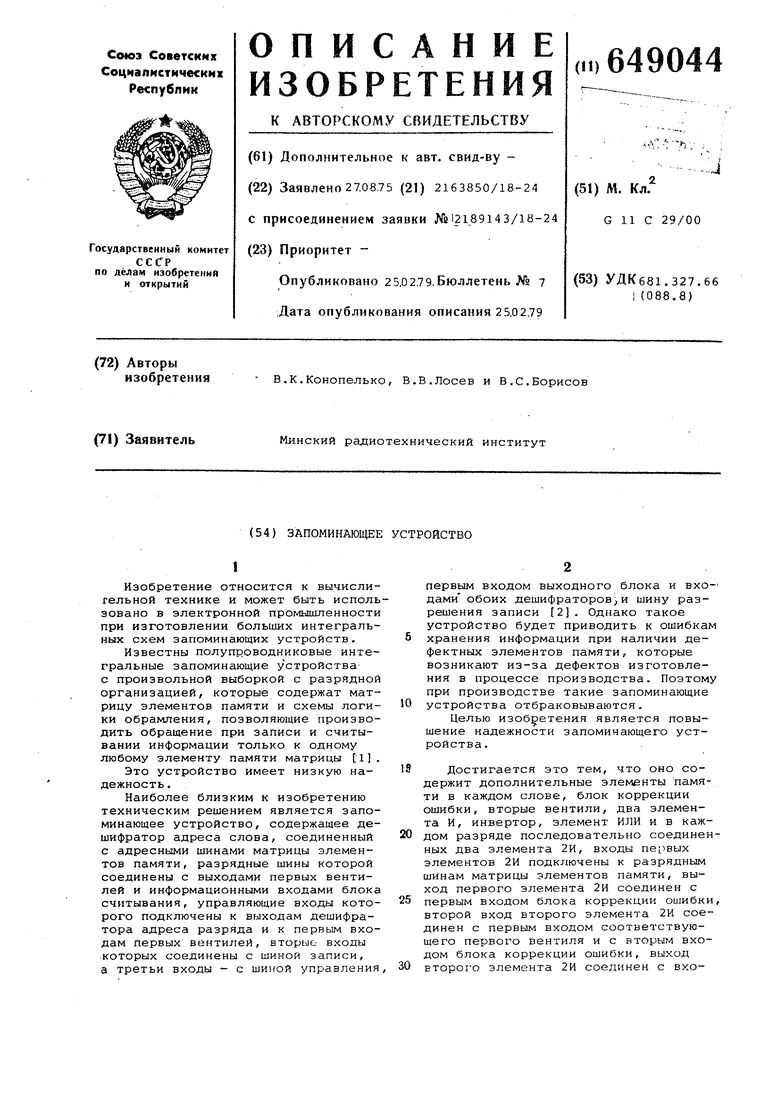

второго элемента 2И соединен с вхоцом элемента ИЛИ, выход которого сое динен с третьим входом блока коррекции ошибки и входом инвертора, выход которого соединен с четвертым входом блока коррекции ошибки и с первым Входом первого элемента И, второй вход которого соединен с шиной разрешения записи и пятым входом блока коррекции ошибки, а выход - с четвертыми входами первых вентилей, разрядные шины цополни.тельных элементов памяти соединены с выходами вторых вентилей и шестыми входами блока коррекции ошибки выходы которого соединены с первыми входами вторых вентилей, выход второго элемента И.соединен с втог рым входом выходного блока, первый вход второго элемента И соединен с выходом блока считывания, а второй вход - с выходом блока коррекции ошибки. Кроме того, блок коррекции ошибки содержит элемент 2И и два элемента 2И-НЕ, первый вход первого элемента 2И-НЕ соединен с шестым входом блока коррекции ошибки, второ вход - с первыми входами второго эле мента 2И-7IE и элемента 2И и третьим входом блока коррекции ошибки, вторы входы второго элемента 2И-П1; и элемента 2И соединены соответственно с пятым входом блока коррекции ошибки с шиной записи, а выходы элементов 2И-НЕ и элемента 2И соединены с соот ветствующими выходами блока коррекции ошибки. Помимо того, что блок коррекции ошибки содержит последова тельно соединенные сумматоры по mod 2, выходы которых и вход первого сумматора по mod 2 соединены с первы ми элементами 2И, подключенными к входам элемента ИЛИ, выход которого соединен с первым входом второго элемента 2И и через первый инвертор первым входом третьего элемента 2И, вторые входы которых соединены с пер вым входом четвертого элемента 2И, ходы четвертого и третьего элементо 2И соединены с входами элемента 2ИЛ две группы -члементов ЗИ,один из входов элементов ЗИ первой группы подключен к выходу второго элемента 2И, а второй группы - к выходу элемента 2 ИЛИ, выходы первых элементов ЗИ обеих групп соединены с элементом ЗИЛИ, вторые входы элемен тов З.И обеих групп подключены соотв ственно к выходам BTopoio и третьего инверторов,вход второго инвертора соединен с вторым входом четвер того элемента 2И и выходом пятого элемента 2И, подключенного к третье му входу первого элемента ЗИ первой группы, вход третьего инвертора сое динен с выходом шестого элемента 2И подключенного к третьему входу перв элемента ЗИ второй группы, третьи входы вторых элементов ЗИ обеих гру объединены. Это позволяет производить исправление двух дефектных элементов па мяти в каждом слове при наличии двух дополнительных элементов памяти. На фиг,1 дана блок-схема запоминающего устройства; на фиг.2 и 3 схемы выполнения блока коррекции ошибки. Запоминающее устройство содержит дешифратор адреса слова 1,соединенный с адресными шинами матрицы 2 элементов памяти, причем исправных элементов памяти 3, дефектных элементов памяти 4 и дополнительных исправных элементов памяти 5, Дефектных.элементов памяти 6. Разрядные шины 7 матрицы 2 соединены с выходами первых вентилей 8 и входами блока считывания 9. Управляющие входы 10 блока считывания 9 подключены к выходам дешифратора адреса разряда 11.и к первым входам первых вентилей. Вторые входы первых вентилей 8 соединены с шиной записи 12, а третьи входы - с шиной управления 13, первым входом выходного блока 14 и входами дешифраторов. В каждом разряде разрядные ишны элементов памяти матрицы подключены к входам первого элемента 2И 15. Выход первого элемента 2И соединен с первым входом 16 блока коррекции ошибки 17 и с первым входом второго элемента 2И 18. Второй вход второго элемента 2И соединен с первым входом соответ ствующего вентиля 8 и с вторым входом блока коррекции ошибки. Выход второго элемента 2И соединен с входом элемента ИЛИ 19, выход которого подключен к третьему входу 20 блока коррекции ошибки 17 и входу инвер- тора 21. Выход инвертора соединен с четвертым входом 22 блока коррекции ошибки 17 и с первым входом первого элемента И 23. .Второй вход первого элемента И соединен с шиной разрешения записи 24 и пятым входом блока коррекции ошибки. Выход первого элемента И соединен с четвертыми входами первых вентилей. Разрядные шины 25 дополнительных элементов памяти 5 и 6 соединены с выходами вторых вентилей 26 и шестыми входами блока коррекции ошибки. Выходк 27 блока коррекции ошибки подключены к первым входам вторых вентилей. Выход второго элемента И 28 соединен с вторым входом выходного блока 14. Первый вход второго элемента И соединен с выходом блока считывания, а второй вход - с выходом 29 блока коррекции ошибки. Выходом устройства является клемма 30., На фиг.2 изображен блок коррекции ошибки для осуществления исправления одного дефектного элемента памяти в каждом слове, который содержит элемент 2И 31, первый 32 и второй 33 элементы 2И - НЕ. Выход 5 первого элемента 2И-НЕ является вы ходом блока коррекции ошибки. Перв вход этого элемента, соединен с шес тым входом блока коррекции ошибки. Второй вход первого элемента 2И-НЕ подключен к первым входам второго элемента 2И-НЕ и элемента 2И и третьим - входом блока коррекции сш ки. Вторые входы второго элемента 2И-НЕ и элемента 2И соединены соот ветственно с шиной записи 12.и с п тым входом блока коррекции ошибки. Выходы элемента 2И и второго элемента 2И-НЕ являются выходами блок коррекции ошибки. Устройство в режиме исправления одного дефектного элемента памяти работает следующим образом. При за писи информации на устройство подаются сигналы по шинам разрешения записи 24, записи 12 и управления 13. При этом происходит возбуждени выходных шин дешифраторов 1 и 11 в соответствии с кодом адреса. Возбуж денная шина дешифтора адреса слова подключает элементы памяти матрицы 2 выбранного .слова к разрядным шинам 7 и сигналы о состояних элемен тов памяти выбранного слова поступают на входы элементов 2И 15, которые анализируют - находятся или нет в выбранной строке дефектные элементы памяти 4. При выборе дефектного элемента памяти 4 на обеих разрядных шинах будут логические , так как элемент отключен. Это Приводит к появлению на выходах элементов 2И 15 единичных сигналов, которые поступают на первые входы элементов 2И 18. На вторые входы одного из элементов 2И l8 и на один из первых вентилей в поступает сигнал с одной из возбужденных шин дешифратора 11. Элементы 2И 18 анализируют - опрашивае ся дефектный элемент памяти 4 или исправный элемент памяти 3. Выбор дефектного элемента памяти 3 приводит к появлению на выходе элемента 2И 18 единичного сигнала, который, проходя через элемент ИЛИ 19 и инвертор 21, поступает на элемен И 23 и запрещает подачу сигнала ра решения записи 24 на первые вентили 8. Кроме того, единичный сигнал с выхода элемента ИЛИ 19, поступая на третий вход блока коррекции, открывает элемент 2И 31 и элемент 2И-НЕ 33 для прохождения сигналов раз решения записи и записи на второй вентиль 26. В том случае, если производится запись логической i в дефектный элемент памяти 4, т.е. его состояние согласуется с записываемой информацией, то в дополнительный элемент памяти 5 записывается логический О, в противном случае логическая . Если опрашиваемый элемент памяти исправен, то на выходе элемента 2И 18 будет нулевходом с выходом инвертора 39, а выкодом - с первымвходом элемента 2 ИЛИ 44. .Второй вход элемента 2 ИЛИ 44 соединен с выходом четБертого элемента 2И 43. Для каждого дополнитель4вой сигнал, который закроет элемс.нты 2И 31 и 2И-НЕ 33 блока коррекции ошибки 17. При этом второй вентиль 26 заперт и записи информации в дополнительный элемент памяти 5 не происходит. Кроме того, нулевой сигнал с элемента ИЛИ 19, инвертируясь инвертором 21, откроет элемент И 23 для прохождения сигнала разрешения записи 24 на первые вентили 8, происходит запись информации в исправный элемент памяти 3 матрицы 2 . В режиме считывания сигналы по шинам записи 12 и шинам разрешения записи 24 отсутствуют. При этом вентили В и 26 заперты, а сигнал о состоянии элемента памяти матрицы 2 поступает с выхода блока считывания 9 на перэый вход элемента И 28. На второй вход элемента И 28 подается сигнал с выхода 29 блока коррекции ошибки 17. На выходе элемента 2И-НЗ 32 будет нулевой сигнал, если в дефектный элемент памяти 4 записывался нулевой символ, и единичный сигнал - в противном случае. Сигнал с выхода 29 -блока коррекции ошибки, поступая на элемент И 28, производит исправление ошибки. В случае, если опрашивается исправный элемент памяти 3, то ну.тзезой сигнал на выходе элемента ИЛИ 19 установит на выходе 29 блока коррекции ошибки 17 единичный сигнал, который, поступив на элемент И 28, откроет его для прохождения сигнала с исправного элемента памяти 3, снимаеэмого с выхода блока считывания 9. Исправленный сигнал с выхода элемента И 28 через выходной блок 14 поступает Ча выход 30 vcTnnAcTBa. На фиг.З изображен блок коррекции ошибки для осуществления исправления двух дефектных элементов памяти в каждом слове,который содержит для каждого ocHOBHolo разряда матрицы 2 первый элемент 2И 34 и сумматор по 35, Первый вход сумматора по модулю два соединен с первым входом 36 блока коррекции ошибки,а второй вход - с выходом сумматора по модулю два предыдущего разряда и первым входом элемента 2И 34. Второй вход элемента 2И соединен с вторым входом 37 блока коррекции ошибки. Выход элемента 2И соединен с входом элемента ИЛИ 38. Выход элемента ИЛИ подключен к входу первого инвертора 39 и первому входу второго элемента 2И 40. Второй вход второго элемента 2И соединен с третьим входом 41 блока коррекции и с первыми входами третьего 42 и четвертого 43 элементов 2И. Третий элемент 2И 42 соединен вторым

ного разряда элементов памяти блок коррекции ошибки, кроме того, содержит пятый и шестой элементы 2И 45 и 47, второй и третий инверторы 47 и 46, группу элементов ЗИ 49 и 50. Входы элементов 2И 45 и 46 подключены к шестым входам 51 блока коррек ции ошибки. Выходы элементов 2И соединены с входами инверторов 47 и 48, а у первого дополнительного разряда и с вторым входом четвертого элемента 2И 43. Выходы инверторов соединены с вторыми входами первого и второго элементов ЗИ 49 и 50. Первые входы элементов ЗИ 49 и 50 соединены для первого дополнительного разряда элементов памяти с выходом второго элемента 2И 40, а для второго с выходом элемента 2ИЛИ 44. Третий вход вторых элементов Зи 50 соединен с пятым входом 52 блока коррекции ошибки, а выход 53 является выходом блока коррекции ошибки. Третий вход первого элемента ЗИ 49 соединен с шестым входом 51 блока коррекцииошибки. Выход первого элемента ЗИ 49 ,соединен с выходом второго элемента ЗИЛИ 54. Третий вход элемента ЗИЛИ 54 соединен с четвертым входом 55 блока коррекции ошибки. Выход 56 элемента ЗИЛИ является выходом блока коррекции ошибки. .

Работа устройства в режиме записи пр:; коррекции двух дефектных элементов памяти в слове отличается от вышеописанной работы устройства тем, что сигналы с выходов элементов 2И 15, поступая навходы 36 цепочки последовательно соединенных сумматоров по mod 2 35, суммируются и с выходов каждого сумматора 35 подаются на входы элемента 2и 34. Цепочки cy гмaтopoв 35 и элементов 2И 34 анализируют, имеется .ли слева от опрациваемого дефектного элемента памяти еще один дефектный элемент памяти в опрашиваемой строке. Это приводит к появлению на выходе элемента 2И . 34 . единичного сигнала в случае отсутствия дефектного элемента памяти слева от опрашиваемого дефектного элемента памяти или нулевого сигнала в случае наличия дефектного элемента. Этот сигнал, проходя через элемент ИЛИ 38, поступает непосредственно на элемент 2И40 и через инвертор 39 - на элемент 2И 42. Кроме , на вторые входы элементов 2И 40, 42 поступает единичный сигнал с третьего входа 41 блока коррекции ошибки, который открывает их, если опрашивается дефектный элемент памяти. Тогда единичный сигнал с выхода элемента ИЛИ 38, в случае отсутствия дефектного элемента памяти, слева от опрашиваемого дефектного элемента памяти, поступая на элемент 2И 40, формирует на выходе последнего единичный сигнал. Этот сигнал открывает элемент ЗИ 50 для ,

прохождения сигнала разрешения записи (пятого входного 52 сигнала блока коррекции ошибки) на дополнительный управляющий вентиль первого дополнительного разряда элементов памяти, куда и заносится для хранения записываемая информация. В том случае, если слева от опрашиваемого дефектного элемента памяти находится еще один дефектный элемент памяти, то на выходе элемента ИЛИ 38 будет нулевой сигнал, который, инвертируясь инвертором 39 и проходя через элемент 2И 42,формирует на выходе элемента 2ИЛИ 44 единичный сигнал. 5тот единичный сигнал откроет второй элемент ЗИ 50 для прохождения сигнала разрешения записи на дополнительный управляющий вентиль второго дополнительного разряда элементов памяти, куда и заносится для хранеНИИ записьаваемая информация..

Если в первом дополнительном разряде элементов памяти имеется дефектный элемент памяти и в него необходимо записать символ с дефектного элемента памяти матрицы, то на выходе элемента 2И 45 этого разряда будет единичный сигнал, который, проходя через открытый элемент 2И 43 и элемент 2ИЛИ 44 и поступая на второй элемент ЗИ 50, откроет его для прохождения сигнала разрешения записи

на дополнительный управляющий венгиль второго дополнительного разряда элементов памяти.Одновременно единичный сигнал с выхода элемента 2И 45 первого дополнительного разряда элементов памяти,инвертируясь инвертором 47,закроет второй элемент ЗИ 50 этого разряда для прохождения сигнала разрешения записи на соответствующий, дополнительный управляющий вентиль.

В режиме считывания работа устройiCTBa происходит следующим образом. ;При опросе дефектного элемента памяти матрицы формируются аналогичным образом, как при записи информации, единичные сигналы, которые открывают соответствующие элементы ЗИ 49 для прохождения сигналов, снимаемых с прямых разрядных шин дополнительных элементов памяти. Сигналы с выходов элементов ЗИ 49 и четвертого входа 55 подаются на входы элемента ЗИЛИ 54 и тогда на выходе-56 элемента ЗИЛИ 54 будет нулевой сигнал, если в дефектный элемент памяти записывался нулевой символ, и единичный сигнал в противном случае.

Сигнал с выхода 56, поступая на элемент И 28, производит исправление. В этом случае, если опрашивается исправный элемент памяти, то на четвертом входе 22 и на выходе 29 блока коррекции ошибки будет единичный сигнал, который откроет элемент И 28, не исправляя считываемого символа с выхода блока считывания 9.

Формула изобретения

а третьи входы - с шиной управления, первым входом выходного блока и входами дешифраторов, шину разрешения записи, отличающееся тем что, с целью повышения надежности устройства, оно содержит дополнительные элементы памяти, блок коррекции ошибки, вторые вентили, два элемента И, инвертор, элемент ИЛИ и в каждом разряде два последовательно соед iieHHbix элемента 2И, входы первых элементов 2И подключены к разрядным шинам матрицы элементов памяти, при этом выход первого элемента 2И соединен с первым входом блока коррекции ошибки, второй вход второго элемента 2И соединен с первым входом соответствующего первого вентиля и с вторым входом блока коррекции ошибки, выход второго элемента 2И соединен с входом элемента ИЛИ, выход которого соединен с третьим входом блока коррекции ошибки и входом интвертора, выход которого соединен с четвертым входом блока коррекции ошибки и с первым входом первого элемента И, второй вход которого соединен с шиной разрешения записи и пятым входом блока корс екции ошибки, а выход с четвертыми входами первых вентилей, разрядные шины дополнительных элементов памяти соединены с выходами вторых вентилей и шестыми входами блока коррекции ошибки, выходы которого соединены с первыми входами вторых вентилей, выход второго элемента И соединен с вторым входом выходного ,блока, первый вход второго элемента И соединен с выходом блока считывания, а второй вход - с выходом блока коррекции ошибки.

0 а выходы элементов 2И-НЕ и элемента 2И соединены с соответствующими выходами блока коррекции ошибки.

5 соединенные сумматоры по mod 2, выходы которых и вход первого сумматора по mod 2 соединены с первыми элементами 2И, подключенными ко входам элемента ИЛИ, выход которого соединен с

0 первым входом второго элемента 2И и через первый инвертор с первым входом третьего элемента 2И, вторые входы которых соединены с первььм входом четвертого элемента 2И, выходы четвер5того и третьего элементов 2И соединены с входами элемента 2ИЛИ, две группы элементов ЗИ, один из входов элементов ЗИ первой группы подключены к выходу второго элемента 2И, а второй группы - к входу элемента 2ИЛИ, выходы первых элементов ЗИ обеих групп соединены с элементом ЗИЛИ, вторые входы элементов ЗИ обеих групп подключены соответственно к выходам второго и третьего инверторов, вход второго инвертора соединен с вторым входом четвертого элемента 2И и выходом пятого элемента 2И, подключенного к третьему входу первого элемента ЗИ первой группы,вход третьего инвертора соединен с выходом шестого элемента 2И, подключенного к третьему входу первого элемента ЗИ второй группы,третьи входы вторых элементов ЗИ обеих групп-объединены.

5

Источники информации, принятые во внимание при экспертизе

2,Сб.статей Микроэлектроника под ред. Ф.В.Лукина. М., Сов.радио, 1972, вып.5, с.128-150.

О

Авторы

Даты

1979-02-25—Публикация

1975-08-12—Подача