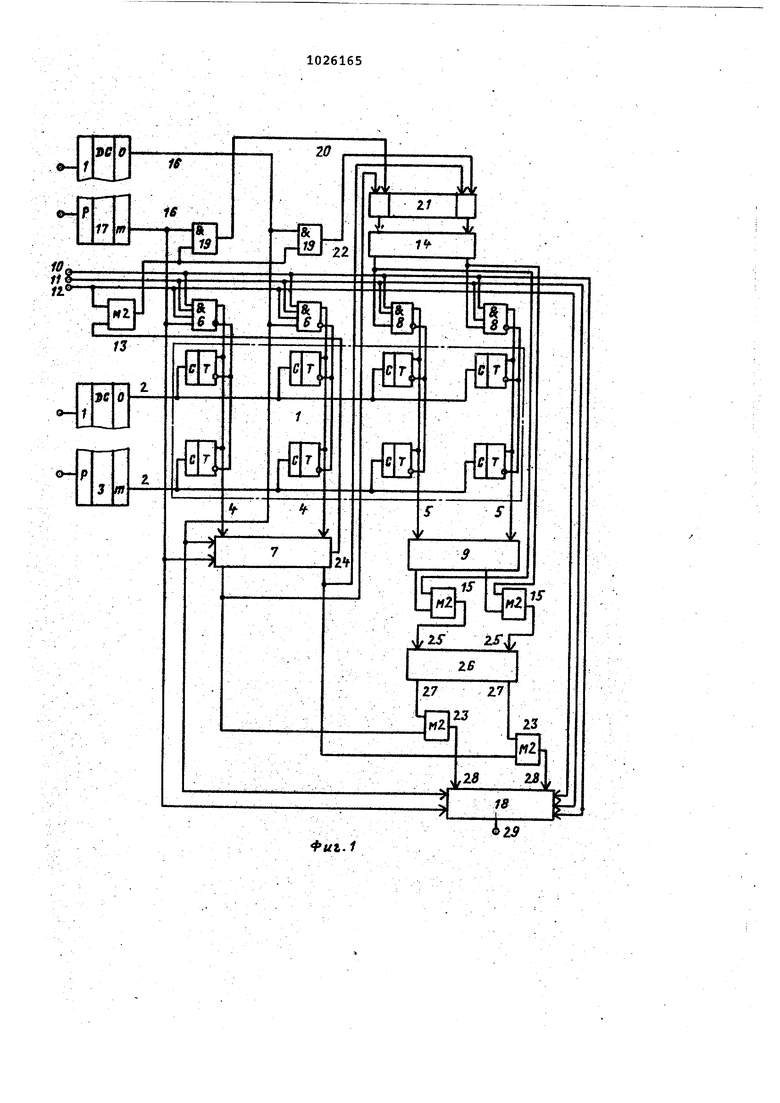

Изобретение относится к вычисли тельной технике и может быть исполь зовано в электронной промышленности при изготовлении больших интегральны схем запоминающих устройств (БИС ЗУ Устройство целесообразно использовать при изготовлении БИС ЗУ, имею щих большую площадь кристаллов, где требуется увеличить выход правильно функционирующих устройств, а также при создании систем, памяти, удовлетворяющих заданному уровню надежности хранения информации-. Известны полупроводниковые ЗУ, ко торые содержат накопитель и схемы ло гики обрамления, позволяющие производить обращение при записи и считывании информации к одному или к нескольким элементам памяти ЭП накопителя С 1 . Однако работоспособность таких устройств нарушается при отказах ЭП накопителя. Наиболее близким к предлагаемому является запоминающее устройство с автономным контролем, содержащее накопитель, числовые шины которого соединены с выходами дешифратора адреса строк, а выходные, шины - с информационными входами первого блока считывания, выходами первых-вентилей и информационными входами второго блока считывания, выходами вторых вентилей соответственно, первые и вторые входы первых и вторых вентилей подключены к шинам разрешения записи и управления, третьи входы их - к шине записи и выходам блока кодирования соответственно, четвертые входы первых вентилей связаны с выходами дешифратора адреса разрядов, управляющими входами первого блока считывания и первыми управляющими входами выходного блока, выходы второго блока считывания соединены с первыми входами- первых сумматоров по 1иодулю два, выходы которых являются входами блока анализа отказов, выходами соединенного с пер выми входами вторых сумматоров по модулю два, вторые входы вторых сумматоров по модулю два; соединены с первыми выходами первого блока считывания, а выходы вторых сумматоров по модулю два связаны с информационными входами выходного блока, вторые управляющие входы которого соединены с шинс1ми разрешения записи, управления и записи 2J. В устройстве при записи информации в накопитель первый блок кодиро вания вырабатывает г дополнительных Л проверочных) разрядов в соответстВИИ с применяемым кодом. Например, при использовании кода Хемминга, ис правляющего одиночные ошибки, г вы бирается из условия k r-.IIJJ где k соответствует числу информационных разрядов. Далее эти разрядов записываются в накопитель. При считывании информации второй блок кодирования по считанным k разрядам (в слове могут быть ошибки) г вновь вырабатывает г (при наличии ошибок вектора г и г отличаются) проверочных разрядов, которые сравниваются с j разрядами, хранившимися в дополнительных ЭП строки. В результате этого сравнения вырабатывается проверочный вектор (синдром, анйлиз которого блоком определения местоположения отказа позволяетустановить отказавший дефектный разряд и исправить его. Использование двух блоков кодирования - записываемого и считываемого слов - приводит к дополни: тельному увеличению площади кристалла, что, в свою очередь, вызывает появление на кристалле дополнительных дефектов в процессе его производства и отказов при эксплуации. В качестве базового объекта выбрана БИС ЗУ типа К541РУ1, выпускаемая отечественной промышленностью. Это устройство емкостью 4 Кбит 1 позволяет производить обращение.к любому одному ЭП накопителя для записи или считывания информации t JОднако это устройство не может быть использовано, если при .его производстве возникли единичные дефекты ЭП. Кроме того, такие устройства становятся неработоспособными при возникновении отказов ЭП в процессе эксплуатации БИС ЗУ. Цель изобретения - упрощение устройства и повьошение его надежности. Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее накопитель, числовые шины кото-т рого соединены с выходами дешифра- : тора адреса строк, а выходные шины с информационными входами первого блока считывания, выходами первых вентилей и информационными входами второго блока считывания, выходами .вторых вентилей соответственно,: первые и вторые входы первых и вторых вентилей подключены к шинам разре-. шения записи и управления, третьи их входы - к шине записи и выходам блока кодирования соответственно, четвертые выходы первых вентилей связаны с выходами дешифратора адреса разрядов управляющими входами первого блока считывания и первыми управляющими входами выходного блока, выходы второго блока считывания соединены с первыми вх.одами первых сумматоров по модулю два, выходы которых являются входами блока анализа отказов, выходами соединенного с первыми входами вторых сумматоров по модулю два, вторые выходы вторы сумматоров по модулю два соединены с первыми выходами первого блока считывания, а выходы вторых суммато ров по модулю два связаны с информационньми входами выходного блока вторые управляющие входы которого соединены с шинами разрешения записи, управления и записи, введены третьи вентили, первые входы которы подключены к выходным шинам дешифра тора адреса разрядов, вторые входы третьих вентилей соединены с выходом третьего сумматора по модулю два, первый и второй входы которого соединены с итной записи и вторым выходом первого блока считывания соответственно, выходы третьих вентилей подключены к вторым входам регистра, первые входу которого сое динены с первыми выходами первого блока считывания, а выходы его - к входам блока кодирования, выходы которого подключены к вторым входам первых сумматоров по модулю два. Это позволяет корректировать в каждой строке накопителя один отказ ;{дефект в режиме считывания информации при невысокой .сложности схем коррекции.. На фиг. 1 изображена функциональ ная схема устройства} на фиг. 2 блок анализа отказов. Устройство содержит накопитель 1 числовые шины 2 которого соединены с выходами дешифратора 3 адреса строк. Основные 4 и дополнительные 5 выходные шины накопителя 1 соединены соответственно с выходами первых вентилей 6, информационными вхо дами первого блока 7 считыванид и выходами вторых вентилей 8, а также с инфбрмационными входами второго блока 9 считывания. Первые и вторые входы первых 6 и вторых 8 вентилей соединены соответственно с шинами разрешения записи 10 и управления 1 а третьи их входы - с шин.ой 12 записи, первым входом третьего сум:матора 13 по модулю два и с выходами блока 14 кодирования, связанны ми также с вторнми входами первых сумматоров 15 по модулю два. Четвер тые входы первых вентилей 6 связаны выходами 16 дешифратора 17 адреса разрядов, управляющими входами перв го блока 7 считывания и первыми управляющими входами выходного блока 18, а также с вторыми входами треть вентилей 19, первые входы которых соединены с выходами третьего сумматора 13 по модулю два. Выходы тре их вентилей 19 соединены с вторыми 20 входами регистра 21, первые входы 22 которого подключены к первым выходам первого блока 7 считывания вторым входам вторых сумматоров 23 по модулю два, второй выход 24 первого блока 7 считывания связан с вторым входом третьего сумматора 13 по модулю два. Выходы регистра 21 являютсявходами блока 14 кодирования. Выходы второго блока 9 считывания соединены с первыми входами первых сумматоров 15 по модулю два, выходами связанных с входами 25 блока 26 анализа отказов. Выходы 27 блока 26 являются первыми входами вторых сумматоров 23 по модулю два. Вы|Ходы сумматоров 23 соединены с информациониыми входами 28 выходного блока 18, выход 29 которого является выходом устройства, а сигналы шин 10-12 являются вторьми управляющими входами выходного блока. . Пример реализации блока 26 анализа отказов показан на фиг. 2. Схема представляет собой програм/мируемУю логическую матрицу (ПЛМ, можно использовать вместо ПЛМ, ПЗУ) состоящую.из инверторов 30 и вентилей (не показаны). К вентилям осуществляется подключение (условно обозначено кружочком} 31 либо прямого, либоИнвертированного входного разряда 25. Таким образом, к каждому вентилю подключены 1 сигналов. Принцип работы устройства основан на свойстве кода Хемминга/ состоящем в том, что при любой последовательности расположения вектор-столбцов в проверочной матрице .3 поразрядНое сравнение наборов контрольных разрядов ( V указывает местоположение отказа, если он есть. Устройство работает следующим образом. В режиме записи информации на входы дешифратора 3 адреса строк поступает код адреса опрашиваемой строки, в результате чег возбуждается одна из Ун выходных шин 2 деш ифратора 3, т.е. выбирается одна из строк. Информационные разряды (К ) слова считываются по шинам 4 и поступают в первый блок 7 считывания и дальше с , выходов блока 7 поступают на первые 22 входы регистра 21. Таким образом, 1l разрядов опрашиваемой строки записываются в регистр 21. Одновременно с этим на входы дешифратора 17 адреса разрядов поступает код сшреса разряда, на пересечении которого со строкой находится выбираемый ЭП. Сигнал с одной, из возбужденных шин 16 дешифратора 17, поступая на один из управляющих входов первого блока 7 считывания, вызывает появление на втором 24 выходе блока 7 ин.фОЕадации 41 или 0), хранящейся в опрашиваемом ЭП. Этот сигнал поступает на второй вход третьего сумматора 13 по модулю два и сравнивается с сигналом, установленным для Записи на шине 12 запиСи.Если срав .ниваемые сигналы отличается, тог на выходе третьего сумматора 13 появит ся единичный сигнал. Этот сигнал через третий вентиль 19, на первый вход которого действует единичный сигна л с возбужденной шины дешифратора 17 адреса разрядов поступит на второй вход 22 соответствующего раз ряда регистра 21 и инвертирует хранящийся в нем символ. Если же записываемый в ЭП и хранящийся в нем символы совпадают, то изменения информации в регистре не происходит. На основании ( информационных символов V хранящихся в регистре 21, блок 14 -кодирования вырабатываетТ проверочных символов, которые поступают на третьи входы вторых вентилей 8, а на третьих входах первых вентилей установлен сигнал 12 записи. После, этого на шине 10 появляется сигнал разрешения записи информации в эй, находящийся на пересечении выбранных строки и разряда, из выбранных ЭП, а также в И дополнительных ЭП происходит запись информации. На этом цикл записи закончен. В режиме считывания сигналы на шинах 10 и 12 отсутствуют, вёнтили и 8 заперты. В соответствии с кодом адреса опрашиваемой строки возбуждается одна из шин 2 дешифратора 3 и все ЭП этой строки подключаются соответственно Через основные 4 li дополнительные 5 выходные шины на копителя 1 к первому 7 и второму 9 блокам считывания. По считанным it информационным символам, поступающи по первым входам 22 в регистр 21, в блоке 14 кодирования вырабатываются И (г--Гг однако векторы) и г м гут отличаться) контрольных символов. Эти символы поступают на входц первых сумматоров 15 и сравниваются в них поразрядно с к сим волами, поступающими на первые входы сумматоров 15. Если в считанном сло ве {и его разрядах) нет отказов, то на выходах первых сумматоров 15 буд нулевые символы синдром равен нулю В противном случае синдром нулю не равен. Синдром по входам 25 поступа ет в блок 26 анализа отказов. В бло ке 26 Д фиг. 2) запрограммированы It двоичных слов по у разрядов соответствующие вектор-столбцам матрицы Ну,|К применяемого кода. Так1Ш образом, синдром, сформулированный первыми сумматорами 15, сравнивается с кащцлм из fc векторов, хранящихся в ПЛМ. При совпадении с одним из векторов s считанном слове есть ошибка) на соЬтветствующем выходе 27 сформируется единичный сигнал, и таким образом, однозначно установитс местоположение отказавшего разряда, Далее этот .единичный сигнал поступает на первый вход одного из вторых сумматоров 23 по модулю два, второй вход которого связан с неверно считанным информационным разрядом, и инвентирует ошибочный разряд на правильный. Скорректированное слоцо поступает на информационные входы 28 выходного блока 18. На первые управляющие входы выходного блока 18 поступает сигнал с возбужденной шины 16 дешифратора 17 адреса разрядов и из {( информационных разрядов на выход 29 устройства поступает символ, расположенный в ЭП, местоположении которого определяется кодами адресов строки и разряда. Естественно, что при определенном считываний информа1Дии из. ЗУ любая ошибка, имеющаяся . в 1 -разрядном слове, будет коррек- i тироваться вНе зависимости от того, считывается из устройства этот разряд или другой.. .Рассмотрим для примера запись и считывание слова А 1010 ( 4 .{записывается и считывается симврл , О во второй разряд строки). Для обнаружения и исправления ошибки используем код Хемминга с проверочной матрицей-H-J,4 , т.е. У , 3: 1 1 01 10 О Н 1 01 1 О 1 ,0 О 11 1 О 01 .С с с с с с с На основании этого кода блок 16 кодирования вырабатывает 3 проверочных символа Cg- С ji по алгоритму. С Cjj - Cij, - С4 сложение Cfc . С - С - С4 . ведется GI Cj. 7 Cj С4 ПО модулю два в :накопитель запишется слово Б 1010 .101. При считывании информации на первых выходах первого блока 7 считывания будет слово А 1110 (сшгабка во втором разряде). Вновь сформированные разрядов рОО) сравниваются на первых сумматорах 15 поразрядно с г символами (lOl/. Синдром ( 6 101} поступает на входа ; блока 25, в котором хранятся ( вектор-Столбцы матрицы Н-. Сийдром совпадает с вторым С вейтором, и на; Втором выходе 27 блока 26 будет единичный сигнал, который на втором сумматоре 23 инвертирует единичный Символ на нулевой. Таким образом, на выходе 29 устройства,будет правильный двоичный симврл О. Если в считанном слове ошибок нет или искажен один из символов, то синдром не совпадает ни с одним из вектор-столбцов, хранящихся в ПЛМ и все, л символов будут правильными -. Предлагаемое .устройство вьшолняет те е функции, что и известное обнаруживает и исправляет единичные дефекты в словах, возникшие по причине отказов ЭП в процессе производства ВИС ЗУ либо его. эксплуатации. Однако предлагаемое устройство проще за счет того, что кодирование информации и в режиме записи, и в режиме сч:итывания осуществляется; одним и тем же блоком кодирования/ в то время как в известном устройстве для этих целей используются два блока кодирования. Анализ, приведенный в описании С2 устройства, показывает, что для БИС ЗУ емкостью 16 Кбит (г 8) под дополнительные ЭП, схемы кодирования, обнаружения и исправления ошибок необходимо увеличить площадь кристалла приблизительно на 18%. Причем 8-10% (из 18%7 заиимают схемы кодирования и определения местоположения оошбки. Даже предварительные подсчеты показывают что длА формирования г проверочнь х разрядов кодом Хемминга-. (самым простым и эффективным 3 нужно около двухйходовых сумматоров по модулю два. Это значит, что для БИС ЗУ емкостью 16 КБИТ (128-128) необходимо 8 64 - 512 сумматоров для

реализаций одного блока кодирования что потребует увеличения площади кристалла на 4-5%. О7метим, что в предлагаемом устройстве формирование блока определения местоположения отказов в виде ПЛМ или ПЗУ не требует проведения дополнительных технологических операций по сравнению с базовым процессом и практически не влияет на выход грл;ных ЗУ из-эа усложнения техпроцесса.

Таким образом, использование лии1ь одного блока кодирования значительно улучшает известное устройство, уменьшает площадь кристалла, что приво;фЕ1Т k повышению надежности всего устройства.

В сравнении с базовым объектом предлагаемое устройство позволяет использовать кристаллы БИС ЗУ с единичными дефектсши производства и исправлять отказы, возникающие при использовании ВИС. 7аким образом, надежность предлагаемого устройства выше, чем базового.

Фиг.1

19

ut.i

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1238163A1 |

| Запоминающее устройство | 1981 |

|

SU1010654A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Устройство для коррекции отказов в полупроводниковой памяти | 1982 |

|

SU1049981A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955209A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЬИ КОНТРОЛЕМ, содержащее накопитель , числовые шины которого сое- динены с выходами дешифратора адреса строк, а выходные шины - с информационными входами первого блока считывания, выходами первых вентилей и информационными входс1ми второго блока считывания, выходами вторых вентилей соответственно, первые и .вторые входы первых и вторых вентилей: подключены к шинам раэрешения записи и управления, третьи их входы к шине записи и выходам блока кодирования соответственно, четвертые входы первых вентилей сйязаны с выЕшл;; ходами дешифратора адреса разрядов; управляющими входами первого блока считывания и первыми управляйщими входами выходного блока, выходы второго блока считывания соединены спервыми входами первых сумматоров по модулю два, выходы которых являются входами блока анализа отказов, выходами соединенного с первыми входами вторых сумматоров по модулю два, вторые входы вторых сумматоров по модулю два соединены с первыми выходами первого блока считывания, а выходы вторых сумматоров по модулю два связаны с информационными вхо-, дами выходного блока, вторые управ-i лякадие входы которого, соединены с § шинами разрешения записи, управления и записи, от ли чаю щ е е с я тем, что, с целью упрощения устройства и повышения его надежности , в него введены третьи вентили, первые входы которых подключе§ ны к выходным шинамг-дешифратора адреса разрядов, вторые входы третьих вентилей соединены с выходом третьего сумматора по модулю два, и второй входы которого соединены o с шиной записи и вторым выходом первого блока считывания соответ л ственно, выходы третьих вентилей подключены к вторым входам peijHCTсЬ ел ра, первые входы которого соединены с первыми выходами первого блока ; .считывания, а выходы его - к входам блока кодирования,, выход которого подключен к вторым входам первых сумматоров по модулю два.

Авторы

Даты

1983-06-30—Публикация

1982-03-16—Подача