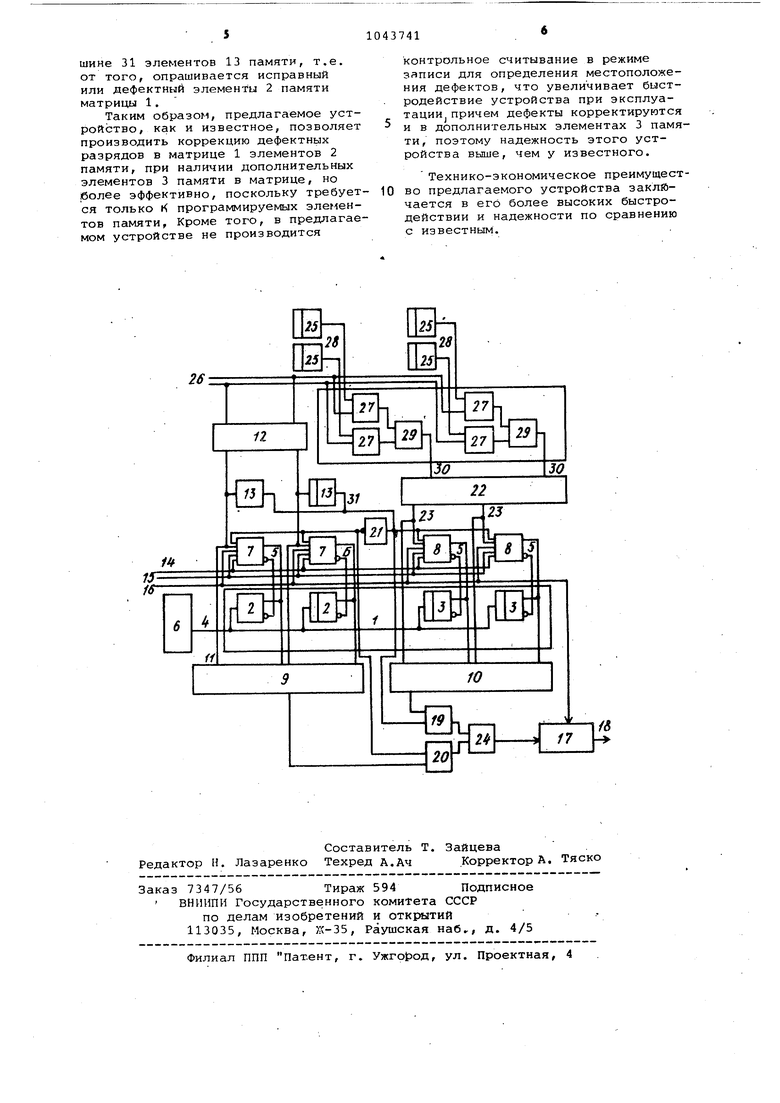

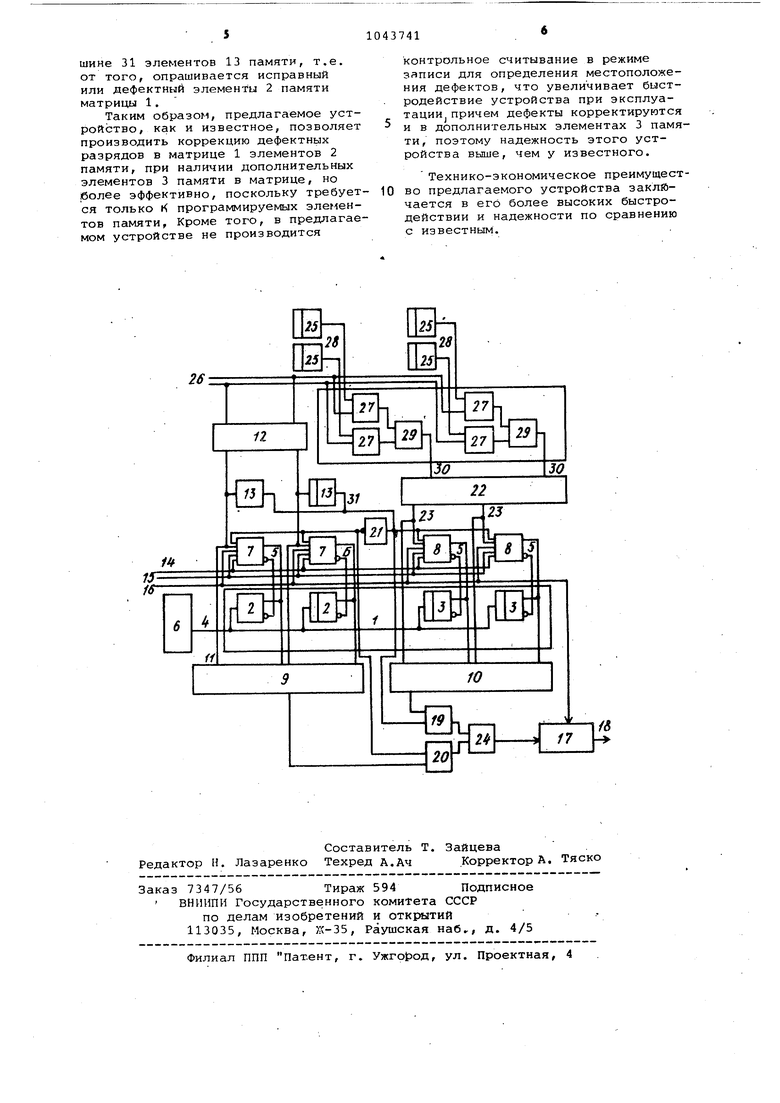

Изобретение относится к вычислительной технике и может быть исполь зовано при изготовлении больших интегральных схем запоминающих: устройств. Известно запоминающее устройство содержащее матрицу элементов памяти схемы логики обращения и коррекции, позволяющие производить обход дефек ных разрядов элементов памяти благо даря наличию дополнительных избыто яых разрядов в матрице l . Недостатком этого устройства является низкая- надежность. Наиболее близким по технической сущности к изобретению является запоминающее устройство, содержащее дешифратор адреса слова, соединенны с адресньлми шинами матрицы элементо памяти, разрядные шины которой соединены с выходами первый и вторых вентилей, информационными входами первого и второго блоков считывания управляющие входы первого блока счи тывания соединены с выходами дешифратора адреса разряда, первыми входами первых вентилей и адресными входами первых программируемых элементов памяти, вторые, третьи, четвертые и пятые входы первых и вторых вентилей соединены соответственно с шинами разрешения записи, упра лелия и первым входом выходного бло ка, разрядной шиной первых программи руемых элементов памяти и первыми входами первого и второго элементов И через инвертор и нейосредственио, первые входы вторых вентилей соединены с выходами дополнительного дешифратора и управляющими входами .второго блока считывания, выходы первого и второго блоков считывания соединены соответственно с вторыми входами первого и второго элементов И, выходы первого и второго элементов И соединены через элемент ИЛИ с вторым входом выходного блока, выход выходного блока является выходом устройства, входы дешифратора адреса разряда, вторые программируемые элементы памяти, программирование первы и вторых программируемых элементов пдмяти осуществляется с помощью лазера 2 . Недостатками известного устройства являются сложность схем коррекции из-за необходимости хранить код адреса дефектного разряда в дополнительной памяти и низкое быстродействие из-за необходимости проведения контрольного считывания в режиме записи для определения дефектности разряда. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в запоминающее устройство, содержащее матрицу основных и дополнительных элементов ламяти, дешифраторы адреса, первую и вторую группы программируемых элементов памяти, блоки считывания, блок вывода данных, группы элементов И, элемент НЕ, элемент ИЛИ и элементы И адресные входы основных и дополнительных элементов памяти подключены к выходам первого дешифратора адреса, инверсные выходы элементов И первой и второй групп соединены с входами записи основных и дополнительных элементов памяти соответственно, прямые выходы элементов И первой группы и выходы основных элементов памяти подключены к информационным входам первого блока считывания, управляющие входы которого соединены с выходами второго дешифратора адреса, первыми входами элементов И первой группы и входами программируемых элементов памяти первой группы, выходы которых подключены к входу элемента НЕ, первому входу первого элемента И и первым входам элементов .И второй группы, вторые входы которых соединены с выходами третьего дешифратора адреса и управляющими входами второго блока считывания, информационные входы которого подключены к выходам дополнительных элементов памяти ,и выходам элементов И второй группы, в.ыход элемента НЕ соединен с первым входом второго элемента И и вторыми входами элементов И первой группы, выходы первого и второго блЪков считывания подключеньа к вторым входам второго и первого элементов И соответс твенно, выходы которых соединены с входами элемента ИЛИ, выход которого подключен к первому входу блока вывода данных, вьисод которого является выходом устройства, а второй вход является управляющим входом устройства и соединен с третьими входвв«1И элементов И первой и второй групп, четвертые и пятые входы которых соответственно объединены и являются входом записи и входом разрешения записи -устройства, адресными входами которого являются входы второго дешифратора адреса, введены третья группа элементов И, вы- . ходы которых соединены с входами элементов ИЛИ группы, выходы которых подключены к входам третьего дешифратора адреса, причем первые входы элементов И третьей группы соединены с выходами программируемых элементов памяти второй группы, а вторые входыс входами второго дешифратора адреса. На чертеже изображена функциональная схема предлагаемого устройства. Устройство содержит матрицу 1 основных- 2 и дополнительных 3 элементов памяти с адресными i и разряднети 5 шинами, первый дешифратор 6 адреса, предназначенный для дешифрации адреса слова, первую 7 и втору з 8 группы элементов И, первый 9 и вто рой 10 блоки считывания. На чертеже обозначены управляющие входы.11 первого блока считывание. Устройство со держит также второй ЛеЪифратор 12 ад реса, предназначенный для дешифрации адреса -разряда основных элементов памяти, первую группу программируемых элементов 13 памяти. На чертеже обозначены также вход 14 разрешения .записи, вход 15 зэписи и управляющий вход 16 устройства. Устройство содержит также блок 17 вывода данных с выходом 18, первый 19 и второй 20 элементы И, элемент НЕ 21, третий дешифратор 22 адреса, предназначенный для дешифрации адреса разряда дополнительных элементов пгадяти, с выходами 23, элемент ИЛИ 24, вторую группу программируемых элементов 25 памяти. На чертеже обозначены также адресные входы 26 устройства. Кроме того, устройство содер жит третью . . группу элементов И 27 с первыми входами 28 и группу элементов ИЛИ 29 с выходами 30. Программируемые элементы памяти первой группы организованы в матрицу с одноразрядной шиной 31 и 2 адрес.- ными входами, где k - число основных элементов памяти. Программирование элементов 13 и 25 памяти осуществляется путем переж гания плавки связей с помощью лазера. , . . . . Устройство работает следующим образом. При изготовлении и при обнаружени дефектных элементов 2 памяти в матри це 1 в программируенвле элементы 13 памяти, соответствующие дефектным . разрядам в матрице 1, заносятся едйничные сигналы. Кроме того, путем программирования единичных бигналов в элементах 25 памяти на выходы 30 коглиутируются п разрядов из k входов 26 (гдеп и).При коррекции двух дефектных разрядов используется только один любой разряд входного адреса, в котором сигнгшы отличаются друг от друга (при дефектности, например, разрядов в матрице 1 с адресами 10000 и11000. второ слева адресный разряд выбирается на выход 30) . При коррекции одного дефектного разряда в разрядах элементов 2 памяти матрицы 1 вначале выбирается в дефектном входом адресе 26 разряд, содержащий нулевой сигнал, путем программирования соответствующего элемента 25 памяти. Если же разряд элементов 3 памяти матрицы 1 соответствующий этому адресу, является также дефектным, то в адресе на входах 26 выбирается дополнительНО еще один разряд, содержащий единичный сигнал, путем программирования второго из элементов 25 памяти. При эксплуатации при записи информации- на входы 14-16 устройства подаются сигналы разрешения записи, записи и управления соответственно. ПриЭТОМ происходит возбуждение дешифраторов 6 и 12 в соответствии с кодом адреса запрашиваемого элемента 2 памяти матрицы 1. Возбужденный выход 4 дешифратора подключает элементы 2 и 3 памяти выбранного слова к разрядным шинам 5.. Одновременно происходит опрос соответствующего элемента 13 памяти единичным сигналом, с одного из входов 11 дешифратор; ра 12.Если опрашивается исправный разряд элементов 2 памяти/ то на шине 31 появится нулевой сигнал, который закроет элементы И 8 и, проходя через элемент НЕ 21, откроет элементы И 7. Тем самым, в разряд элементов 2 памяти матрицы 1, открытый сигна.лом с одного из выходов 11 дешифратора 12, происходит запись информации, поступающей по входу 15. Если опрашивается дефектный разряд элементов 2 памяти, то на шине 31 появится единичный сигнал, который откроет вторые элементы И 8 и, проходя через элемент НЕ 21, закроет элементы НЕ 7. Тогда в разряд элементов 3 произойдет записБ информации по алресу, поступающему с выходов 30 элементов ИЛИ 29 и вычисленному де П1ифратором 22. Прямой и инверсный сигналы с двух 23 дешифратора 22. управляют выбором соответственно первого-и второго разрядов элементов 3 памяти матрицы 1. Сигнал на выходе 30 элемента ИЛИ 29 соответствует сигналу на однсзм из входов26, в котором сигналы в адресах двух дефектных разрядов ;Отлччаются друг от друга. Если же в матрице 1 содержится два дефектных разряда, один из которых относится к элементам 3 памяти, то благодаря соответствующему программированию при производстве всегда будет опрашиваться один из .исправных разрядов элементов 3 памя;ти по нулевому или единичному сигналу с выхода 30. В режиме считывания сигналы на входах 14 и 15 отсутствуют. При этом элементы И 7 и 8 заперты, а сигнал О7СОСТОЯНИИ опрашиваемого основного 2 или дополнительного 3 элементов памяти матрицы 1 поступает с выходов блоков 9 или 10 через элементы И 20 19, элемент ИЛИ 24, блок 17 на выход 18 устройства. Так же как и в режиме записи, выделение хранигмого сигнала или с блока 9, или с блока 10 зависит от сигнала на

шине 31 элементов 13 памяти, т.е. от того, опрашивается исправный или дефектный элементы 2 памяти матрицы 1.

Таким образом, предлагаемое устройство, как и известное, позволяет производить коррекцию дефектных разрядов в матрице 1 элементов 2 памяти, при наличии дополнительных элементов 3 памяти в матрице, но более эффективно, поскольку требуется только К программируемых элементов памяти, Кроме того, в предлагаемом устройстве не производится

контрольное считывание в режиме записи для определения местоположения дефектов, что увеличивает быстродействие устройства при эксплуатации причем дефекты корректируются и в дополнительных элементах 3 памяти, поэтому надежность этого устройства выше, чем у известного.

Технико-экономическое преимуадество предлагаемого устройства заклйчается в его более высоких быстродействии и надежности по сравнению с известным.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией дефектных элементов памяти | 1981 |

|

SU980165A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Постоянное запоминающее устройство | 1975 |

|

SU733025A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство | 1975 |

|

SU649044A1 |

| Запоминающее устройство с коррекцией информации | 1981 |

|

SU957273A1 |

| Запоминающее устройство | 1981 |

|

SU963089A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее матрицу основных и дополнительных элементов памяти, дешифраторы адреса, первую и вторую группы программируемых элементов памяти, блоки считывания, блок вывода данных, группы элементов И, элемент НЕ, элемент ИЛИ и элементы И, причем адресные входы основных и дoпoJ нитeльныx элементов памяти подключены к выходам первого дешифратора адреса, инверсные выходы элементов И первой и второй групп соединены с входами записи основных и дополнительных элементов памяти соответственно, прямые выходы элементов И первой группы и выходы основных элементов памяти подключены к информационным входам первого блока считывания, управляющие выходы которого соединены с выходами второго деигифра1гора адреса, первыми входами элементов И первой группы и входгили программируемых элементов памяти первой группы, выходы которых подключены ко входу элемента ЙЕ, первому , входу первого элемента И и первым входам элементов И второй группы, вторые входы которых соединены с выходами третьего дешифратора адреса и управляквдими входами второго блоки считывания, информационные входы которого подключены к выходам дополнительных элементов памяти и выходам элементов И второй группы, выход элемента НЕ соединен с первым входом второго элемента И и вторыми входами элементов И первой группы, выходы перв.ого и второго блоков считывания подключены к вторым входам второго и первого элементов И соответственно, выходы которых соединены с входами элемента ИЛИ, выход которого подключен к первому вХойу бло ка вывода данных, выход которого является выходом устройства, а второ вход является управляющим входом уст ройства и соединен с третьими входги и элементов И первой и второй групп, четвертые и пятые входы которых соответственно объединены и являются входом записи и входом разре-шения записи устройства, адресными 4 СО входами которого являются входы второго дешифратора адреса, о т л и- ча.ющееся тем, что, с целью 4 повыцения быстродействия устройства, в него введены третья группа элементов И, выходы которых подключены к .входам элементов ИЛИ группы входы которых подключены к входам Третьего дешифратора адреса-, причем первые входы элементов И. третьей группы соединены с выходами программируемых, элементов памяти второй группы, а вторые входы - с входами второго дешифратора адреса.

2ff

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Щетинин Ю.И | |||

| и др | |||

| Способы использования кристаллов ЗУ с де- , фектными запоминающими элементами | |||

| Зарубежная электро.нная техника, 1978, № 20, с.6, рис.1,2 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-09-23—Публикация

1982-04-28—Подача