(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ YCTPOfiCTBO

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955209A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Постоянное запоминающее устройство | 1975 |

|

SU733025A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Запоминающее устройство | 1975 |

|

SU714496A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в электронной промышленности при изготовлении больших интегральных схем программируемых постоянных заноминаку-, ших устройств (ППЗУ).

Известны ППЗУ. содержащие матрицу, элементов памяти, дешифраторы слова и разряда, селектор, вентили считывания, усилители считывания til - ГзЗ .

Однако в этих устройствах, элементы памяти матрицы соединены с разрядными шинами плавкими п емычками или р - п -переходами, которые разрушаются при записи информашш в соответствии с кодом, подлежащим хранению в ППЗУ. До занесения программируемого кодй в матрицу в информационном поле содержатся только единицы. Работоспособность ППЗУ нарушается при наличии дефектного нуля в информационном поле матрицы, когда никаким способом не удается записать на место дефектного элемента единицу. Эти уст

ройства обеспечивают обращение к лк бому одному элементу памяти накопителя.

Наиболее близким по технической сущности к изобретению является постоянное запоминающее устройство содержащее дешифратор адреса слова, соединенный с Адресными шинами матричного накопителя селектор, первые входы которого соединены с выходами дешифратора ад10реса разряда, а выход - с первым входом сумматора по модулю два, второй вход которого соединен с блоком исправления ошибок, выход сумматора по модулю два подключен к первому вхо15ду вентиля считывания, а выходом - с входом усилителя считывания, второй и третий входы блока исправления ошибок подключены соответственно к :первой, второй и третьей дополнительным

20

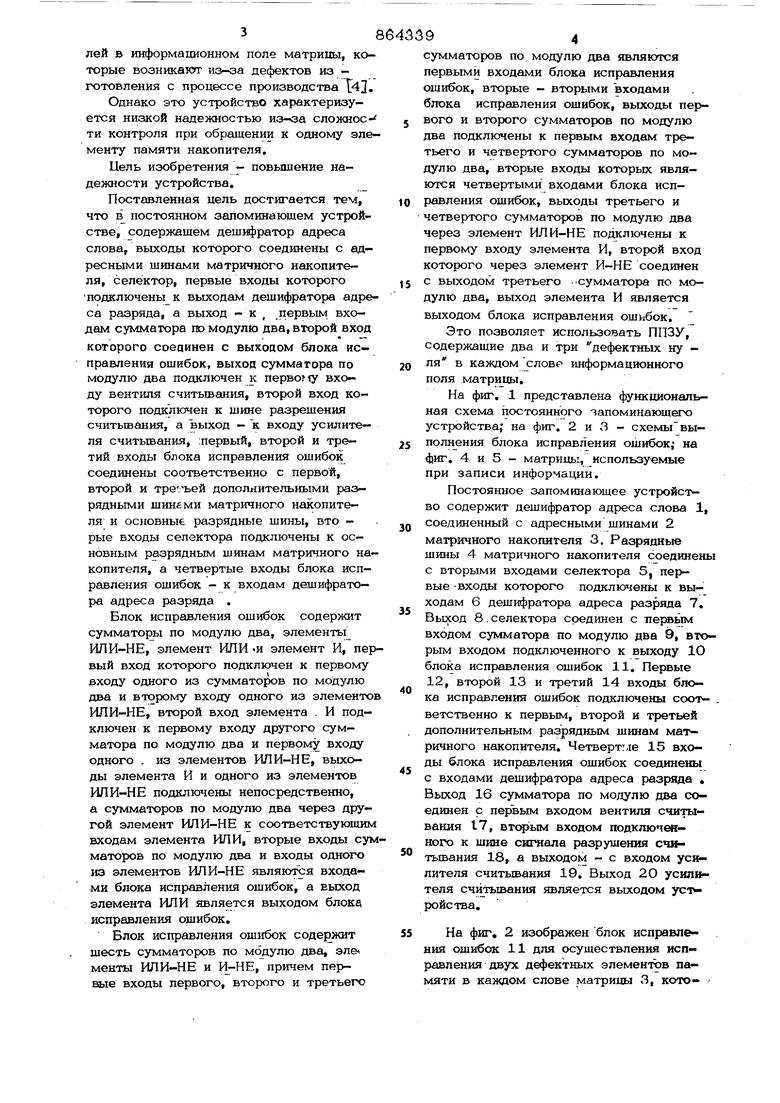

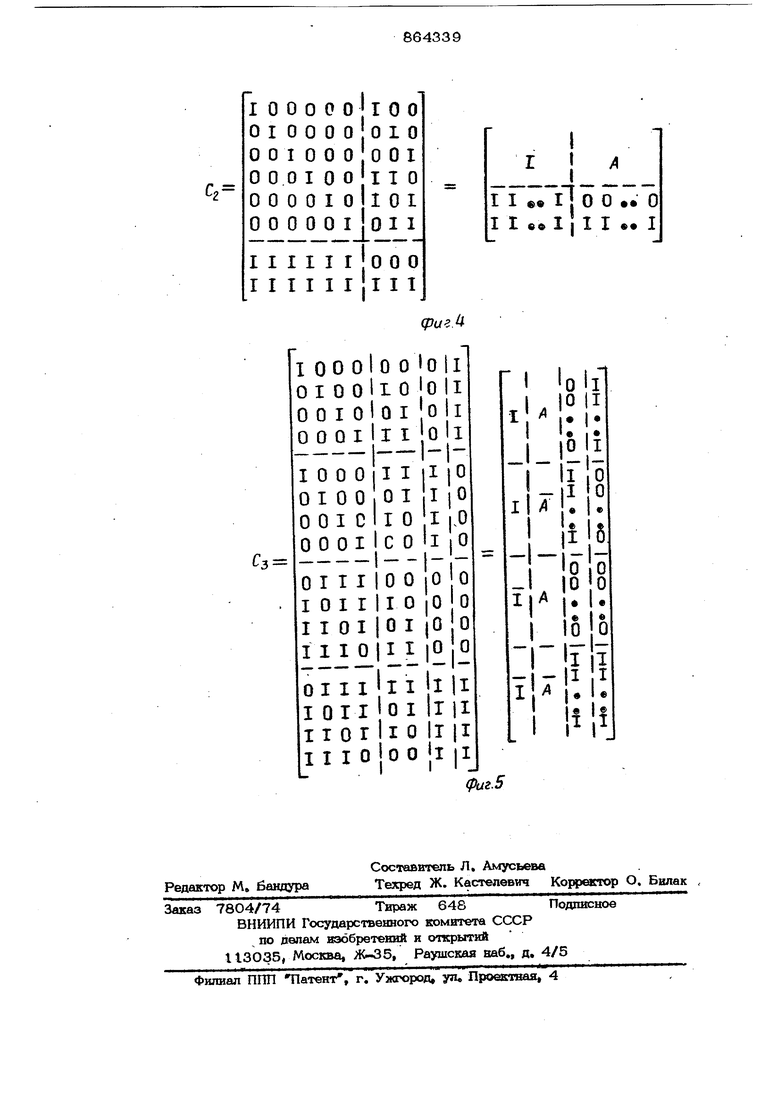

разрядным и1инам матри Ь{ого накопителя. Такое устройство позволяет исправлйть ошибки хранения информации при наличии лвух и трех дефектных ну3лей в информационном поле матрицы, которые возникактг из-за дефектов из гчэтовления с процессе производства Т43. Однако это устройство характеризуется низкой надежностью из-за сложноети контроля при обращении к одному эле менту памяти накопителя. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в посто5шном запоминающем устройстве, содержащем дешифратор адреса слова, выходы которого соединены с адресными шинами матричного накопителя, селектор, первые входы которого подключены к выходам дешифратора адре са разряда, а выход - к , первым входам сумматора по модулю два, второй вход которого соединен с выходом блока исправления ошибок, выход сумматора по модулю два подключен к первопу входу вентиля считьшания, второй вход которого подключен к шине разрешения считьшания, а выход - к входу усилителя считьтания, :первый, второй и третий входы блока исправления ошибок соединены соответственно с первой, второй и третьей дополнительными разрядными матричного накопителя и основные разрядные шины, вто рые входы селектора подключены к основным разрядным шинам матричного на копителя, а четвертые входы блока исправления ошибок - к входам дешифратора адреса разряща . Блок исправления ошибок содержит сумматорь по модулю два, элементы ИПИ-НЕ, элемент ИЛИ -и элемент И, пе вый вход которого подключен к первому входу одного из сумматоров по модулю два и второму входу одного из элементо ИЛИ-НЕ, второй вход элемента . И подключен к пертому входу другого сумматора по модулю два и первому входу одного . из элементов ИЛИ-НЕ, выходы элемента И и одного из элементов ИЛИ-НЕ подключены непосредственно, а сумматоров по модулю два через другой элемент ИЛИ-НЕ к соответствующим входам элемента ИЛИ, вторые входы су маторов по модулю два и входы одного из элементов ИЛИ-НЕ являются входами блока исправления ошибок, а выход элемента ИЛИ является выходом блока исправления ошибок. Блок исправления ошибок содержит шесть сумматоров по модулю два, элел менты ИЛИ-НЕ и , причем первые входы первого, второго и третьего 9 сумматоров по модулю два являются первыми входами блока исправления ошибок, вторые - вторыми входами блока исправления ошибок, выходы первого и второго сумматоров по модулю два подключены к первым входам третьего и четвертого сумматоров по модулю два, вторые входы которых являются четвертыми входами блока исправления ошибок, выходы третьего и четвертого сумматоров по модулю два через элемент ИЛИ-НЕ подключены к первому входу элемента И, второй вход которого через элемент И-НЕ соединен с выходом третьего -сумматора по модулю два, выход элемента И является выходом блока исправления ошухбок. Это позволяет использовать ППЗУ, содержащие два и три дефектных ну ля в каждом словр информационного поля матрицы. На фиг. 1 представлена функциональная схема постоянного запоминающего устройства; на фиг. 2 и 3 - схемы вы- блока исправления ошибок; на фиг. 4 и 5 - матрицы, используемые при записи информации. Постоянное запоминающее устройство содержит дешифратор адреса слова 1, соединенный с адресными шинами 2 матричного накопителя 3. Разрядные шины 4 матричного накопителя С5 единены с вторыми входами селектора 5, первые -входы которого подключены к выходам б дешифратора адреса разряда 7, Выход 8, селектора соединен с входом сумматора по модулю два 9, В1 орым входом подключенного к выходу 10 блока исправления ошибок 11. Первые 12, второй 13 и третий 14 входы блока исправления ошибок подключены соответственно к первым, второй и третьей дополнительным разрядным шинам матричного накопителя. Четвертме 15 входы блока исправления ошибок соединены с входами дешифратора адреса разряда . Выход 16 сумматора по модулю два соединен с первым входом вентиля считывания 17, входом подключенного к шине сигнала разрушения сч тьшания 18, а выходом - с входом усилителя считьтания 19. Выход 2О усилителя считьтания 5тляется выходом устройства. На фиг, 2 изображен блок исправления ошибок 11 для осуществления исправления двух дефектных элементов памяти в каждом слове матрицы 3, который содержит сумматоры по модулю два 21, первый 22 н второй 23 эпемон ты ИЛИ-НЕ, элементы И 24 и ИЛИ 25 Входы первого элемента , входы элемента И и первые входы сумматоров jHo модулю два соединены с первыми входами блока исправления ошибок Вторые входы сумматоров по модулю два соединены с четвертыми входами блока исправления ошибок, а выходы- с входами второго элемента ИЛИ-НЕ. Выходы першрго и второго элементов ИЛИ-НЕ, элемента И соединены с входами элемента ИЛИ . Выход элемента ИЛИ $шляется выходом блока испр) ошибок. ycTixjucTBO в режиме исправления даух дефектных элементов памяти в каждом слове матрицы работает следующим образом. При записи информации (при изготовлешш) в основные разряды и в первые дополнительные разряды каждого слова матрицы заносится информация для хранения следующим образом. В матрицу записьшается слово Ч и + С (U, dl ), где и (U,VJ,j... ,иц,0,...,0) слово длины; и - первые k U -у символов представляют собой программируемую в матрицу информагшю U, а последние г - символов - нули г - 2)-, С- ( и , ci ) - одна из строк матрицы Cij На фиг. 4 показана матрица 6; ( 3; « 9 и общий вид матрицы urj , где 1 - единичная матрина J А- матрица, содержащая двоичные числа, за исключением чисел ОО.,.0 и 11...1, . Матрица Сг обладает тем сво ством , что в подматрице С J из любых двух ее столбцов содержится каждая строка из 2 различных строк длйнь V 2 { с, - кратность дефекта), т.е, всегда содержатся комбинации вида : .0 О, О 1, 1. О, 1 1 . Нужная строка С (U , d ) определяет ся следующим образом. Составляется подматрица С.,} ( с раз мером rv х2 ) матрицы ч t -и стол бец матрицы С J . является столбцом СлС номером, равным номеру д -и слева де фектной 1ЮЗИЦИИ. .лределяется U - м рица - строка с двумя элементами элемент соответствует i - слева де- фектной позиции и равен нулю, если та 96 позиция вин состояние дефектного разряда э| совпадают и равен единице в противном случае. Затем иаходит ся номер строки подматриНы C.J (каяример, при подсчете строк сверху), где UJ - матрица строка покрьшает (совпадает) одну любую из строк подматрицы tj. Номер этой строки в подматрице С соответствует номеру строки в мат- рице Сл, которая и задает функцию согласования записываемой в матрицу информации с данными дефектами. Пример. Пусть в строке (слове) матрицы элементов памяти имеется один неисправнь й элемент в основных разрядах (It - разрядах), который находится в нулевом состоянии, а все остальные разряды в единичном состоянии. Пусть неисправным разрядом будет второй слева разряд, и его состояние не совпадает с прог)раммируемой в элемент информацией, т.е, мы никаким образом в этот разряд не можем занести единичный символ. Тогда Видно g что о) покрывает (совпадает) С. во 2( 7в 8 строках. Любую из этих строк в Сд можно испЪльзовать в качестве функшш С ( U , dl ) согласования программируемой в информации с состоянием дефекта. При этом в пэрвых разрядах слова храниться код адреса строки Сд. П р и м е р 2 . Пусть в строке (слове) матрииы элементов памяти имеется два неисправных элемента (находятся в нулевом состоянии), один из которых находятся в разрядах 4 (I разряд), а второй - в ледаых разрядах 12(1 дополнительном разряде). Пусть программируемая информапзая в матрицу имеет вид U 1 О 1 О 11. Тогда 0«(1О011 000), 7 Отсюда видно, что uj покрьтает (сов падает ) С J в 7 строке С.| и С. В матрицу программируется слово Ч( 101011 ООО) 4(111111 000)О10 10О ООО, т. программируемая информация стала совпадать с состо5шием дефектных разрядов, а tor - дополнителыа 1х разрядах хранится код покрьшающей строки из С. В режиме считьюания в соответствии с кодом адреса опрашиваемого разряда происходит возбуждение шин 2 и 6 дешифраторов 1 и 7. При этом на выходе 8 селектора 5 вьщеляется информация хранимая в этом разряде матричного накопителя 3, а на выходе 10 блока исправления ошибок 11 - информация, соответствующая данному разряду из строки матрицы CQ , определяемой по коду адреса, хранимому в - разрядах 12, опрашиваемого слова. Тогда , разрядах 12 записаны числа О0..0,1 1, то на выходе 10 элемента ИЛИ 25 блока исправления ошибок 11 всегда будет единичный сигнал , так как эти комбинации всегда выделяются или элементом ИЛИ-НЕ 22 или элементом И 24 независимо от 01 рашиваемого разряда, В этом случае, сигналы, сни у1аемые с выхода 8 селек.Х1ра 5, будут инвертироваться на противоположные на сумматоре по модулю два 9 и через вентиль счи тьюания 17, усилитель считывания 19 поступают на вь1ход 20 устройства. Сиг налы на выходе 2 О устройства будут считьюаться правильными, так как инвертирование производилось дважды : при записи (при изготовлении) и при счи тьшании (при эксплуатац: и). Для исправных элементов памяти эти инвертирования не изменяют правильного выходного сигнала. Для дефектных элементов памяти инвертирование информации при записи позволяет согласовать состояние дефектного разряда с программируемой информацией, а инвертирование при считьшании восстановить правильно сигналы с дефектных позиций. ( Для примера 2, считьшаемое слово на выходе 8 селектора 5 mvieeT вид Ч О1010О ООО, слово на выходе 10 блока исправления ошибок 11 0(0, d,) 111 111 ООО, а на выходе 2О устройства и 1О1О11, т е. соответствует информа101И, подлежащей хранению). Если в разрядах 12 записаны числа отличные от ОО,.0 , 11..1, то инвертированию при считывании (как и при записи) будет подвергаться только один 39 разряд, код адреса которого совпадает с кодом адреса , хранимым в разрядах 12 (проверка на совпадение осуществляется на сумматорах по модулю два 21 и эле- менте ИЛИ -Ht 23 блока исправления ошибок 11). На фиг. 3 изображен блок исправления ошибок для осуществления исправления трех дефектных элементов памяти в каждом слове накопителя 3, который содержит первые 26, вторые 27, третий 28 и четвертый 29 сумматоры по модулю два, элементы ИЛИ-НЕ ЗО и И-НЕ 31. Первые и вторые входы первых сумматоров по модулю два, соединены соответственно с первыми и вторым входами блока исправления ошибок. Выходь. первых сумматоров по модулю два соединены с первыми входами вторых сумматоров по модулю два, втопыми входами, подключенными к четвертым входам исправления ошибок. Выходы вторых сумматоров по модулю два соедшены с входами элемента ИЛИ-НЕ, выход которого подключен к первому входу четвертого сумматора по модулю два. Второй вход четвертого сумматора по модулю два соединен через элемент И-НЕ с выходом. третьего сумматора по модулю два. Входы третьего сумматора по модулю два соединены с вторым и третьим входами блока исправления ошибок. Выход четвертого сумматора по модулю два 5шляется выходом блока исправления ошибок. Устройство в режиме исправления трех дефектных элементов памяти в каждом слове матрицы работает следующим образом. При записи информации (при изготовлении) в разряды 4 и в разряды 12 каждого слова матрицы заносится информация, как и при исправлении двух дефектных элементов памяти. Однако для нахождения функции согласования CTCU, d ) используется матрица Cj . На фиг. 5 показана матрица Сгп,, , . и 8 и общий вид матрицы С , где 1 - единичная матрица I - матрица инверсия к единичной матрице Ij А -матрица размфом { -2)х -k , все строки которой различны, И -матрица инверсная к матрице А . Матрица С обладает, тем свойсгвом, что в подматрице С из любых трех ее столбцов содержится каждая строка из 2 различных строк дли1НЫ 3 ( q, - кратность дефекта), т.е. 9 всегда содержатся котибипации вида : ;оо, 001, 010, 100, но, loi, он. 111. Пля маркировки строк матрицы Crj в бираются у 2 разрядные двоич ные числа, которые являются дополнительными разрядами. Работа устройства в режиме считььвания при коррекции трех дефектных элементов памяти С слова, отличается от описанной тем, что во втором допол нительном разряде 13 матрицы 3 хранится нулевой или V единичный символ, благодаря чему на выходе первых сумматоров по модулю два 26 формируются числа из матрицы А . Тогда, в том случае, если символы, хранимые во втором 13 и третьем 14 дополнительных разрядах не совпадают, то на выходе элемента И-НЕ 31 будет нулевой , а на выходе элемента ИЛ И-НЕ 30 (а следовательно, и на выходе четвертого сумматора 29) буду формироваться сигналы, соответствующие единичной матрице. В противном случае, т.е. когда символы хранимые во втором 13 и третьем 14 дополнительных разрядах совпадают на выходе элемента И-НЕ 31 будет единичный сигнал и на выходе четвертого сумматора 29 будут формироваться сигналы, соот: ветс-геукацие инверсии единичной матрицы. При этом аналогичным образом, как и при исправлении двух дефектных элементов памяти в слово непосредственная проверка показывает сфавильность хранения информации в устройстве. Таким образом, данное устройство вьшолняет те же функции, что и известное, но требует для своей реализации меньшего числа дополнительных разрядов, а также значительно упрощаются схемы контроля (не требуется сложных дешифраторов на -k - выходов в бл ках исправления ошибок, отсутствуют k - сумматорог по модулю два в самом устройстве ), в результате чего повышается надежность устройства. I Формула изобретения i. Постоянное запоминакниее устройство, содержащее - дешифратор адреса сло ва, выходы которого соединены с адрес ными шинами матричного накопителя, се лектор, первые входы которого подключены к выходам дешифрато{эа адреса раз рада, а выход - к первым входам сумм 9 тора по модулю два, второй вход которого соединен с выходом блока исправления ошибок, выход сумматора по модулю два подключён к первому входу вентиля считывания, второй вход которого подключен к шине разрешения считывания, а выход - к входу усилителя считывания , первый, второй и третий входы блока исправления ошибок соединены соответствеино с первой, второй и третьей дополнительными разрядными шинами матрччнсго накопителя и основные разрядные шины, отличающееся тем, что, с целью повышения надежности устройства, вторые входы селектора подключены к осчовным разрядным шинам матричного накопителя, а четвертые входы блока исправления ошибок - к входам дешхфратора адреса разряда, 2.Устройство по п, 1, о т л и ч аю щ о е с я тем, что блок исправления ошибок содержит сумматоры по модулю два. элементы HJTli-HF, элемент ИЛИ и элетлент И, первый вход которого подключен к первому входу одного из сумматоров по модулю два и второму входу одного из элементов ИЛ И-НЕ, второй вход элемента И подключен к первому входу другого сумматора по модулю два и первому входу одного из элементов И Л И-НЕ, выходы элемента И и одного из элементов ИЛИНЕ подключены непосредственно, а сумматоров по модулю два через другой элемент ИЛ И-НЕ к соответствующим входам элемента ИЛИ, вторые входы сумматоров по модулю два и входы одного из элементов ИЛИ-НЕ являются входами блока исправления ошибок, а выход элемента ИЛИ является выходом; блока исправления ошибок. 3.Устройство по п. J., о т л и ч аю ш е е с я тем, что блок исправления ошибок содержит шесть сумматоров по модулю два, элементы ИЛИ-НЕ я И-НЕ, причем первые входы первого и второго и третьего сумматоров по модулю два являются первыми входами блока исправления ошибок, вторые - вторыми входами блока исправления ошибок, выходы лорвого и второго сумматоров модулю два подключены к первым ахо- дам третьего и четвертого сумматоров по модулю два, вторые входы которыу являются четвертьтми входами блока исправлений ошибок, выходы третьего ь четвертого сумьлаторов по модулю два через элемент ИЛИ-НЕ подключены к

11

первому входу элемента И, второй вход которого через элемент И-НЕ соединен с выходом третьего сумматора по модулю два, выход 9л« 1ента И является выходом блока исправления ошибок.

Источники информации, принятые во внимание при экспертизе

(риг.г

6433912

.. -Электронная техника, 1975, NO 4, с. 65-687

5 на биполярных транзисторньгх структурах. М., Советск9е радио, 1979, с. 246257, рис. 8.2

10 кл. Q11 С 17/ОО, (5 11 С 29/ОО, 13.10.75 (прототип).

фигЪ

Авторы

Даты

1981-09-15—Публикация

1979-05-21—Подача