Изобретение относится к вычислительной технике и может быть использовано в электронной промышленности при изготовлении больших интегральных схем программируемых постоянных запоминающих устройств (ППЗУ).

Известны ППЗУ, содержащие матрипу элементов памяти, дещифраторы слова и разряда, селектор, вентили считывания, усилители считывания. В таких устройствах элементы памяти матрицы соединены с разрядными шинами плавкими перемычками или р-п переходами, которыми разрушаются при записи информации в соответствии с кодом, подлежащим хранению в ППЗУ. До занесения программируемого кода в матрицу в информационном поле содержатся только единицы 1 и 2.

Работоспособность ППЗУ нарушается при наличии «дефектного нуля в информационном поле матрицы, когда никаким способом не удается записать на место дефектного элемента единицу.

Наиболее близким техническим решением к изобретению является постоянное запоминающее устройство, содержащее дешифратор адреса слова, соединенный с адресными шинами матрицы элементов памяти, селектор, первые входы которого соединены с выходами дешифратора адреса разряда, а выходы - с первыми входами первых сумматоров по модулю два, выходы , которых подключены к первым входам вентилей считывания, вторыми входами соединенных с шиной сигнала разрешения считывания, а выходом - с входами усилителей считывания 3.

Однако такое устройство приводит к ш ошибкам хранения информации при наличии двух и трех «дефектных нулей в информационном поле матрицы, которые возникают из-за дефектов изготовления в процессе производства. Поэтому при производстве такие постоянные запоминающие устройства отбраковываются.

Цель изобретения - повышение надех ности устройства.

Поставленная цель достигается тем, что в него введены блок .исправления ошибок и 20 вторые сумматоры по модулю два, выходы вторых сумматоров по модулю два соединены с вторыми входами селектора, первые входы - с основными разрядными шинами матрицы элементов памяти, а вторые входы - с первыми выходами блока исправления ошибок, второй выход которого соединен с вторыми входами первых сумматоров по модулю два, первые и второй входы блока исправления ошибок подключены соответственно к первым и второй дополнительным разрядным шинам матрицы элементов памяти, а также тем, что блок исправления ошибок содержит элемент ИЛИ и дешифратор, причем входы элемента ИЛИ и дешифратора соединены с первыми входами блок, а выходы дешифратора и элемента ИЛИ соединены соответственно с первыми и .вторым выходами блока, а также тем, что блок исправления ошибок содержит первый и второй дешифраторы, пер,вые и второй сумматоры по модулю два, элемент ИЛИ-НЕ, первый и второй элементы ИЛИ, элемент И, причем входы первого дешифратора соединены с первыми входами блока, элементом ИЛИ-НЕ и первыми входами первых сумматоров по модулю два, вторые входы которых соединены с выходом элемента И, а выходы - с входами второго дешифратора, выходы которого являются первыми выходами блока, выходы первого дешифратора соединенны с входами первого элемента ИЛИ, выход которого подключен к первому входу второго сумматора по модулю два и первому входу элемента И, вторым входом соединенного е вторым, входом блока и первым входом Btoporo элемента ИЛИ, вторым входом подключенного к выходу элемента ИЛИ-НЕ, а выходом - к второму входу второго сумматора по модулю два, выход которого является вторым выходом блока.

Это позволяет использовать ППЗУ, содержащие три «дефектных нуля в каждом слове информационного поля матрицы.

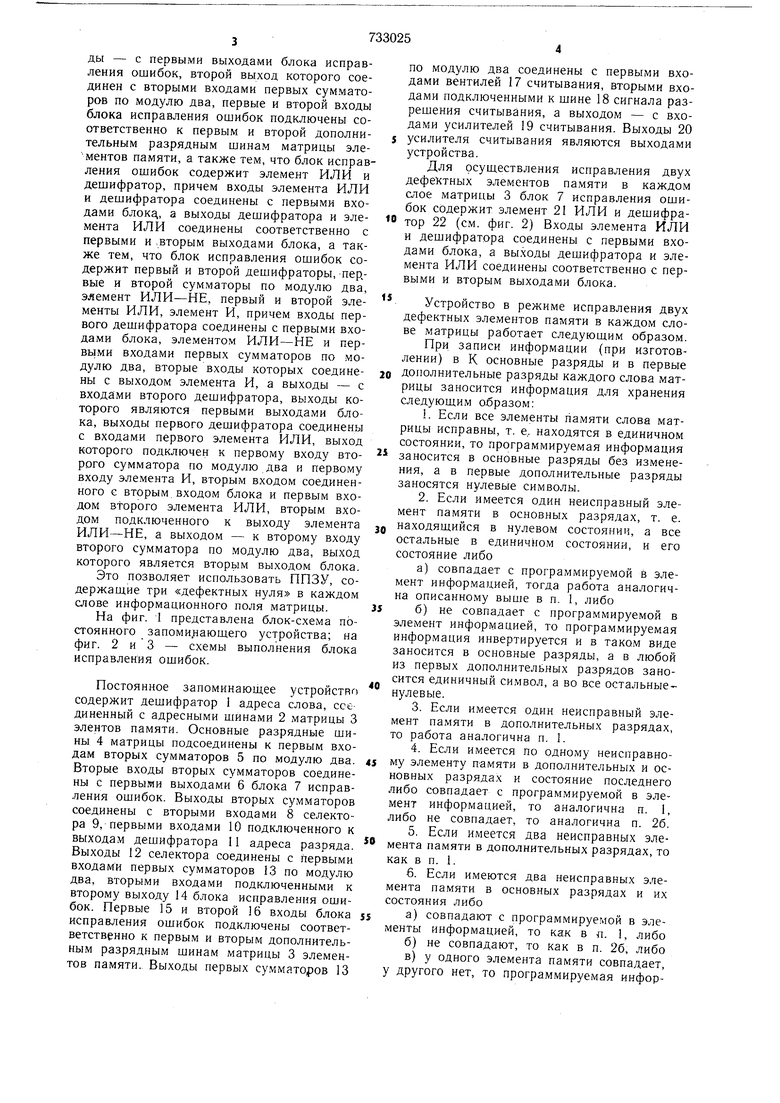

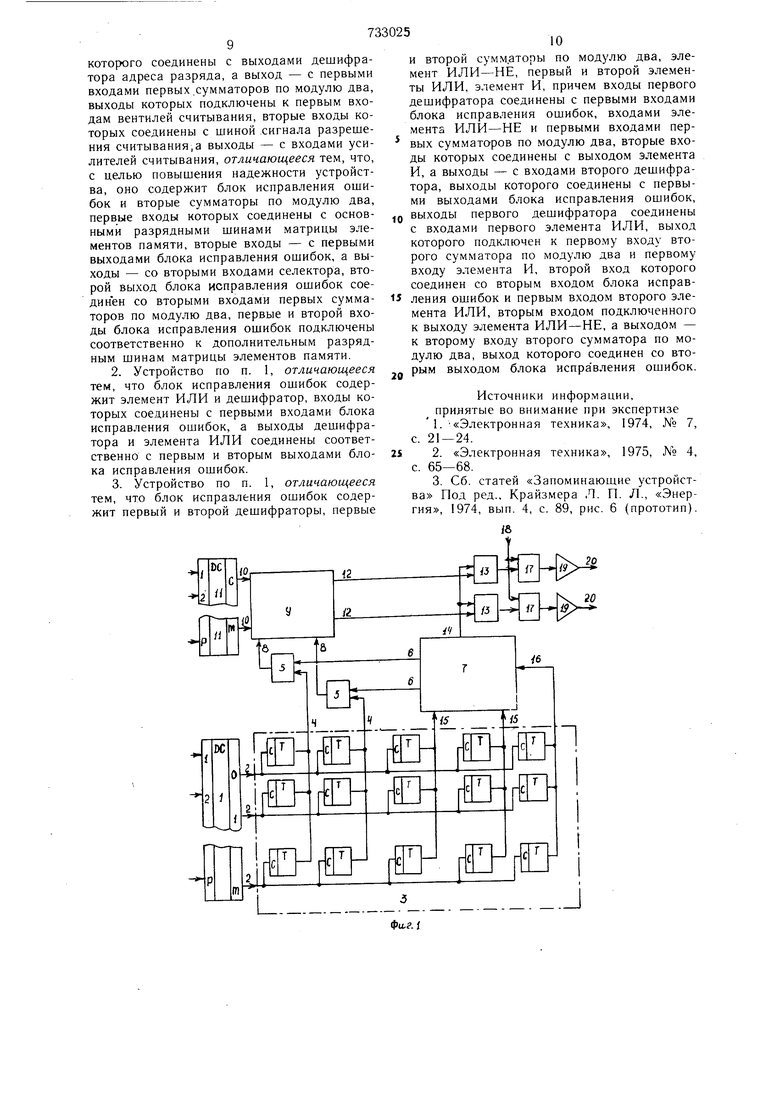

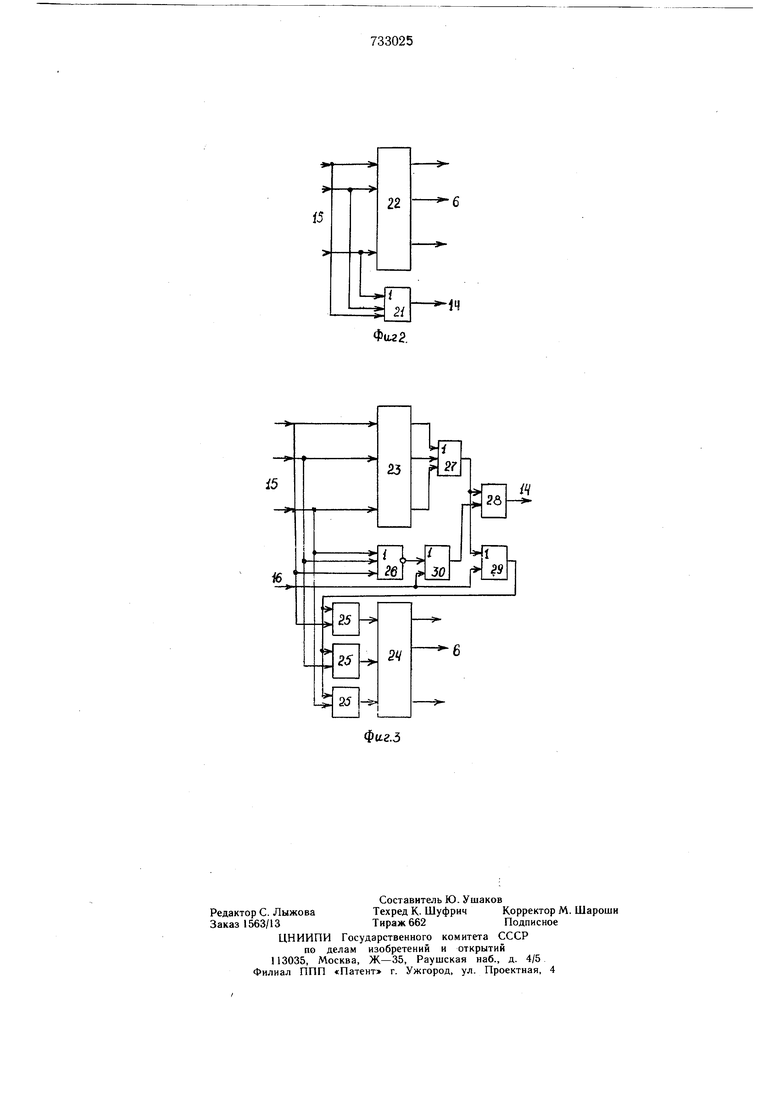

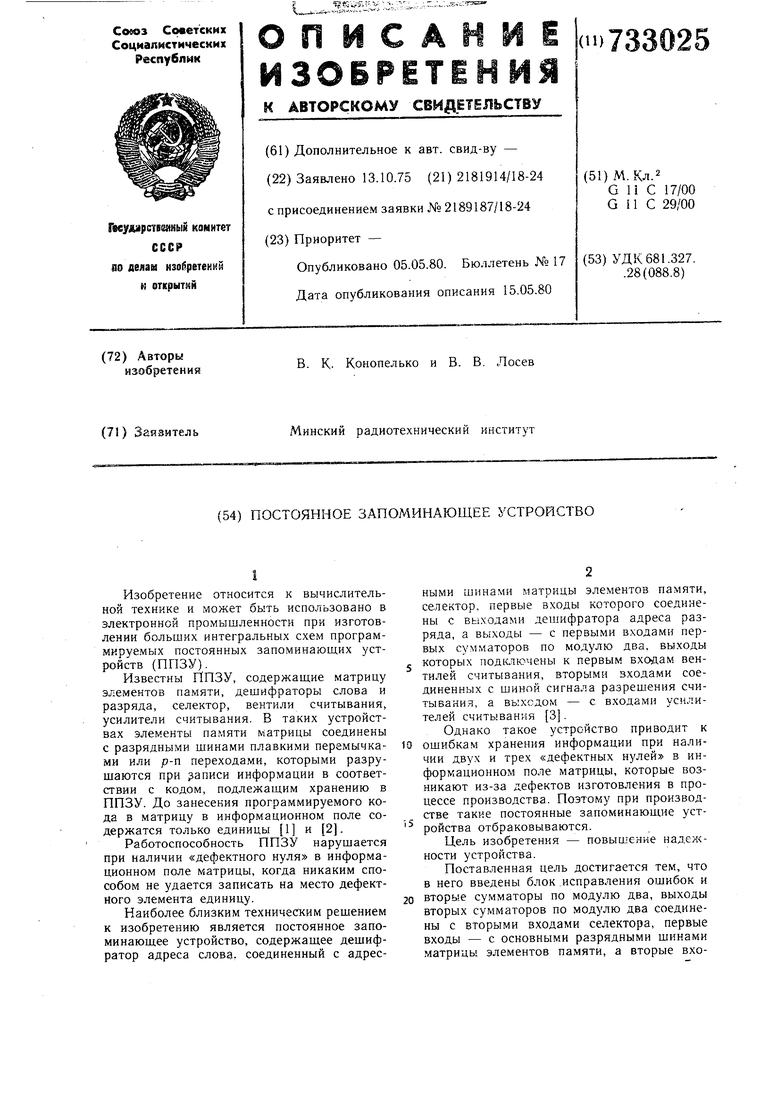

На фиг. 1 представлена блок-схема постоянного запоми.нающего устройства; на фиг. 2 и 3 - схемы выполнения блока исправления ошибок.

Постоянное запоминающее устройство содержит дешифратор 1 адреса слова, соединенный с адресными шинами 2 матрицы 3 элентов памяти. Основные разрядные шины 4 матрицы подсоединены к первым входам вторых сумматоров 5 по модулю два. Вторые входы вторых сумматоров соединены с первыми выходами 6 блока 7 исправления ошибок. Выходы вторых сумматоров соединены с вторыми входами 8 селектора 9, первыми входами 10 подключенного к выходам дешифратора 11 адреса разряда. Выходы 12 селектора соединены с первыми входами первых сумматоров 13 по модулю два, вторыми входами подключенными к второму выходу 14 блока исправления ошибок. Первые 15 и второй 16 входы блока исправления ошибок подключены соответветстврнно к первым и вторым дополнительным разрядным шинам матрицы 3 элементов памяти.. Выходы первых сумматоров 13

по модулю два соединены с первыми входами вентилей 17 считывания, вторыми входами подключенными к шине 18 сигнала разрешения считывания, а выходом - с входами усилителей 19 считывания. Выходы 20

5 усилителя считывания являются выходами устройства.

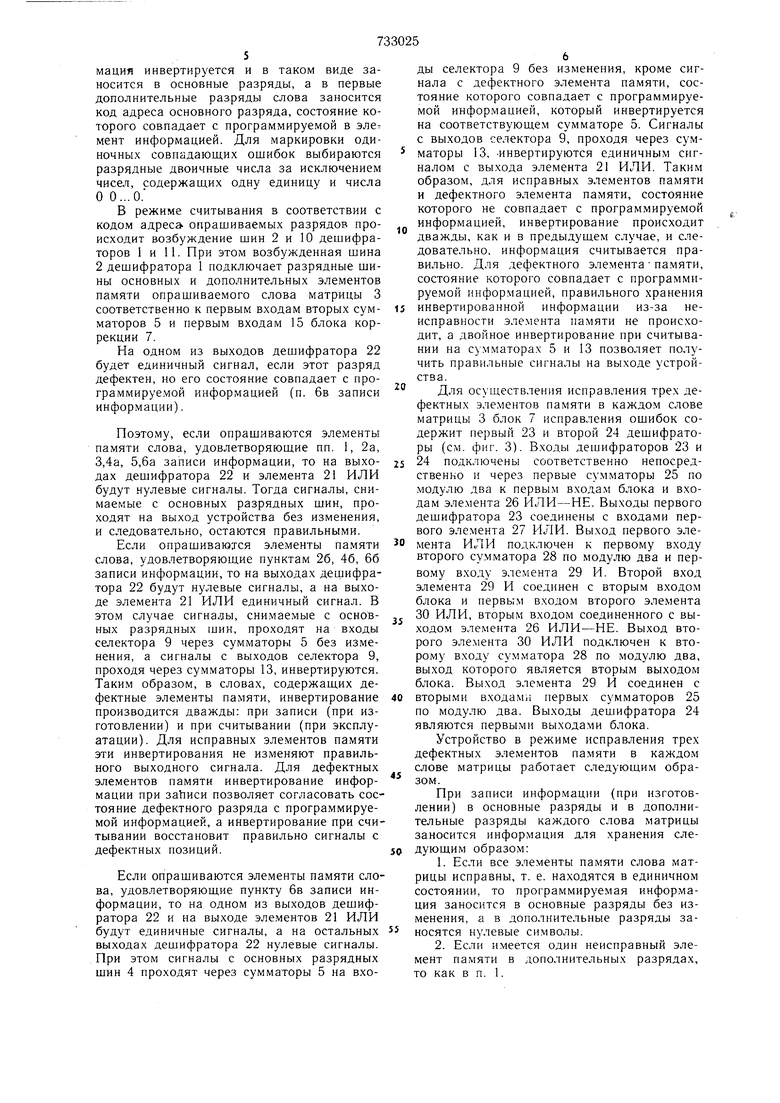

Для осуществления исправления двух дефектных элементов памяти в каждом слое матрицы 3 блок 7 исправления ошибок содержит элемент 2 ИЛИ и дешифратор 22 (см. фиг. 2) Входы элемента ИЛИ и дешифратора соединены с первыми входами блока, а выходы дешифратора и элемента ИЛИ соединены соответственно с первыми и вторым выходами блока.

Устройство в режиме исправления двух дефектных элементов памяти в каждом слове матрицы работает следуюшим образом. При записи информации (при изготовлении) в К основные разряды и в первые

20 дополнительные разряды каждого слова матрицы заносится информация для хранения следующим ойразом:

1.Если все элементы памяти слова матрицы исправны, т. е, находятся в единичном состоянии, то программируемая информация

заносится в основные разряды без изменения, а в первые дополнительные разряды заносятся нулевые символы.

2.Если имеется один неисправный элемент памяти в основных разрядах, т. е.

j находящийся в нулевом состоянии, а все остальные в единичном состоянии, и его состояние либо

а) совпадает с программируемой в элемент информацией, тогда работа аналогична описанному выше в п. 1, либо

S б) не совпадает с программируемой в элемент информацией, то программируемая информация инвертируется и в таком виде заносится в основные разряды, а в любой из первых дополнительных разрядов заносится единичный символ, а во все остальныенулевые.

3.Если имеется один неисправный элемент памяти в дополнительных разрядах, то работа аналогична п. 1.

4.Если имеется по одному неисправноS му элементу п-амяти в дополнительных и основных разрядах и состояние последнего либо совпадает с програм.мируемой в элемент информацией, то аналогична п. 1, либо не совпадает, то аналогична п. 26.

5.Если имеется два неисправных элемента памяти в дополнительных разрядах, то как в п. 1.

6.Если имеются два неисправных элемента памяти в основных разрядах и их состояния либо

а) совпадают с программируемой в элементы информацией, то как в л. 1, либо

б)не совпадают, то как в п. 26, либо

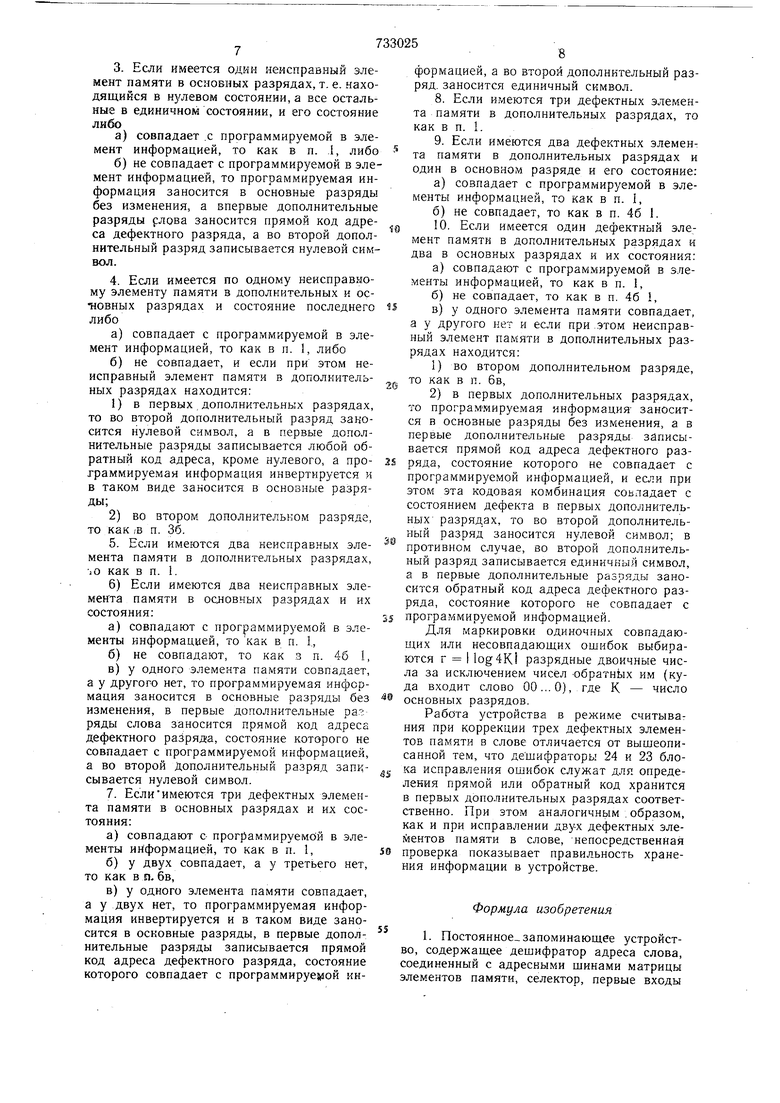

в)у одного элемента памяти совпадает, у другого нет, то программируемая информация инвертируется и в таком виде заносится в основные разряды, а в первые дополнительные разряды слова заносится код адреса основного разряда, состояние которого совпадает с программируемой в элемент информацией. Для маркировки одиночных совпадающих ошибок выбираются разрядные двоичные числа за исключением чисел, содержащих одну единицу и числа О 0...0. В режиме считывания в соответствии с кодом адреса- опращиваемых разрядов происходит возбуждение шин 2 и 10 дешифраторов 1 и 11. При этом возбужденная шина 2 дешифратора 1 подключает разрядные шины основных и дополнительных элементов памяти опрашиваемого слова матрицы 3 соответственно к первым входам вторых сумматоров 5 и первым входам 15 блока коррекции 7. На одном из выходов дешифратора 22 будет единичный сигнал, если этот разряд дефектен, но его состояние совпадает с программируемой информацией (п. 6в записи информации). Поэтому, если опрашиваются элементы памяти слова, удовлетворяющие пп. 1, 2а, 3,4а, 5,6а записи информации, то на выходах дешифратора 22 и элемента 21 ИЛИ будут нулевые сигналы. Тогда сигналы, снимаемые с основных разрядных шин, проходят на выход устройства без изменения, и следовательно, остаются правильными. Если опрашиваются элементы памяти слова, удовлетворяющие пунктам 26, 46, 66 записи информации, то на выходах дещифратора 22 будут нулевые сигналы, а на выходе элемента 21 ИЛИ единичный сигнал. В этом случае сигналы, снимаемые с основных разрядных шин, проходят на входы селектора 9 через сумматоры 5 без изменения, а сигналы с выходов селектора 9, проходя через сумматоры 13, инвертируются. Таким образом, в словах, содержащих дефектные элементы памяти, инвертирование производится дважды: при записи (при изготовлении) и при считывании (при эксплуатации). Для исправных элементов памяти эти инвертирования не изменяют правильного выходного сигнала. Для дефектных элементов памяти инвертирование информации при позволяет согласовать состояние дефектного разряда с программируемой информацией, а инвертирование при считывании восстановит правильно сигналы с дефектных позиций. Если опрашиваются элементы памяти слова, удовлетворяющие пункту бв записи информации, то на одном из выходов дешифратора 22 и на выходе элементов 21 ИЛИ будут единичные сигналы, а на остальных выходах дешифратора 22 нулевые сигналы. При этом сигналы с основных разрядных шин 4 проходят через сумматоры 5 на входы селектора 9 без изменения, кроме сигнала с дефектного элемента памяти, состояние которого совпадает с программируемой информацией, который инвертируется на соответствующем сумматоре 5. Сигналы с выходов селектора 9, проходя через сумматоры 13, -инвертируются единичным сигналом с выхода элемента 21 ИЛИ. Таким образом, для исправных элементов памяти и дефектного элемента памяти, состояние которого не совпадает с программируемой информацией, инвертирование происходит дважды, как и в предыдущем случае, и следовательно, информация считывается правильно. Для дефектного элемента памяти, состояние которого совпадает с программируемой информацией, правильного хранения инвертированной информации из-за неисправности элемента памяти не происходит, а двойное инвертирование при считывании на сумматорах 5 и 13 позволяет получить правильные сигналы на выходе устройства. Для осуществления исправления трех дефектных элементов памяти в каждом слове матрицы 3 блок 7 исправления ощибок содержит первый 23 и второй 24 дещифраторы (см. фиг. 3). Входы дешифраторов 23 и 24 подключены соответственно непосредственно и через первые сумматоры 25 по модулю два к первым входам блока и входам элемента 26 ИЛИ-НЕ. Выходы первого дешифратора 23 соединены с входами первого элемента 27 ИЛИ. Выход первого элемента ИЛИ подключен к первому входу второго сумматора 28 по модулю два и первому входу элемента 29 И. Второй вход элемента 29 И соединен с вторым входом блока и первым входо.м второго элемента 30 ИЛИ, вторым входом соединенного с выходом элемента 26 ИЛИ-НЕ. Выход второго элемента 30 ИЛИ подключен к второму входу сумматора 28 по модулю два, выход которого является вторым выходом блока. Выход элемента 29 И соединен с вторыми входами первых сумматоров 25 по модулю два. Выходы дешифратора 24 являются первыми выходами блока. Устройство в режиме исправления трех дефектных элементов памяти в каждом слове матрицы работает следующим образом. При записи информации (при изготовлении) в основные разряды и в дополнительные разряды каждого слова матрицы заносится информация для хранения следующим образом: 1. Если все элементы памяти слова матрицы исправны, т. е. находятся в единичном состоянии, то программируемая информация заносится в основные разряды без изменения, а в дополнительные разряды заносятся нулевые символы. 2. Если имеется один неисправный элемент памяти в дополнительных разрядах, то как в п. 1. 3.Если имеется один неисправный элемент памяти в основных разрядах, т. е. находящийся в нулевом состоянии, а все остальные в единичном состоянии, и его состояние либо а)совпадает .с программируемой в элемент информацией, то как в п. 1, либо б)не совпадает с программируемой в элемент информацией, то программируемая информация заносится в основные разряды без изменения, а впервые дополнительные разряды рлова заносится прямой код адреса дефектного разряда, а во второй дополнительный разряд записывается нулевой символ. 4.Если имеется по одному неисправному элементу памяти в дополнительных и основных разрядах и состояние последнего либо а)совпадает с программируемой в элемент информацией, то как в п. , либо б)не совпадает, и если при этом неисправный элемент памяти в дополнительных разрядах находится: 1)в первых , дополнительных разрядах, то во второй дополнительный разряд заносится нулевой символ, а в первые дополнительные разряды записывается любой обратный код адреса, кроме нулевого, а программируемая информация инвертируется и в таком виде заносится в основные разряды;2)во втором дополнительном разряде, то как (Б п. 36. 5.Если имеются два неисправных элемента памяти в дополнительных разрядах, дО как в п. 1. 6) Если имеются два неисправных элемента памяти в основных разрядах и их состояния: а)совпадают с программируемой в элементы информацией, то как в п. 1., б)не совпадают, то как з п. 45 1, в)у одного элемента памяти совпадает, а у другого нет, то программируемая информация заносится в основные разряды без изменения, в первые дополнительные ра. ряды слова заносится прямой код адреса дефектного разряда, состояние которого не совпадает с программируемой информацией, а во второй Дополнительный разряд записывается нулевой символ. 7. Еслиимеются три дефектных элемента памяти в основных разрядах и их состояния:а)совпадают о программируемой в элементы информацией, то как в п. 1, б)у двух совпадает, а у третьего нет, то как в п. 6в, в)у одного элемента памяти совпадает, а у двух нет, то программируемая информация инвертируется и в таком виде заносится в основные разряды, в первые дополнительные разряды записывается прямой код адреса дефектного разряда, состояние которого совпадает с программируе юй информацией, а во второй дополнительный разряд, заносится единичный символ. 8.Если имеются три дефектных элемента памяти в дополнительных разрядах, то как в п. 1. 9.Если имеются два дефектных элемента памяти в дополнительных разрядах и один в основном разряде и его состояние: а)совпадает с программируемой в элементы информацией, то как в п. 1, б)не совпадает, то как в п. 46 1. 10.Если имеется один дефектный элемент памяти в дополнительных разрядах и два в основных разрядах и их состояния: а)совпадают с программируемой в элементы информацией, то как в п. 1, б)не совпадает, то как в п. 46 1, в)у одного элемента памяти совпадает, а у другого нет и если при .этом неисправный элемент памяти в дополнительных разрядах находится: 1)во втором дополнительном разряде, то как в п. 6в, 2)в первых дополнительных разрядах, то программируемая информация- заносится в основные разряды без изменения, а в первые дополнительные разряды записывается прямой код адреса дефектного разряда, состояние которого не совпадает с программируемой информацией, и если при этом эта кодовая комбинация совладает с состоянием дефекта в первых дополнительных разрядах, то во второй дополнительный разряд заносится нулевой символ; в противном случае, во второй дополнительный разряд записывается единичный символ, а в первые дополнительные разряды заносится обратный код адреса дефектного разряда, состояние которого не совпадает с программируемой информацией. Для маркировки одиночных совпадающих или несовпадающих ошибок выбираются г I log4Kl разрядные двоичные числа за исключением чисел -обратных им (куда входит слово 00...0), где К - число основных разрядов. Работа устройства в режиме считывания при коррекции трех дефектных элементов памяти в слове отличается от вышеописанной тем, что дешифраторы 24 и 23 блока исправления ошибок служат для определения прямой или обратный код хранится в первых дополнительных разрядах соответственно. При этом аналогичным , образом, как и при исправлении двух дефектных элементов памяти в слове, непосредственная проверка показывает правильность хранения информации в устройстве. Формула изобретения 1. Постоянное запоминающее устройство, содержащее дешифратор адреса слова, соединенный с адресными шинами матрицы лементов памяти, селектор, первые входы которого соединены с выходами дешифратора адреса разряда, а выход - с первыми входами первых,сумматоров по модулю два, выходы которых подключены к первым входам вентилей считывания, вторые входы которых соединены с шиной сигнала разрешения считывания,а выходы - с входами усилителей считывания, отличающееся тем, что, с целью повышения надежности устройства, оно содержит блок исправления ошибок и вторые сумматоры по модулю два. первые входы которых соединены с основными разрядными шинами матрицы элеMKTMVT ПЯ ПапииШ/ИЛ ТКГЛСЮИЯН XjCO-yrMimi -iTTo. ментов памяти, вторые входы - с первыми выходами блока исправления ошибок, а выходы - со вторыми входами селектора, второй выход блока исправления ошибок сое. динен со вторыми входами первых сумматоров по модулю два, первые и второй входы блока исправления ошибок подключены соответственно к дополнительным разрядным шинам матрицы элементов памяти. 2.Устройство по п. 1, отличающееся тем, что блок исправления ошибок содержит элемент ИЛИ и дешифратор, входы которых соединены с первыми входами блока исправления ошибок, а выходы дешифратора и элемента ИЛИ соединены соответственно с первым и вторым выходами блока исправления ошибок. 3.Устройство по п. 1, отличающееся тем, что блок исправления ошибок содержит первый и второй дешифраторы, первые и второй сумматоры по модулю два, элемент ИЛИ-НЕ, первый и второй элементы ИЛИ, элемент И, причем входы первого дешифратора соединены с первыми входами блока исправления ошибок, входами элемента ИЛИ-НЕ и первыми входами первых сумматоров по модулю два, вторые входы которых соединены с выходом элемента И, а выходы - с входами второго дешифратора, выходы которого соединены с первыми выходами блока исправления ошибок. выходы первого дешифратора соединены , , , , с входами первого элемента ИЛИ, выход которого подключен к первому входу второго сумматора по модулю два и первому входу элемента И, второй вход которого соединен со вторым входом блока исправ - iiit ii v,j ijujjjDiivi Ui.iUrLd И ЛШаЬления ошибок и первым входом второго элемента ИЛИ, вторым входом подключенного к выходу элемента ИЛИ-НЕ, а выходом - к второму входу второго сумматора по модулю два, выход которого соединен со вторым выходом блока исправления ошибок. Источники информации, принятые во внимание при экспертизе 1.«Электронная техника, 1974 № 7 . 21-24. 2.«Электронная техника, 1975 № 4 . 65-68. 3.Сб. статей «Запоминающие устройста Под ред., Крайзмера Л. П. Л., «Энерия, 1974, вып. 4, с. 89, рис. 6 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955209A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство матрич-НОгО ТипА C САМОКОНТРОлЕМ | 1979 |

|

SU841063A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство | 1975 |

|

SU649044A1 |

| Запоминающее устройство | 1975 |

|

SU714496A1 |

Авторы

Даты

1980-05-05—Публикация

1975-10-13—Подача