I

Изобретение относится к радиотехнике и может использоваться при обработке в реапьнс 4 масштабе времени радиолокационных и гидроакустических сигналов.

Известен цифровой фильтр, содержащий счетчик числа периодов, выходы которого подключены к входам первого накапливающего су е4атора, выходы которого соединенгл с первыми входами блоков элементов И, выходы которых подключены к входам матричного умножителя, выход которого через регистр памяти подключен к входу второго накапливающего сумматора и второму входу первого блока элементов И, третий и четвертый входэл которого соединены соответственно с дополнительным входом второго блока элементов И и выходом первого блока памяти первый вход которого соединен с входом преобразователя код-аналог и выходом второго накапливающего сумматора, к соответствующим входам которого подключен дополнительный выход первого накпливающ го сумматора, дополнительный вход ксэторогр соединен с входом первогосчетчика адреса, выход которого через второй блок памяти подключен

к второму входу второго блока элементов И, а дополнительный вход второго накапливающего суммато й соединен с входом счетчика числа периодов и соответствующим входом первого накапливающего сумматора 1 ,

Однако известное устройство обладает низким быстродействием в режиме фильтрации, что не позволяет фильтровать относительно широкополосные сигналы.

Цель изобретения - повышение быстродействия.

Дпя этого в цифровой фильтр, содержащий счетчик числа периодов, выходы которого подключены к входам первого накапливающего сумматора, выходы которого соединены с первыми входами блоков элементов и, выходы которых подключены к входам матричного умножителя, выход которого чере регистр памяти подключен к входу второго накапливающего сумматора и второму входу первого блока элементов И, третий и четвертый входы которого соединены соответственно с дополнительным входом второго блока элементов И н выходом первого блока памяти, первый вход которого соедине с входом преобразователя код-аналого и выходом второго накапливающего

сумматора, к соответствующим входам которого подключен дополнитель {ый выход первого накапливающего сумматора, дополнительный вход которого соединен с входом первого счетчика адреса, выход которого через второй блок памяти подключен к второму входу второго блока элементов И, а дополнительный вход второго накапливающего сумматора соединен с входом счетчика числа периодов и соответствующим входом первого накапливающего сумматора, введены два дополнительны блока памяти, второй, третий и четвертый счетчики адреса и комбинационный сумматор, к входам которого подключены выходы дополнительных блоков памяти, входы которых соединены соответственно с выходами второго и третьего счетч ков адреса, при этом выход четвертого счетчика адреса подключен к второму входу первого блока памяти, а выход комбинационного сумматора соединен с третьим входом второро блока элементов И,причем выход первого дополнительного блока памяти подключен к дополнительному входу второго дополнительного блока памяти.

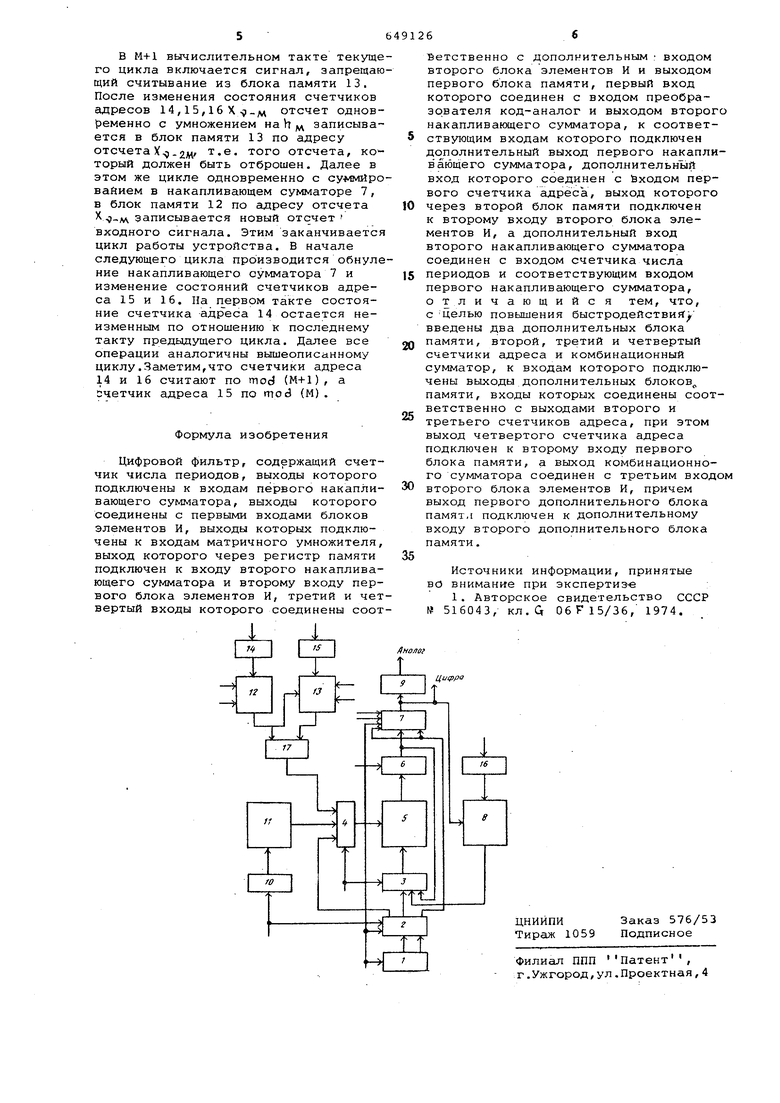

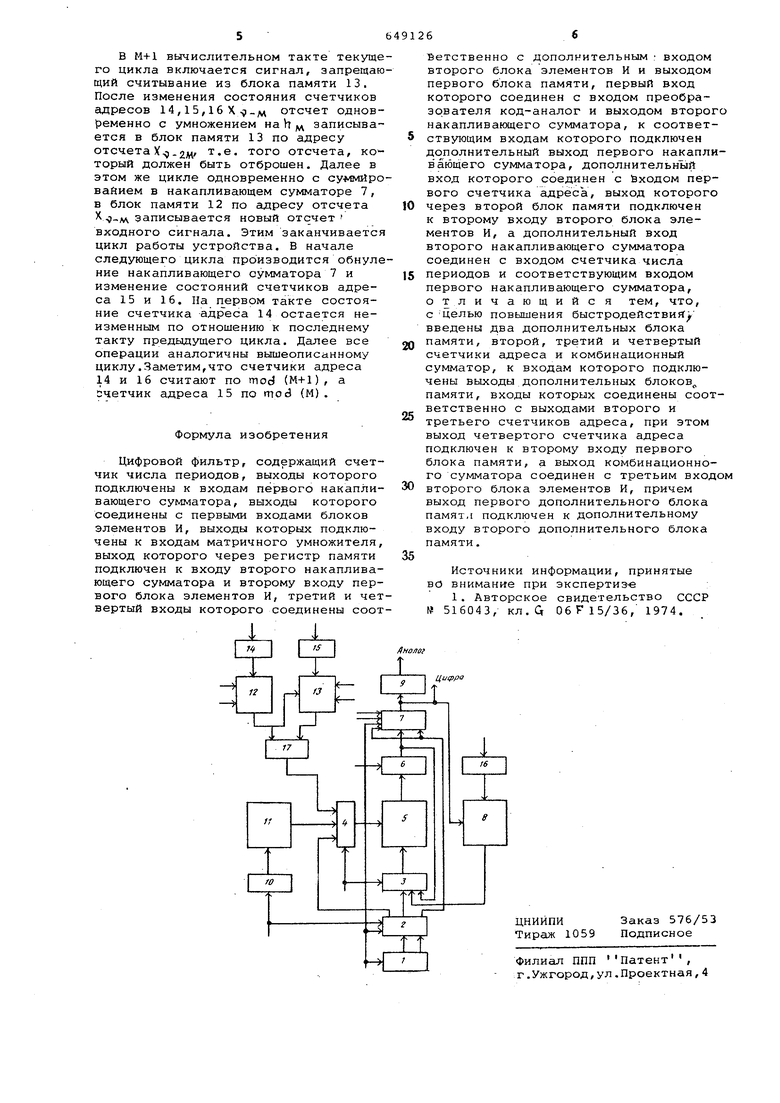

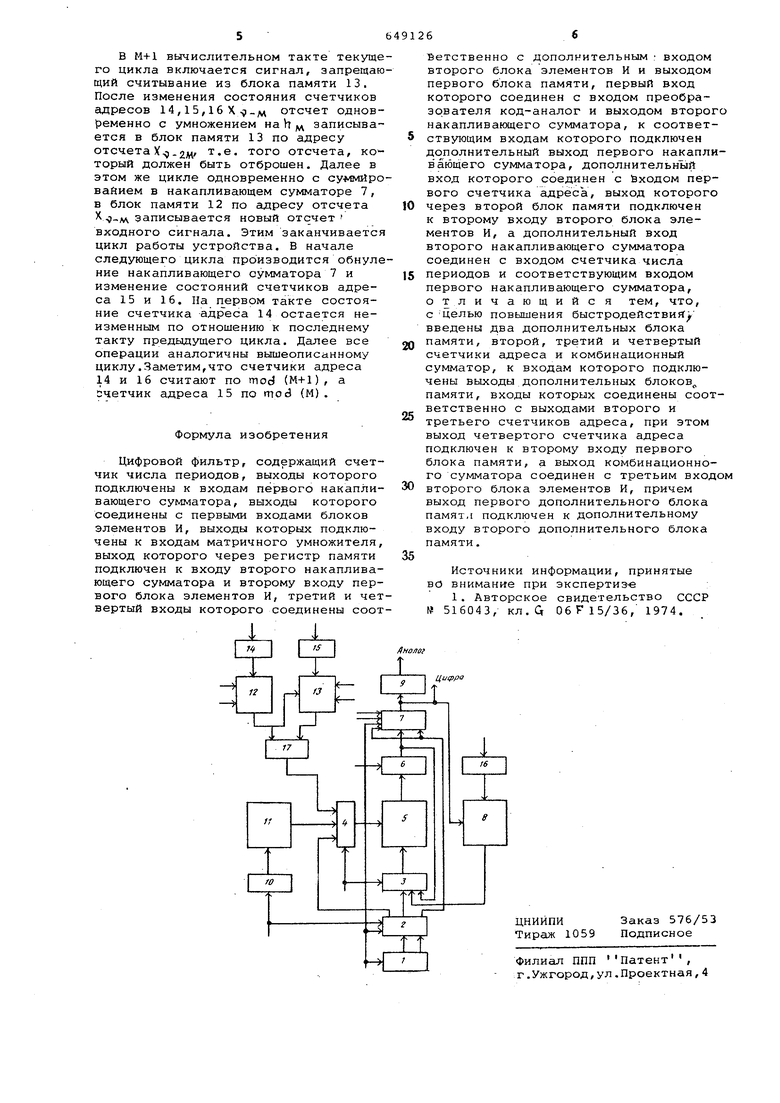

На чертеже представлена структурная электрическая схема предложенного устройства.

Цифровой фильтр содержит счетчик 1 числа периодов, выходы которого подключены к входам первого накапливающего суглматора 2, выходы которого соединены с первыми входами блоков элементов И 3,4, выходы которых подключены к входам матричного умножителя 5, выход которого через регистр 6 памяти подключен к входу второго накапливающего сумматора 7 и второму входу первого блока элементов И 3, третий и четвертый входы которого соединены соответственно с дополнительным вхдом второго блока элементов И 4 и выходом первого блока памяти 8, первый вход которого соединен с .входом пресЗразователя код-аналог и выходом второго накапливающего сумматора 7, к соответствующим входам которого подключен дополнительный выход первого накапливающего сумматора 2, дополнительный вход которого соединен с входом первого счетчика адреса 10, выход которого через второй блок памяти 11 подключен к второму входу второго блока элементов И 4, а дополнительный вхо второго накапливающего сумматора 7 соединен с входом счетчика 1 числа периодов и с соответствующим входом первого накапливающего сумматора 2, введенные два дополнительных блока памяти 12,13, второй, третий и четвертый счетчики адреса 14,15,16 ч комбинационный сумматор 17, к входа которого подключены выходы дополнительных блоков памяти 12,13, входы которых соединены соответственно с выходами второго и третьего счетчиков адреса 14,15, при этом выход четвертого, счетчика адреса 16 подключен к второму входу первого блока

памяти 8, а выход комбинационного сумматора 17 соединен с третьим входом в.торого блока элементов И 4 причем выход первого дополнительного блока памяти 12 подключен к дополнительному входу второго дополнительного блока памяти 13.

Работа устройства разделяется на два режима:

а)генерирование весовых коэффициентов;

б)фильтрация.

Так как весовая функция сиг-метрична, то в блоке памяти 8 весовых коэффициентов хранится только ее половина, т.е. М+1 отсчетов. Учитывая, что входные отсчеты, симметрично расположенные относительно среднего умножаются на один и тот же весовой коэффициент, появляется возможность увеличения вдвое быстродействия устройства путем введения их предварительного суммирования. Это удается сделать практически без увеличения требуемой аппаратуры, применяя новый способ адресации в блоках памяти 12

и 13 отсчетов входного сигнала, не требующий постоянной перезаписи отсчетов. Устройство в режиме фильтрации осуществляет операцию свертки отсчетов входного сигнала и соответствующих им весовых коэффициентов в виде

М-1

.

Первые Н отсчетов входного сигнала располагаются в блоке памяти 13, а последние М+1 - в блоке памяти 12, причем расположение текущих отсчетов в памяти не является фиксированным, а изменяется от цикла к циклу.

Вычислительный такт начинается со считывания крайних симметричных отсчетов входного сигнала и соответствующего отсчета весовой функции, хранящихся по адресам, установленным на счетчиках адресов .14,15 и 16.

. Далее отсчеты входного сигнала суммируются на комбинационном сумматоре 17 и сумма умножается на матричном умножителе 5 на коэффициент h (, . На блоки элементов И 3 и 4 подается на время фильтрации соответствующий управляющий потенциал. Результат умножения записывается в регистр

6 и затем добавляется в накапливающий сумматор 7. Далее с поступлением импульсов на входы счетчиков адресов ,14,15,16 производится изменение их состояния и описанная процедура по65 торяется.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой нерекурсивный фильтр | 1974 |

|

SU516043A1 |

| Цифровой фильтр | 1975 |

|

SU636616A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Фурье-Чебышеву | 1983 |

|

SU1136181A1 |

| Цифровой полосовой фильтр | 1976 |

|

SU813703A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| Цифровой синтезатор синусоидально- косинусоидальных сигналов | 1977 |

|

SU734706A1 |

Авторы

Даты

1979-02-25—Публикация

1977-03-09—Подача