1

Изобретение относится к импульсной технике.

Известен делитель частоты импульсов иа феррит-транзисторных эдементах, содержащий бинарную ячейку с подмагничиванием и ключевой элемент с двумя обмотками подмагничивания, подключенными к шинам сложения и вычитания, с двумя управляющими обмотками, каждая из которых соединена с соответствуюнхим выходом бинарной ячейки и с выходной обмоткой, подключенной к следующего разряда 1.

Недостатком данного делителя является малая стабильность деления.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является делитель частоты, содержащий N разрядов, каждый из которых содержит три феррит-транзисторных эле.мента, выходы первого ивторого из которых соединены с информационными входами последующих феррит-транзисторных элементов данного разряда, установочные входы всех феррит-транзисторных элементов соединены с шиной сброса, входы считывания ферриттранзисторных элементов первого разряда соединены с входными шинами, а входы считывания первого феррит-транзисторного элемента разряда соединены с информационным входом первого феррит-транзисторного элемента предыдущего разряда 2.

Недостатком данного делителя является

зависимость стабильности от параметров элементов.

Целью изобретения является повышение стабильности.

Это достигается тем, что в делитель частоты, содержащий N разрядов, каждый из

которых содержит три феррит-транзисторных элемента, выходы первого и второго из которых соединены с информационными входами последующих феррит-транзисторных элементов данного разряда, установочные

5 входы всех феррит-транзисторных элементов соединены с щиной сброса, входы считывания феррит-транзисторных эле ментов первого разряда соединены с первой входной щиной, а входы считывания первого феррит-транзисторного эле.мента разряда

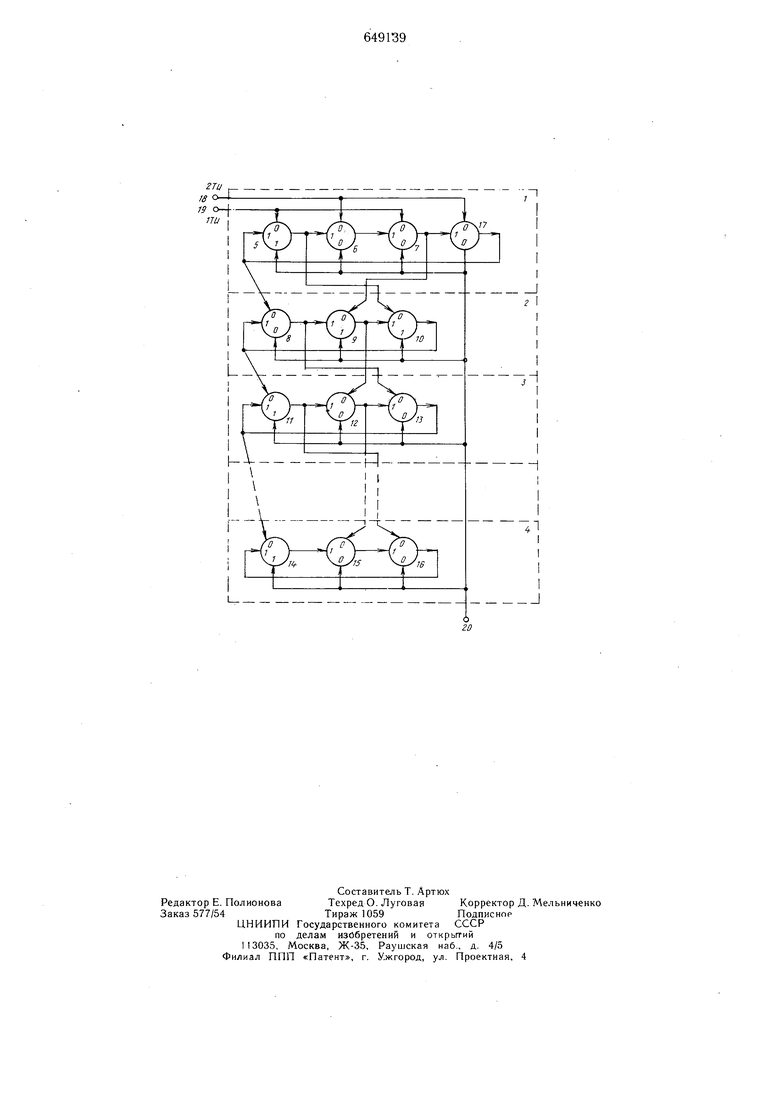

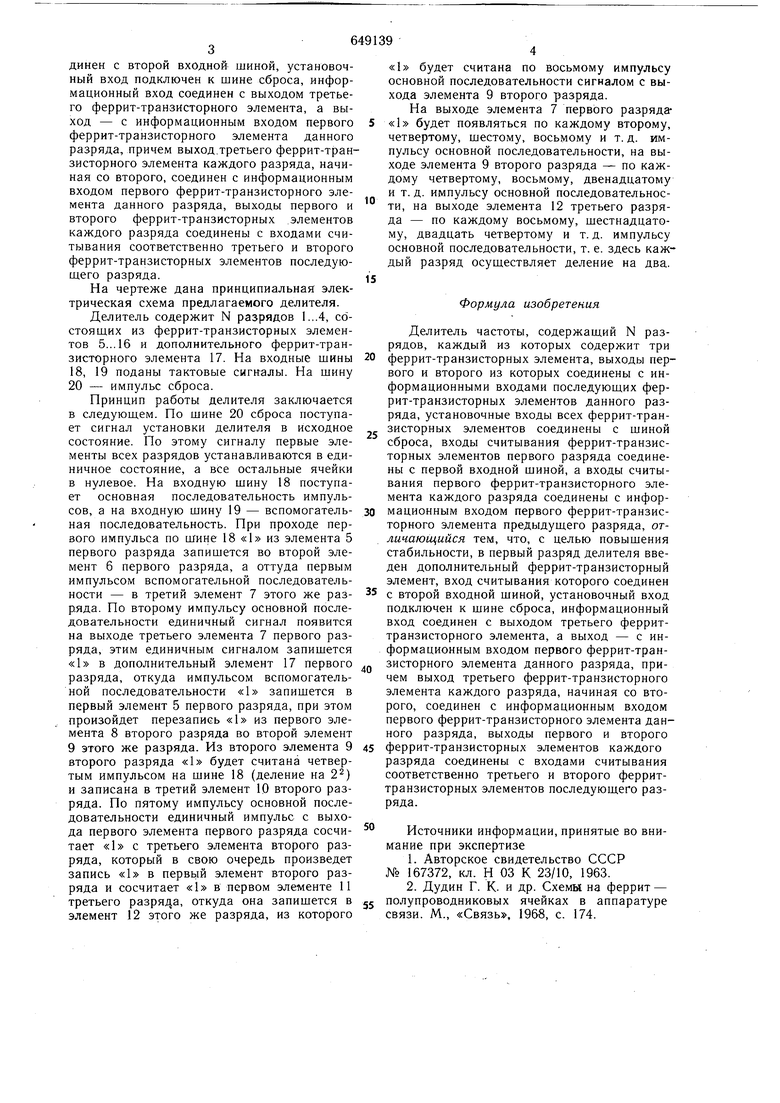

0 соединены с информационным входом первого феррит-транзисторного элемента предыдущего разряда, в первый разряд делителя введен дополнительный феррит-транзисторный элемент, вход счи-тывания которого соединен с второй входной шиной, установочный вход подключен к шине сброса, информационный вход соединен с выходом третьего феррит-транзисторного элемента, а выход - с информационным входом первого феррит-транзисторного элемента данного разряда, причем выход.третьего феррит-транзисторного элемента каждого разряда, начиная со второго, соединен с информационным входом первого феррит-транзисторного элемента данного разряда, выходы первого и второго феррит-транзисторных элементов каждого разряда соединены с входами считывания соответственно третьего и второго феррит-транзисторных элементов последующего разряда. На чертеже дана принципиальная электрическая схема предлагаемого делителя. Делитель содержит N разрядов 1...4, состоящих из феррит-транзисторных элементов 5...16 и дополнительного феррит-транзисторного элемента 17. На входные шины 18, 19 поданы тактовые сигналы. На шину 20 - импульс сброса. Принцип работы делителя заключается в следующем. По шине 20 сброса поступает сигнал установки делителя в исходное состояние. По этому сигналу первые элементы всех разрядов устанавливаются в единичное состояние, а все остальные ячейки в нулевое. На входную шину 18 поступает основная последовательность импульсов, а на входную щину 19 - вспомогательная последовательность. При проходе первого импульса по щине 18 «1 из элемента 5 первого разряда запишется во второй элемент 6 первого разряда, а оттуда первым импульсом вспомогательной последовательности - в третий элемент 7 этого же разряда. По второму импульсу основной последовательности единичный сигнал появится на выходе третьего элемента 7 первого разряда, этим единичным сигналом запишется «1 в дополнительный элемент 17 первого разряда, откуда импульсом вспомогательной последовательности «1 запишется в первый элемент 5 первого разряда, при этом произойдет перезапись «1 из первого элемента 8 второго разряда во второй элемент 9 этого же разряда. Из второго элемента 9 второго разряда «1 будет считана четвертым импульсом на шине 18 (деление на 2) И записана в третий элемент 10 второго разряда. По пятому импульсу основной последовательности единичный импульс с выхода первого элемента первого разряда сосчитает «1 с третьего элемента второго разряда, который в свою очередь произведет запись «1 в первьш элемент второго разряда и сосчитает «1 в первом элементе 11 третьего разряда, откуда она запишется в элемент 12 этого же разряда, из которого «1 будет считана по восьмому импульсу основной последовательности сигналом с выхода элемента 9 второго разряда. На выходе элемента 7 первого разряда«1 будет появляться по каждому второму, четвертому, шестому, восьмому и т. д. импульсу основной последовательности, на выходе элемента 9 второго разряда - по каждому четвертому, восьмому, двенадцатому и т. д. импульсу основной последовательности, на выходе элемента 12 третьего разряда - по каждому восьмому, шестнадцатому, двадцать четвертому и т. д. импульсу основной последовательности, т. е. здесь каждый разряд осуществляет деление на два. Формула изобретения Делитель частоты, содержащий N разрядов, каждый из которых содержит три феррит-транзисторных элемента, выходы первого и второго из которых соединены с информационными входами последующих феррит-транзисторных элементов данного разряда, установочные входы всех феррит-транзисторных элементов соединены с шиной сброса, входы считывания феррит-транзисторных элементов первого разряда соединены с первой входной шиной, а входы считывания первого феррит-транзисторного элемента каждого разряда соединены с информационным входом первого феррит-транзисторного элемента предыдущего разряда, огличающийся тем, что, с целью повыщения стабильности, в первый разряд делителя введен дополнительный феррит-транзисторный элемент, вход считывания которого соединен с второй входной шиной, установочный вход подключен к шине сброса, информационный вход соединен с выходом третьего ферриттранзисторного элемента, а выход - с информационным входом первого феррит-транзисторного элемента данного разряда, причем выход третьего феррит-транзисторного элемента каждого разряда, начиная со второго, соединен с информационным входом первого феррит-транзисторного элемента данного разряда, выходы первого и второго феррит-транзисторных элементов каждого разряда соединены с входами считывания соответственно третьего и второго ферриттранзисторных элементов последующего разряда. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 167372, кл. Н 03 К 23/10, 1963. 2.Дудин Г. К. и др. Схемы на феррит - полупроводниковых ячейках в аппаратуре связи. М., «Связь, 1968, с. 174.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки кода на четность | 1976 |

|

SU653616A1 |

| Дешифратор | 1974 |

|

SU572922A1 |

| Реверсивный счетчик | 1980 |

|

SU907813A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU272672A1 |

| УСТРОЙСТВО для АДРЕСОВАНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ ПОДЪЕМНО-ТРАНСПОРТНЫХ И ШАХТНЫХ УСТАНОВОК | 1970 |

|

SU270348A1 |

| РЕГИСТР СДВИГА | 1973 |

|

SU364029A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

| Устройство для обмена информацией | 1986 |

|

SU1363228A1 |

| Устройство для воспроизведения цифровой информации | 1984 |

|

SU1167645A1 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

Авторы

Даты

1979-02-25—Публикация

1977-10-27—Подача