Изобретение относится к устройствам микроэлектроники, в частности к логическим интегральным схемам с матричным расположением элементов.

Целью изобретения является снижение рассеиваемой мощности и повышение надежности удобства за счет устранения помех во время переключения выходных буферных каскадов интегральных схем на основе базового матричного устройства.

На фиг. 1 показана структура базового матричного устройства; на фиг.2 эквивалентная схема базовой ячейки устройства управления; на фиг.3 - пример коммутации транзисторов базовой ячейки устройства управления для реализации оптимизированного устройства управления выходным буферным каскадом и входного буферного каскада; на фиг.4 - принципиальные электрические схемы.

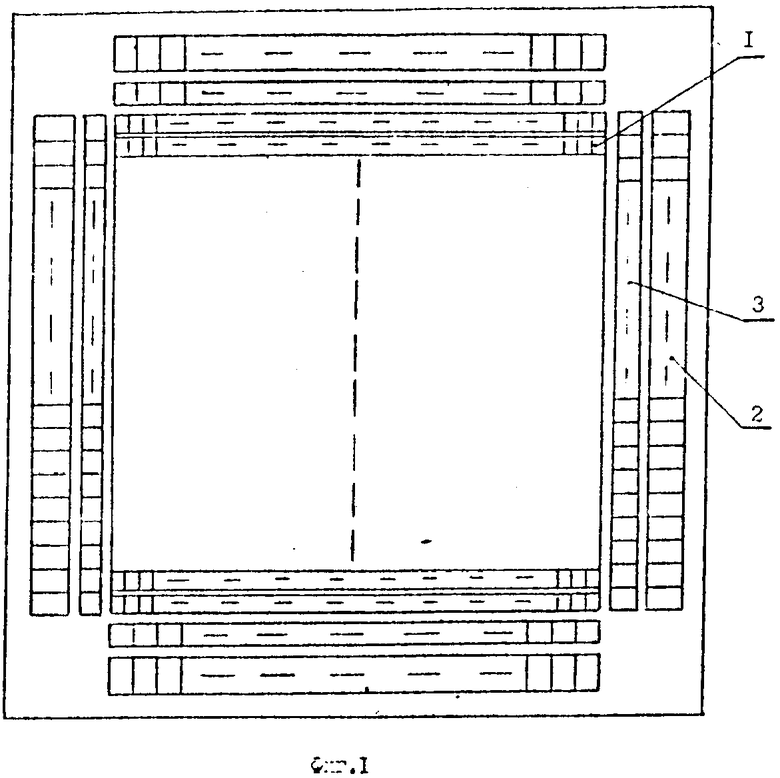

Базовое матричное устройство содержит блок 1 ячеек матрицы (БЯМ), ячейки этого типа предназначены для реализации внутренних логических вентилей и макроблоков. По периферии устройства размещены блоки 2 ячеек буфера (БЯБ), предназначенные для реализации мощных выходных каскадов. Они обеспечивают согласованную работу БИС на основе КМОП базового матричного устройства (БМУ) с внешними ТТЛ и КМОП интегральными схемами, а также защиту схемы от электрических перегрузок.

Блок 3 ячеек устройства управления (БЯУУ) предназначен для реализации прежде всего схем управления выходным буферным каскадом, а также входных буферных элементов, обеспечивающих согласование БИС с КМОП и ТТЛ уровнями внешних сигналов. В том случае, когда вывод БИС на основе БМУ используется как вход, на ячейках устройства управления можно реализовать входные триггеры-защелки или устройства управления внутренними буферными элементами.

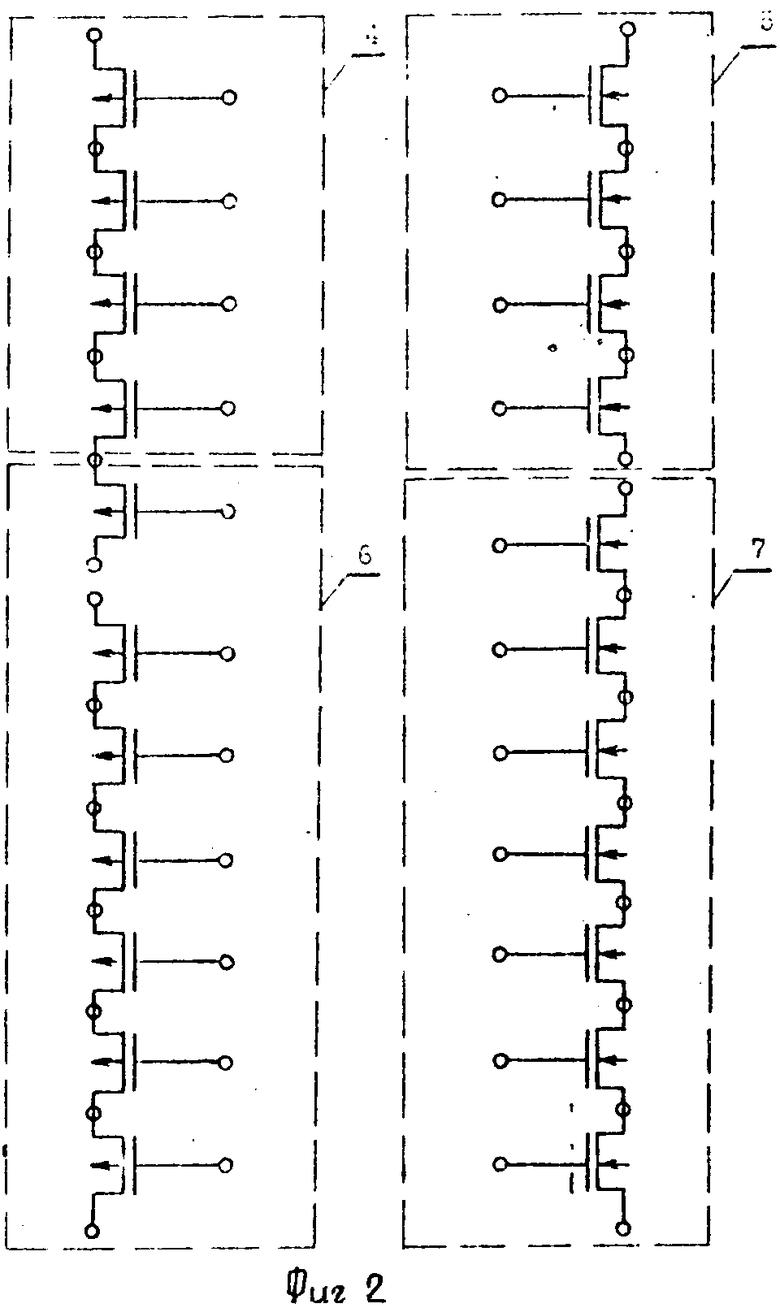

Представленная на фиг.2 эквивалентная схема базовой ячейки устройства управления содержит четыре блока 4-7 транзисторов. Транзисторы в блоках оптимизированы и имеют различные геометрические размеры. Блоки 4,5 предназначены для реализации оптимизированной схемы управления выходным буферным каскадом, а блоки 6,7 - для реализации входного буферного каскада.

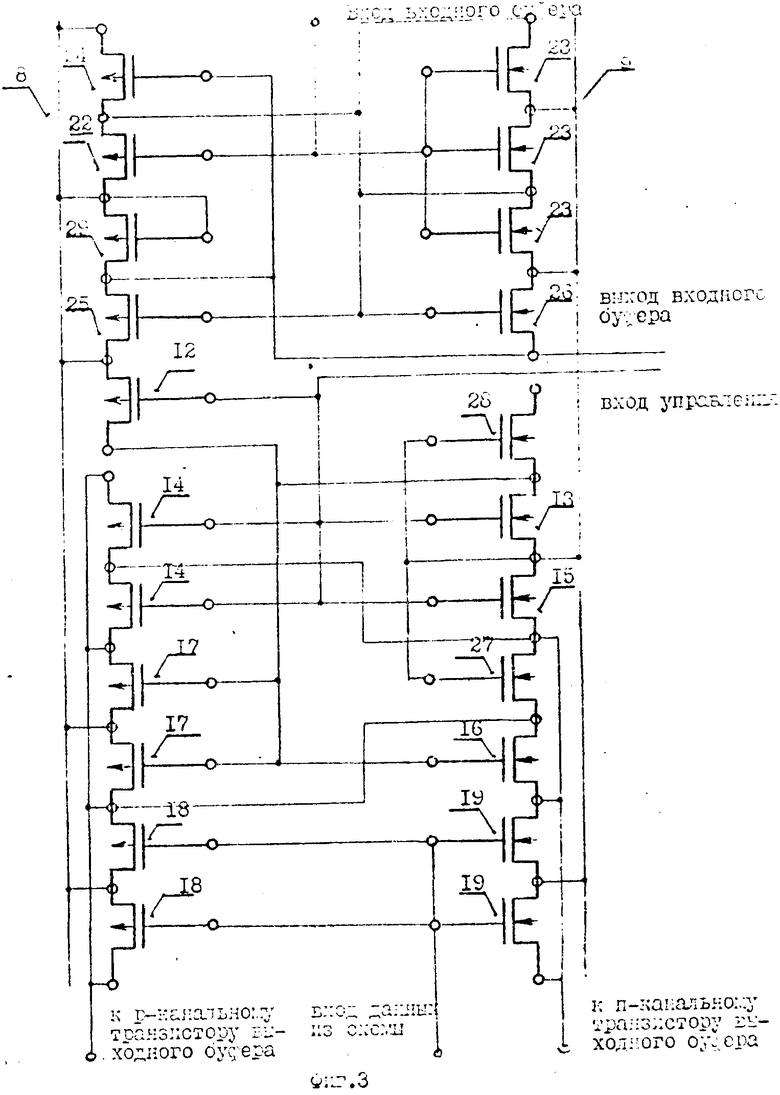

На фиг. 3 представлен пример коммутации транзисторов блоков 4-7 ячейки устройства управления для реализации оптимизированной схемы управления выходным буферным каскадом и входного буферного каскада, совместного по уровням сигналов с ТТЛ интегральными схемами. Принципиальные электрические схемы, реализованные на фиг.3, приведены на фиг.4.

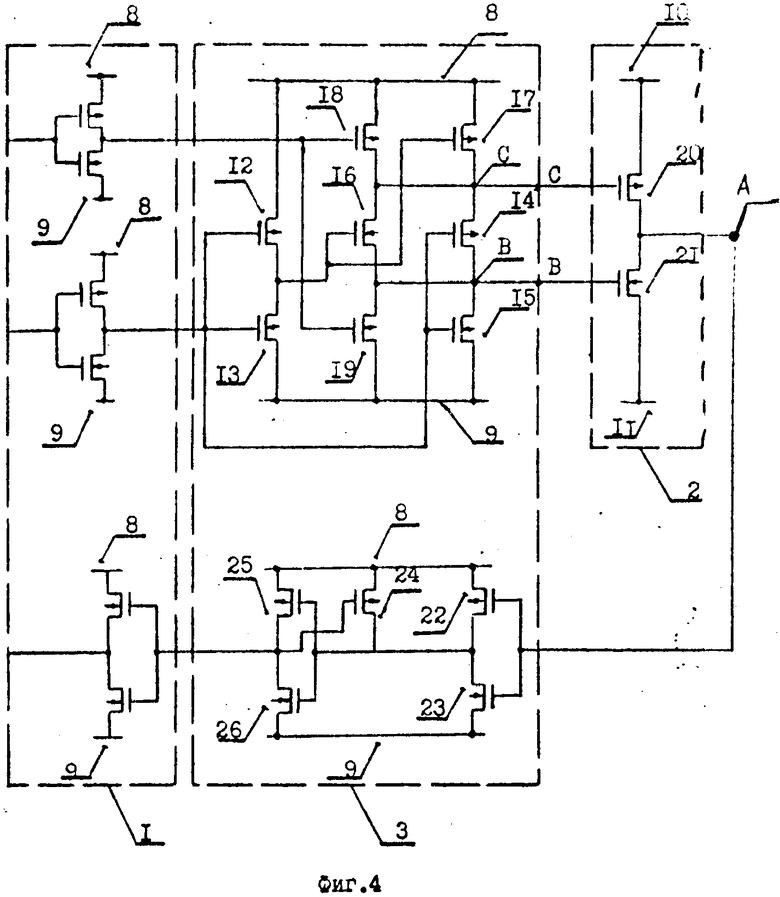

Часть схемы, составляющая блок 1, реализована на ячейках матрицы. Часть схемы, составляющая блок 2, реализована на ячейке буфера. Часть схемы, составляющая блок 3, реализована на ячейке устройства управления. БЯМ и БЯУУ имеют общую шину питания 8 и шину нулевого потенциала 9. БЯБ имеют отдельные шину питания 10 (буфер 10) и шину нулевого потенциала 11 (буфер 11).

Транзисторы 12-19 образуют устройство управления выходным буфером. Затворы транзисторов 12, 13, 14, 15 объединены. Стоки транзисторов 12, 13 присоединены к затворам транзисторов 16, 17. Затворы транзисторов 18 и 19 объединены. Стоки транзисторов 16, 17, 18 присоединены к истоку транзистора 14 (точка С). Стоки транзисторов 14, 15, 19 присоединены к истоку транзистора 16 (точка В). Истоки транзисторов 13, 15, 19 подключены к шине нулевого потенциала 9. Истоки транзисторов 12,17,18 подключены к шине питания 8. Первый и второй входы блока 1 подключены соответственно к объединенным затворам транзисторов 18 и 19, 12 и 13 блока 2. Выход В блока 3 устройства управления подсоединен к затвору транзистора выходного буфера. Выход С подключен к затвору транзистора 20 того же блока 2. Стоки транзисторов 20, 21 объединены с контактной площадкой кристалла и затворами транзисторов 22, 23 входного буфера, реализованного на ячейке устройства управления. Истоки транзисторов 20, 21 подключены к шине 10 питания буфера и шине 11 нулевого потенциала буфера. Соответственно стоки транзистора 22, 23, 24 объединены с затворами транзисторов 25, 26. Затворы транзисторов 27, 28 подключены к шине нулевого потенциала. Истоки транзисторов 22,24,25 присоединены к шине питания 8, а истоки транзисторов 28, 26 - к шине 9 нулевого потенциала. Стоки транзисторов 25, 26 объединены с затвором транзистора 24 и соединены с входом блока 1.

Представленное на фиг.4 устройство работает следующим образом.

Если на затворы транзисторов 13, 12 подан сигнал логической единицы, то транзистор 12 будет в непроводящем состоянии, транзистор 13 - в проводящем и на затворах транзисторов 16, 17 появится сигнал логического нуля. Транзисторы 15, 17, находятся в проводящем состоянии, транзисторы 14, 16 - в непроводящем. На затвор транзистора 20 поступает сигнал логической единицы, на затвор транзистора 21 - сигнал логического нуля, поэтому транзисторы 20, 21 находятся в проводящем состоянии, а выходной буфер - в третьем состоянии, а выходной буфер - в третьем состоянии. Если на затворы транзисторов 12, 13 подать логический ноль, то транзистор 12 будет находиться в проводящем состоянии, транзистор 13 в непроводящем, транзисторы 14, 16 в проводящем, а транзисторы 15, 17 - в непроводящем состоянии. Пусть на затворах транзисторов 18, 19 был установлен сигнал логического нуля, при этом транзистор 18 находится в проводящем, а транзистор 19 - в непроводящем состоянии, поэтому в точках В и С установится логическая единица. Транзистор 20 находится в непроводящем состоянии, а транзистор 21 - в проводящем. Таким образом, в точке А, т.е. на входе устройства, установится сигнал логического нуля. При изменении логического сигнала от нуля до единицы на затворах транзисторов 18, 19 транзистор 18 переходит в непроводящее состояние, а транзистор 19 - в проводящее. Через транзистор 19 начинают разряжаться емкости в точках В и С. Емкость в точке С разряжается через сопротивление открытых транзисторов 14 и 16, поэтому напряжение в точке В достигает уровня логического нуля раньше, чем в точке С на время t.

Ширина канала транзисторов 14, 16 подобрана так, что времени достаточно для того, чтобы вывести транзистор 21 из области насыщения и уже после этого транзистор 20 переходит в проводящее состояние. Это до минимума снижает протекание "сквозных" токов через транзисторы 20, 21 выходного каскада и тем самым снижает потребляемую мощность. Аналогичным образом работает схема при изменении сигнала на затворах транзисторов 18, 19 от уровня логической единицы до уровня логического нуля.

Использование данного типа устройства управления выходным каскадом с оптимизированными транзисторами 12-19 позволяет уменьшить пиковое значение тока потребления в 1,5 раза и уменьшить скорость нарастания тока до 25 мА/нс. На транзисторах 22-26 выполнен выходной ТТЛ буфер. Пусть на затворы транзисторов 22, 23 подан сигнал логической единицы. Транзистор 22 будет в непроводящем, транзистор 23 - в проводящем состоянии. Поэтому на затворах транзисторов 25, 26 появляется сигнал логического нуля. Транзистор 25 будет находиться в непроводящем состоянии, транзистор 26 - в проводящем. На выходе входного буфера устанавливается сигнал логической единицы, транзистор 24 находится в непроводящем состоянии. При переходе сигнала на затворах транзисторов 22-23 от уровня логической единицы до уровня логического нуля напряжение на стоках транзисторов 22, 23 начинает перемещаться от уровня логического нуля к уровню логической единицы, а на стоках транзисторов 25, 26 - от уровня логической единицы до уровня логического нуля. При этом транзистор 24 переходит в проводящее состояние. При обратном переключении транзистор 24 переключится в непроводящее состояние только тогда, когда на стоках транзисторов 25-26 появится сигнал логической единицы. Таким образом, обратный выброс на фронтах сигналов не приводит к ложному срабатыванию буфера. Транзистор 24 вносит гистерезис в переключении входного ТТЛ буфера, что повышает помехоустойчивость. Кроме того, реализация входных буферных элементов на ячейках устройства управления позволяет устранить влияние выходных буферных каскадов на входные, поскольку для них используются разные шины питания и шины нулевого потенциала, т.е. обеспечивается развязка по этим шинам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

| МАГНИТОУПРАВЛЯЕМАЯ ЛОГИЧЕСКАЯ ЯЧЕЙКА | 1994 |

|

RU2072590C1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| МАТРИЧНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2016 |

|

RU2727767C1 |

| Устройство считывания для программируемой логической матрицы | 1988 |

|

SU1566410A1 |

| УСТРОЙСТВО ДЛЯ ЭЖЕКЦИИ ТЕКУЧЕЙ СРЕДЫ | 2005 |

|

RU2337010C2 |

Изобретение относится к логическим интегральным схемам с матричным расположением элементов. Целью изобретения является повышение надежности и снижение рассеиваемой мощности. Базовое матричное устройство содержит блоки ячеек матрицы, по периферии которого размещены блоки ячеек буфера, предназначенные для реализации мощных выходных каскадов. Дополнительно введенные блоки ячеек устройства управления расположены между блоками ячеек буфера и блоком ячеек матрицы. Ячейки устройства управления содержат четыре последовательные цепи МДП транзисторов различной конфигурации, из которых две выполнены на транзисторах первого типа, а две другие - на транзисторах второго типа. Изобретение позволяет снизить скорость нарастания тока в буферном каскаде, напряжение помех и пиковый ток потребления. 1 з.п.ф-лы, 4 ил.

| Патент США N 4461815, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-07-15—Публикация

1989-04-19—Подача