(54) УСТРОЙСТВО МИКРОПРОЦЕССОРНОЙ СВЯЗИ

Изобретение относится к вычислительной технике и в частности « средствам микропроцессорного управления.

Микропроцессоры представляют собой законченные цифровые вычислители, которые находят все большее применение при построении систем управления и обработке данных.

Однако обладая многими известными достоинствами, микропроцессоры имеют и существенный недостаток, заключающийся в ограниченности количества выводов, что не позволяет без применения дополнительных модулей организовать достаточно эффективный интерфейс связи с внешними устройствами.

Известны устройства, в которых организована связь микропроцессора с внешними устройствами (памятью, устройствами ввода-вывода и т.д.) 1. В этих устройствах ЗУ состояния (регистр состояния) осуществляет прием из микропроцессора сигналов состояни и выдачу нх внешним устройствам. Формирователь информационных сигналов и усилители адресных сигналов обеспечивают согласование соответственно адресных

и информационных шин микропроцессора с внешними устройствами. Генератор тактовых сигналов осуществляет общую синхронизацию устройства.

Недостатками подобной организации связи микропроцессора с внешними устройствами являются наличие раздельных шин данных J(вxoдныx и выходных) t и наличие нерационально большой номенклатуры сигналов состояния.(8 шин состояния). ,0 Наиболее близким к предлагаемому устройству является контролер связи микропроцессора с внешними устройства, который включает в себя шинные формирователи данных, регистр состояний и шифратор сигналов состояния. Для осуществления возis можности использования интерфейсной магистрали другими активными устройствами микропроцессор содержит входную шину «Захват. При наличии на этой шине сигнала от внешнего устройства микропроцессор j(j останавливается (входит в режим «Захват),, снимает все сигналы со своих интерфейсных шин и выдает сигнал «подтверждение захвата, по которому внешнее устройство, выдавшее сигнал «Захват, может использовать интерфейсную магистраль для обмена данными {2.

Недостатки такой организации захвата интерфейсной магистрали другими активными устройствами заключается в том, что микропроцессор анализирует во втором такте машинного цикла наличие сигнала «Захват и, если таковой имеется, входит в режим «Захват, прекратив выполнение цикла.

После сброса сигнала«Захват микропроцессор начинает невыполненный цикл сна. чала, непроизводительно затрачивая время на повторное выполнение первых двух тактов, микропроцессор вырабатывает сигнал подтверждения захвата только в том случае, если к моменту выполнения во втором такте анализа наличия запроса «Захвата таковой имеется. Если же запрос «Захвата от внешнего устройства появляется после выполнения анализа, сигнал подтверждения захвата появится только во втором такте следующего цикла, и таким образом периферийное устройство не имеет возможности пользоваться интерфейсной магистрьалыо в течение части или в наиболее неблагоприятном случае всего цикла, хотя интерфейсная магистраль в это время свободна и могла бы быть использована для передачи данных другими активными устройствами. Следовательно, при выполнении команд микропроцессором существуют достаточно большие интервалы времени, когда интерфейсные шины свободны (не производится.обмен данными), однако использовать их внешние активные устройства не имеют возможности. Кроме того, когда внешнее устройство использует интерфейсную магистраль, микропроцессор в это время не выполняет никаких операций, из чего следует, что при подключении к интерфейсу микропроцессора других активных устройств, интерфейсная магистраль используется недостаточно эффективно, что приводит к снижению производительности микропроцессорных систем. Другой недостаток указанных устройств заключается в том, что в работе микропроцессора предусмотрен некоторый временной интервал, в течение которого внешнее устройство, к которому адресовался микропроцессор, должно Б случае своей неготовности к функционированию выставить соответствующий сигнал. Неполучение такого сигнала вос принимается микропроцессором как свидетельство готовности адресованного внешнего устройства. .Если последнее, будучи неготово, по какой-либо причине не успеет за отведенное время выставить сигнал неготовности, микропроцессор выполнит операции, соответствующие готовности готовности внешнего устройства, что приведет к нарушению правильного функционирования устройства в целом. Таким образом, регламентирование времени между выдачей адреса и реакцией микропроцессора на готовность внешнего устройства накладывает ограничения на длину интерфейсной магистрали, ее конструкцию, количество подключаемых внешних устройств, ужесточает требования к быстродействию элементов и создает другие трудности.

Цель изобретения - повышение быстродействия устройства.

Для устранения указанных недостатков в устройство микропроцессорной связи, содержащее группу элементов И адреса, группу элементов И данных, регистр данных,

регистр состояний, шифратор управляющих сигналов, генератор тактовых сигналов, элемент И, причем информационные входы элементов И группь адреса являются первой группой входов устройства, а выходы

элементов И группы адреса являются первой группой выходов устройства, информационные входы элементов И группы данных соединены со второй группой входов устройства, а выходы элементов И группы данных являются второй группой выходов устройе ства, вход регистра данных является первым входом устройства, первый управляющий вход регистра данных соединен со вторым входом устройства, а выход регистра данных является первым выходом устрой- ства, входы регистра состояний соединены со второй группой входов устройства, управляющий вход регистра состояний подключен к выходу элемента И, а выход регистра состояний подключен к первому входу шифратора управляющих сигналов, управляющий

0 выход которого соединен с управляющими входами элементов И труппы адреса, элементов И группы данных и вторым управляющим входом регистра данных, а выходы шифратора управляющих сигналов являются третьей группой выходов устройства, выход генератора тактовых сигналов соединен с первым входом элемента И и является вторым выходом устройства, при этом второй вход элемента И соединен с третьим входом устройства, введены RS-триггер готовности, блок асинхронной связи, блок анализа запросов, причем D-вход RS-триггера готовности является четвертым входом устройства, синхровход триггера готовности подключен к выходу элемента И, вход «сброс триггера готовности соединен с первым вы ходом блока асинхронной связи, прямой выход триггера готовности соединен с первым входом блока асинхронной связи, а обратный выход триггера готовности является третьим выходом устройства, второй вход

0 блока асинхронной связи соединен с выходом генератора тактовых импульсов, группа входов-выходов блока асинхронной связи является первой группой входов-выходов устройства, второй выход блока асинхронной связи подключен ко второму входу шифра тора управляющих сигналов вход-выход блока асинхронной связи соединен с первым входом-выходом блока анализа запросов; вторая группа входов выходов которого я в

ляется второй группой входов-выходов устройства.

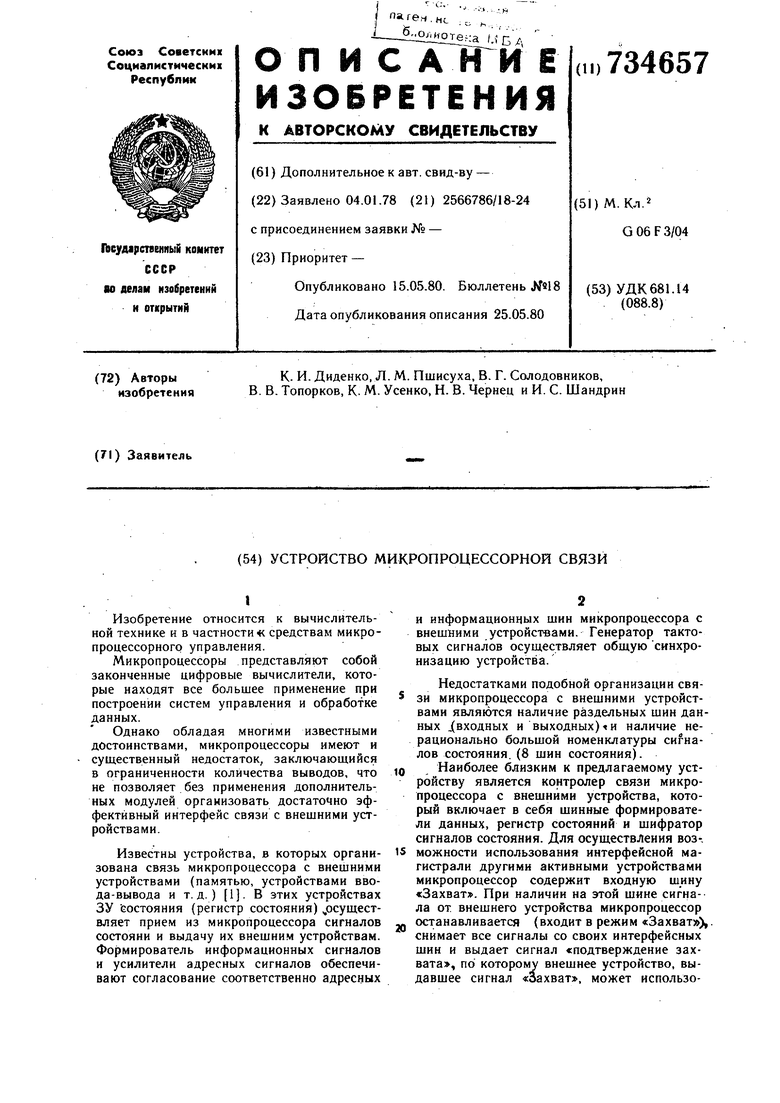

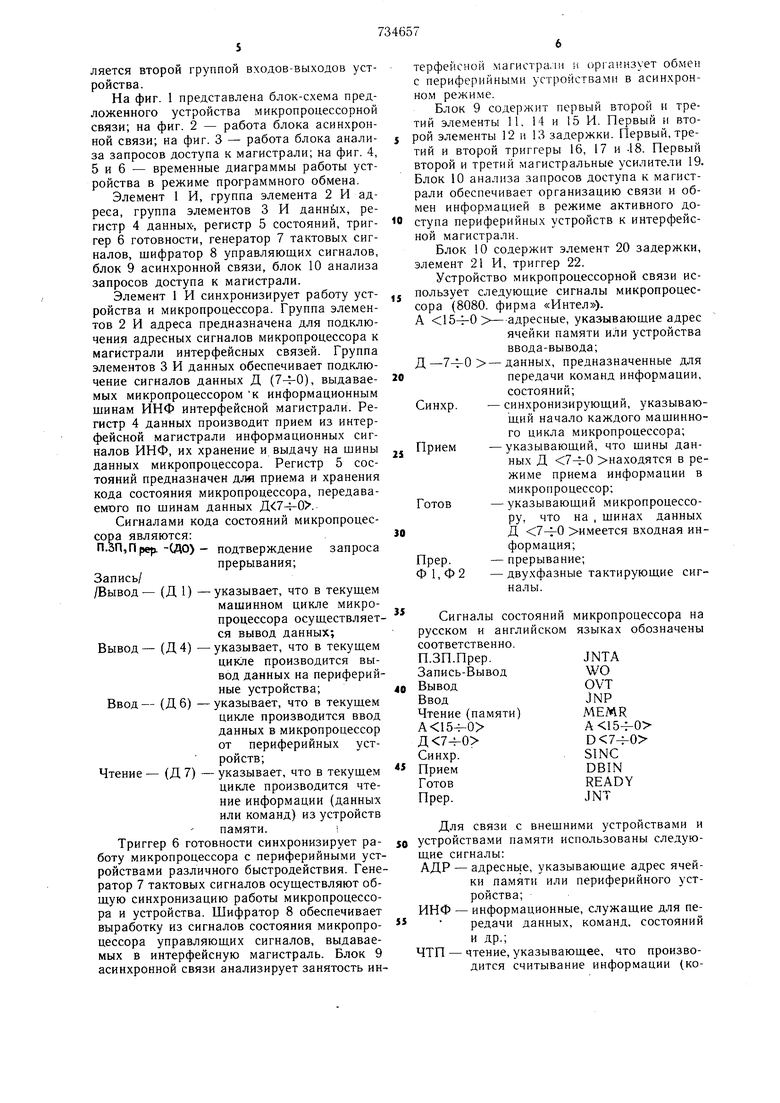

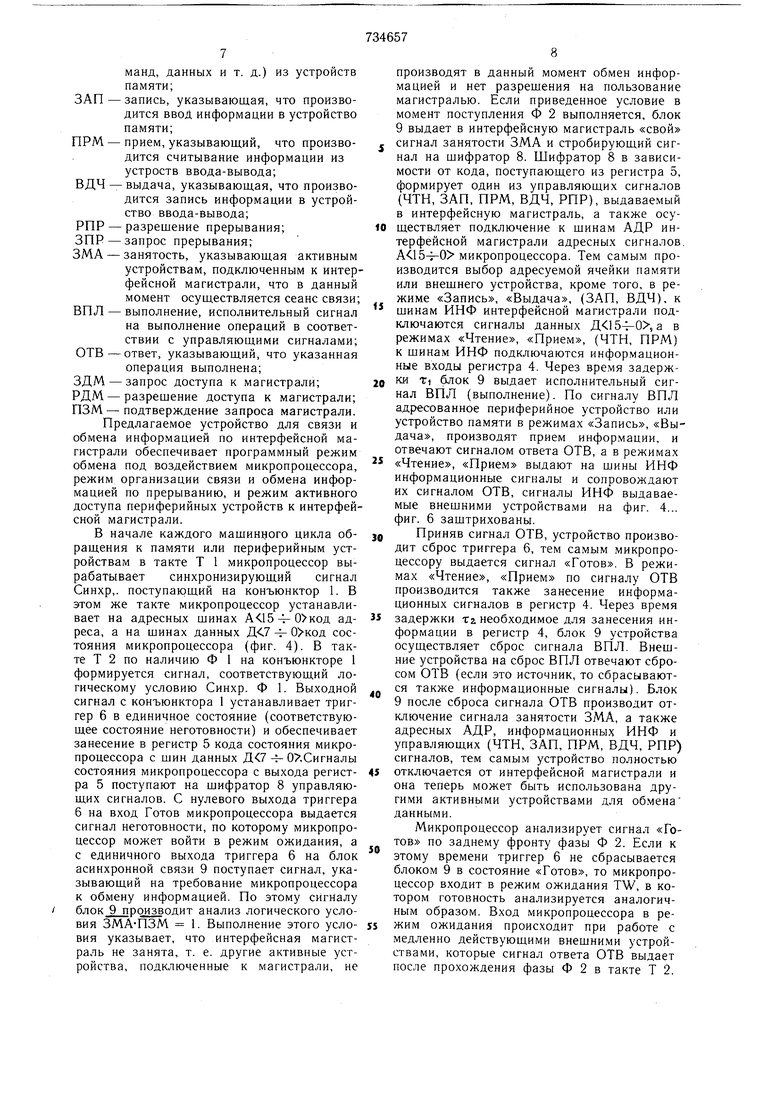

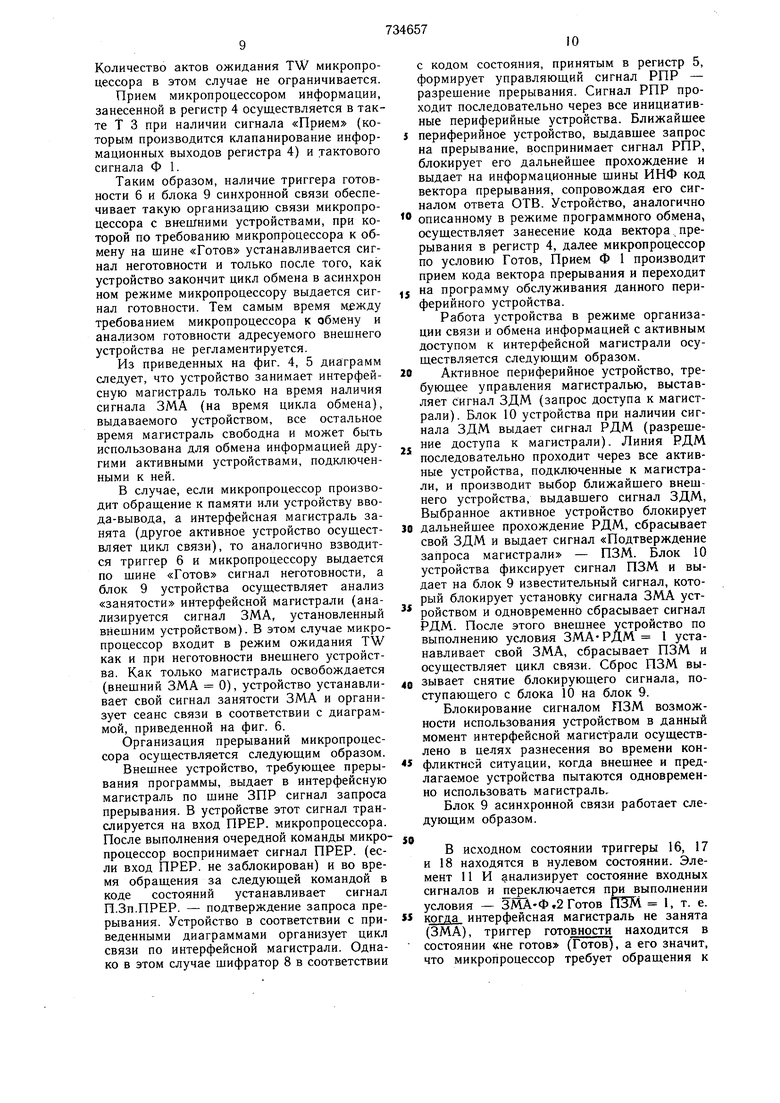

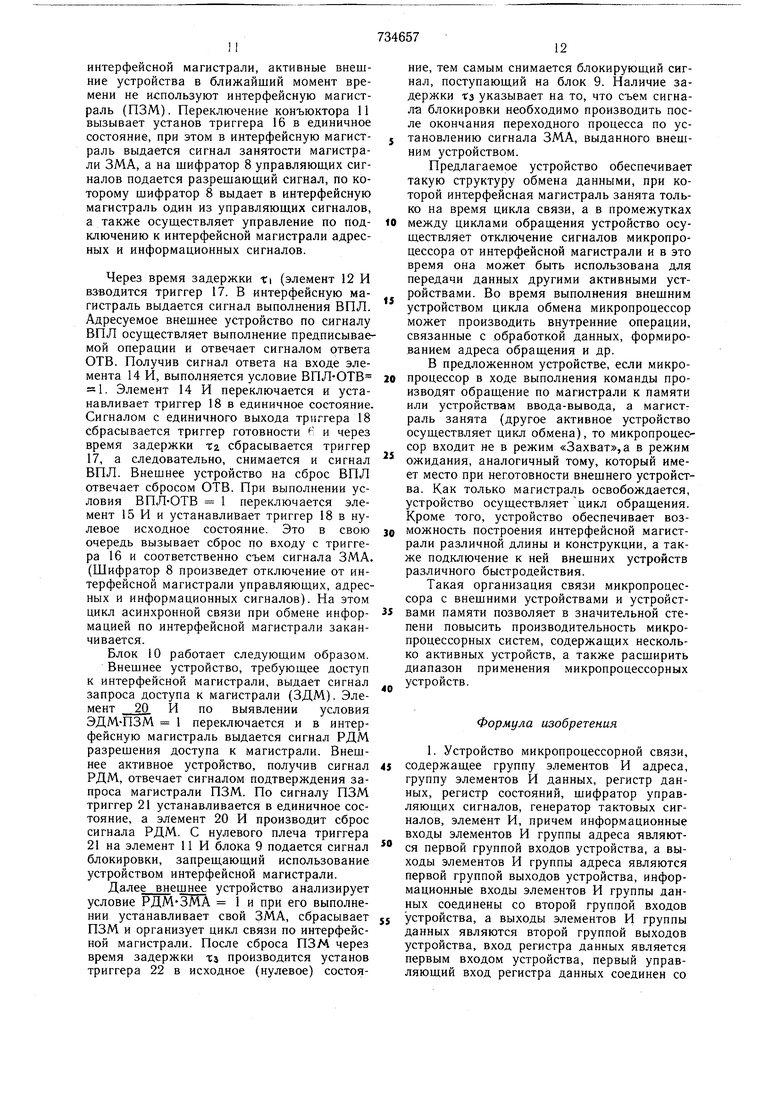

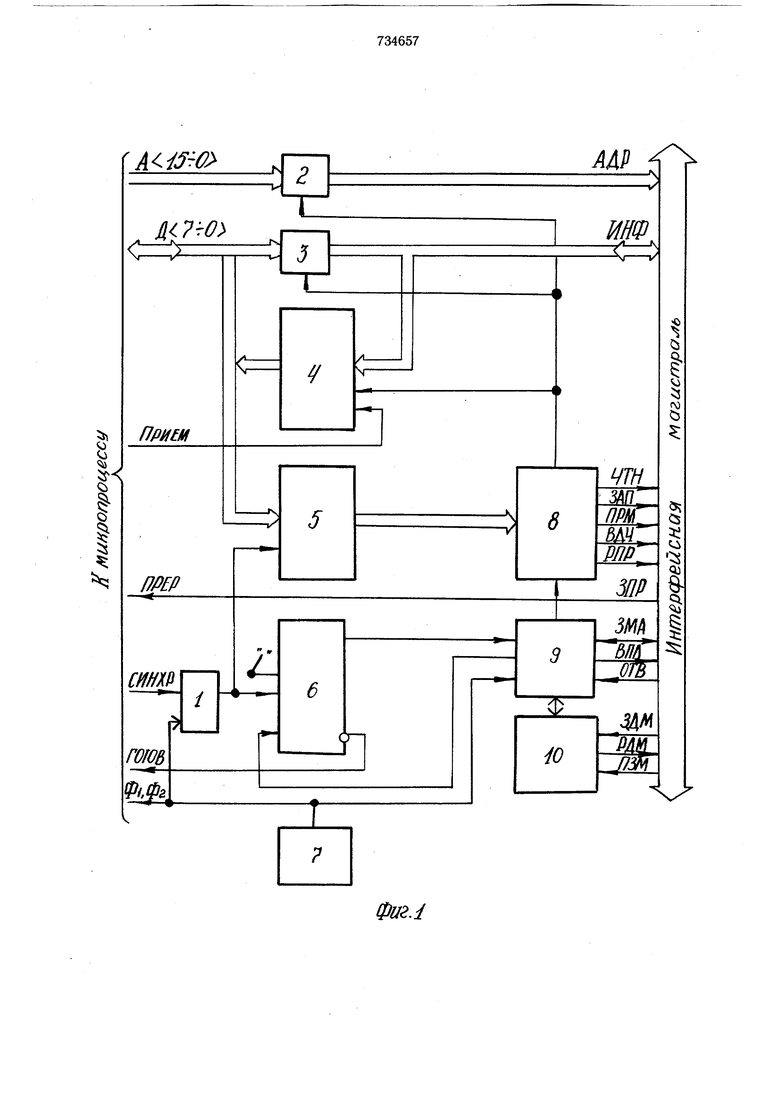

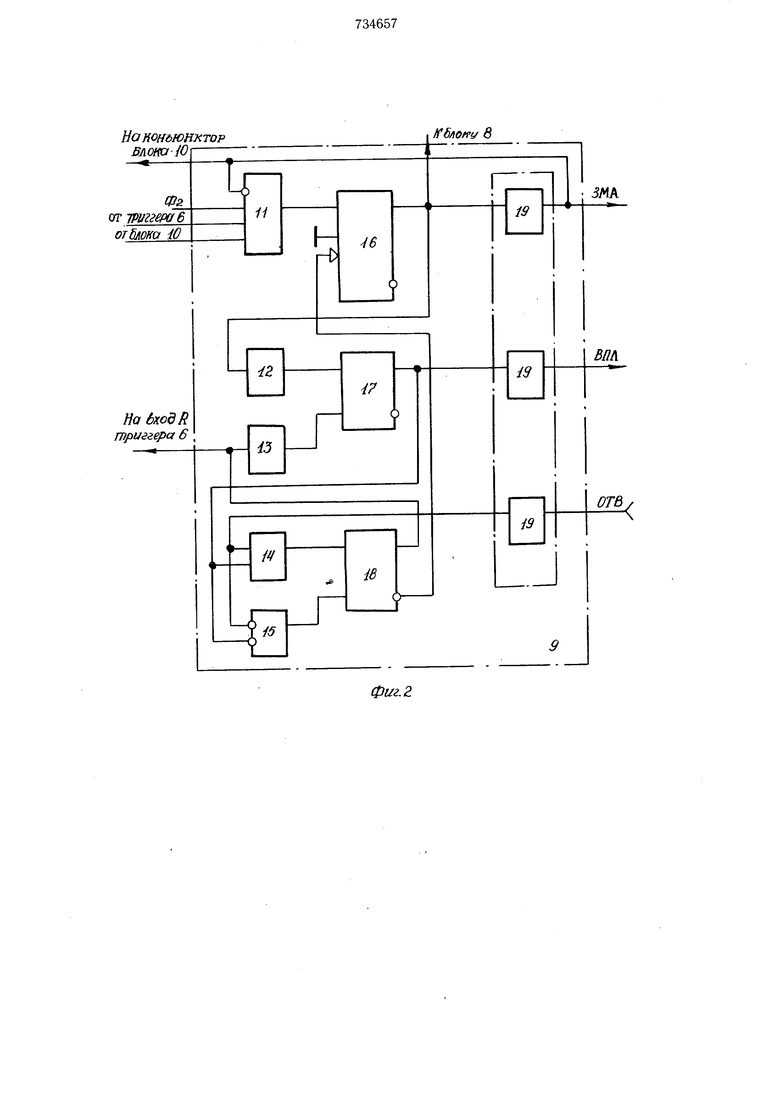

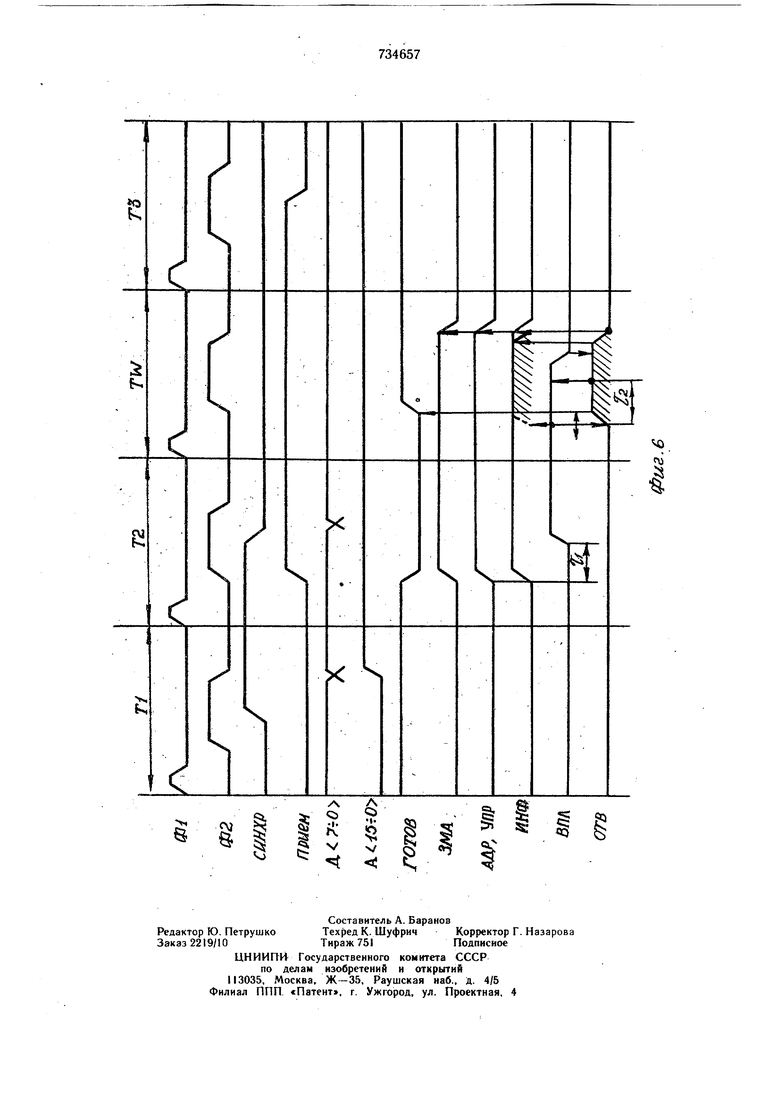

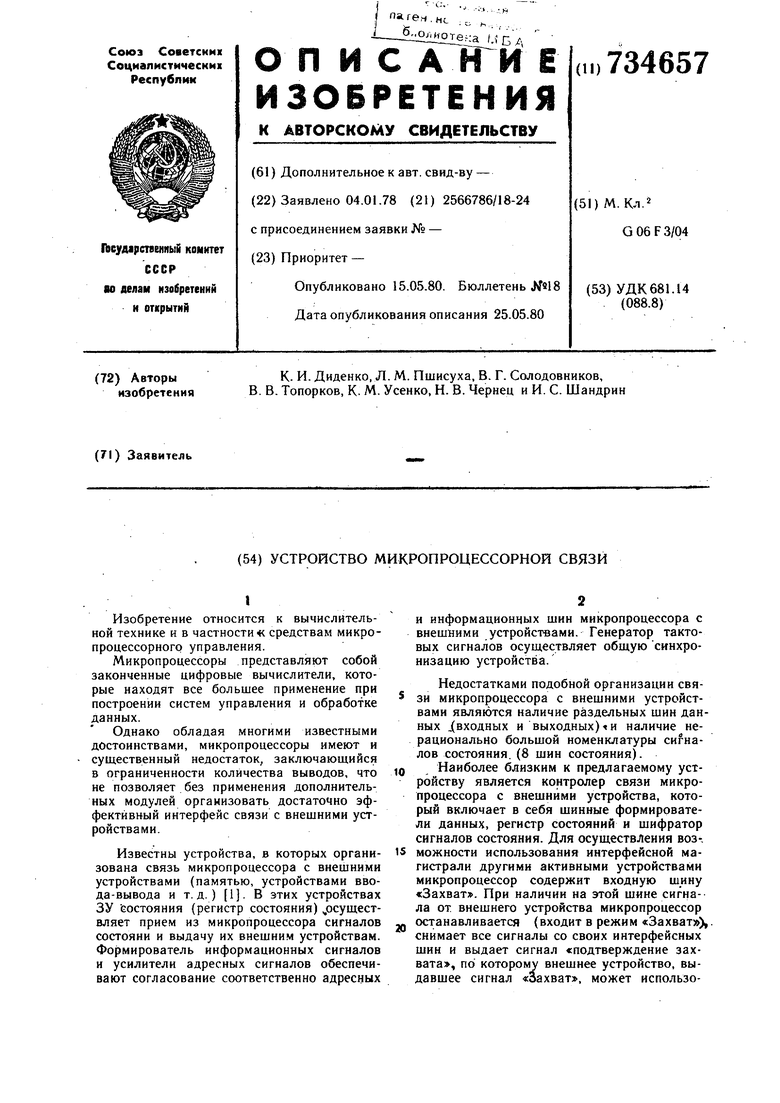

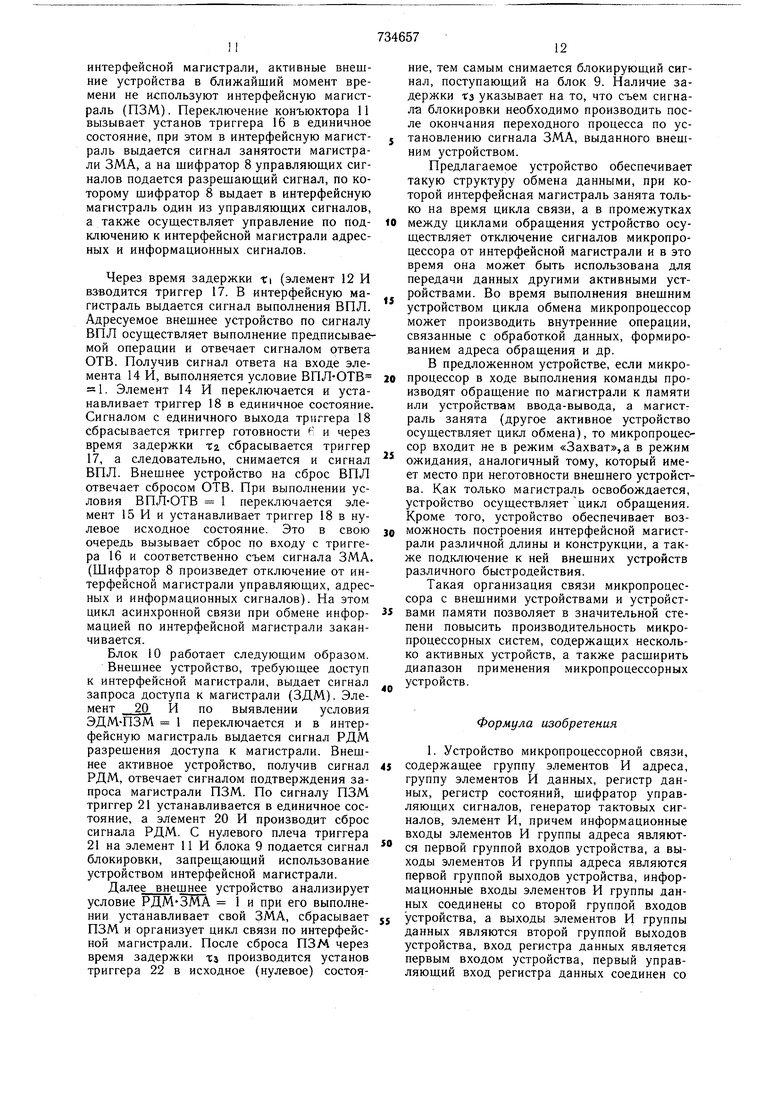

На фиг. 1 представлена блок-схема предложенного устройства микропроцессорной связи; на фиг. 2 - работа блока асинхронной связи; на фиг. 3 - работа блока анализа запросов доступа к магистрали; на фиг. 4, 5 и 6 - временные диаграммы работы устройства в режиме программного обмена.

Элемент 1 И, группа элемента 2 И адреса, группа элементов 3 И даннйх, регистр 4 данных-, регистр 5 состояний, триггер 6 готовности, генератор 7 тактовых сигналов, шифратор 8 управляющих сигналов, блок 9 асинхронной связи, блок 10 анализа запросов доступа к магистрали.

Элемент 1 И синхронизирует работу устройства и микропроцессора. Группа элементов 2 И адреса предназначена для подключения адресных сигналов микропроцессора к магистрали интерфейсных связей. Группа элементов 3 И данных обеспечивает подключение сигналов данных Д (7-4-0), выдаваемых микропроцессором к информационным шинам ИНФ интерфейсной магистрали. Регистр 4 данных производит прием из интерфейсной магистрали информационных сигналов ИНФ, их хранение и выдачу на шины данных микропроцессора. Регистр 5 состояний предназначен для приема и хранения кода состояния микропроцессора, передаваемого по шинам данных .

Сигналами кода состояний микропроцессора являются: П.оП,Прер.-(ДО) - подтверждение запроса

прерывания; Запись/

/Вывод- (Д 1) -указывает, что в текушем машинном цикле микропроцессора осуществляется вывод данных;

Вывод - (Д 4) - указывает, что в текущем цикле производится вывод данных на периферийные устройства;

Ввод - (Д 6) - указывает, что в текушем цикле производится ввод данных в микропроцессор от периферийных устройств;

Чтение - (Д 7) - указывает, что в текушем цикле производится чтение информации (данных или команд) из устройств памяти.

Триггер 6 готовности синхронизирует работу микропроцессора с периферийными устройствами различного быстродействия. Генератор 7 тактовых сигналов осуществляют общую синхронизацию работы микропроцессора и устройства. Шифратор 8 обеспечивает выработку из сигналов состояния микропроцессора управляющих сигналов, выдаваемых в интерфейсную магистраль. Блок 9 асинхронной связи анализирует занятость интерфейсной магистрали .и организует обмен с периферийными устройствами в асинхронном режиме.

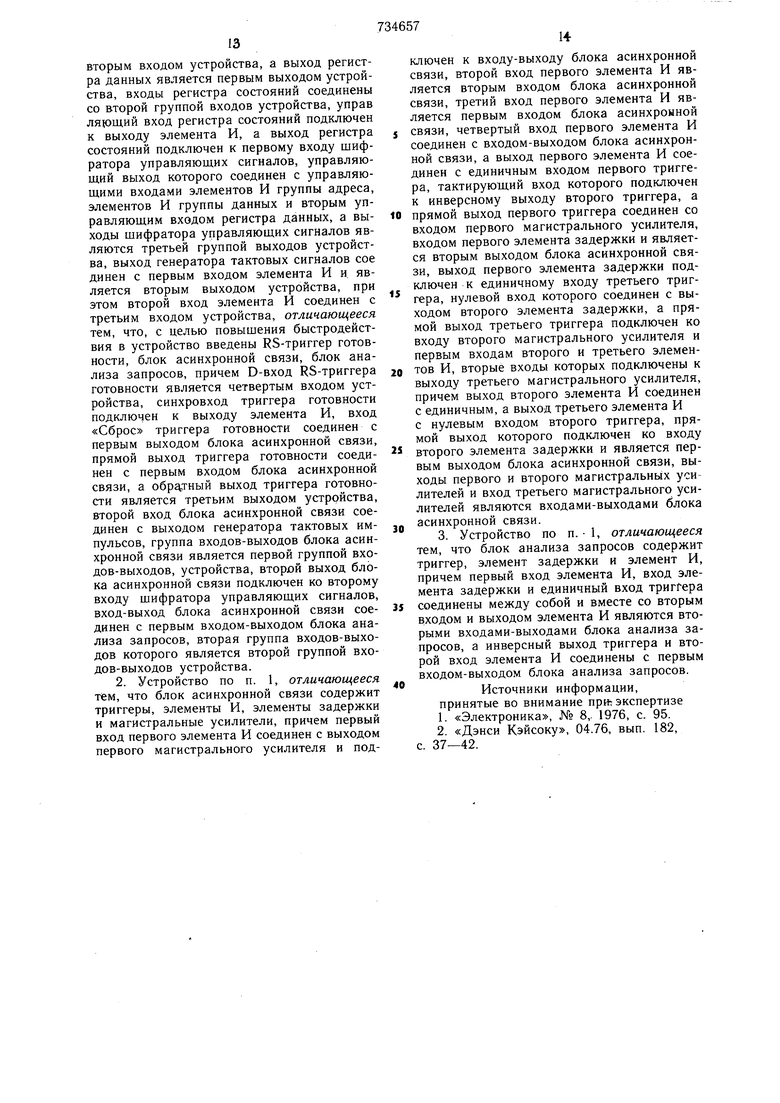

Блок 9 содержит первый второй и третий элементы 11. 14 и 15 И. Первый и второй элементы 12 и 13 задержки. Первый, третий и второй триггеры 16, 17 и -18. Первый второй и третий магистральные усилители 19. Блок 10 анализа запросов доступа к магистрали обеспечивает организацию связи и обмен информацией в режиме активного доступа периферийных устройств к интерфейс0ной магистрали.

Блок 10 содержит элемент 20 задержки, элемент 21 И, триггер 22.

Устройство микропроцессорной связи использует следующие сигналы микропроцессора (8080. фирма «Интел). А 15- -0 -адресные, указывающие адрес ячейки памяти и.ти устройства ввода-вывода;

Д-7-ЬО -данных, предназначенные для передачи команд информации,

0 состояний;

Синхр. - синхронизирующий, указываюший начало каждого машинного цикла микропроцессора; Прием -указывающий, что шины данSных Д 7-ьО находятся в режиме приема информации в микропроцессор;

Готов-указывающий микропроцессору, что на , щинах данных Д имеется входная ин0формация;

Прер.-прерывание;

Ф1,Ф2 -двухфазные тактирующие сигналы.

5

Сигналы состояний

микропроцессора на языках обозначены русском и английском соответственно. П.ЗП.Прер.

JNTA Запись-Вывод

WO Вывод

OVT

JNP Ввод

Чтение(памяти)

MEMR А 15ч-0

Д 7-4-0

Синхр.

SINC Прием

DBIN

READY Готов Прер.

JNT

Для связи с внешними устройствами и устройствами памяти использованы следующие сигналы:

АДР - адресное, указывающие адрес ячейки памяти или периферийного устройства;

ИНФ - информационные, служащие для передачи данных, команд, состояний и др.;

ЧТП - чтение, указывающее, что производится считывание информации (ко7

манд, данных и т. д.) из устройств памяти;

ЗАП-запись, указывающая, что производится ввод информации в устройство памяти;

ПРМ - прием, указывающий, что производится считывание информации из устроств ввода-вывода; ВДЧ выдача, указывающая, что производится запись информации в устройство ввода-вывода; РПР - разрешение прерывания; ЗПР - запрос прерывания; ЗМА - занятость, указывающая активным устройствам, подключенным к интерфейсной магистрали, что в данный момент осуществляется сеанс связи; ВПЛ - выполнение, исполнительный сигнал на выполнение операций в соответствии с управляющими сигналами; ОТВ - ответ, указывающий, что указанная

операция выполнена; ЗДМ - запрос доступа к магистрали; РДМ - разрешение доступа к магистрали; ПЗМ - подтверждение запроса магистрали. Предлагаемое устройство для связи и обмена информацией по интерфейсной магистрали обеспечивает программный режим обмена под воздействием микропроцессора, режим организации связи и обмена информацией по прерыванию, и режим активного доступа периферийных устройств к интерфейсной магистрали.

В начале каждого мащинного цикла обращения к памяти или периферийным устройствам в такте Т 1 микропроцессор вырабатывает синхронизирующий сигнал Синхр,. поступакэщий на конъюнктор 1. В этом же такте микропроцессор устанавливает на адресных шинах А 15Ч-0 код адреса, а на шинах данных ч- состояния микропроцессора (фиг. 4). В такте Т 2 по наличию Ф 1 на конъюнкторе 1 формируется сигнал, соответствующий логическому условию Синхр. Ф 1. Выходной сигнал с конъюнктора 1 устанавливает триггер 6 в единичное состояние (соответствующее состояние неготовности) и обеспечивает занесение в регистр 5 кода состояния микропроцессора с шин данных - О.Сигналы состояния микропроцессора с выхода регистра 5 поступают на шифратор 8 управляющих сигналов. С нулевого выхода триггера б на вход Готов микропроцессора выдается сигнал неготовности, по которому микропроцессор может войти в режим ожидания, а с единичного выхода триггера 6 на блок асинхронной связи 9 поступает сигнал, указывающий на требование микропроцессора к обмену информацией. По этому сигналу блок 9 ПРОИЗВОДИТ анализ логического условия ЗМАПЗМ 1. Выполнение этого условия указывает, что интерфейсная магистраль не занята, т. е. другие активные устройства, подключенные к магистрали, не

производят в данный момент обмен информацией и нет разрешения на пользование магистралью. Если приведенное условие в момент поступления Ф 2 выполняется, блок 9 выдает в интерфейсную магистраль «свой сигнал занятости ЗМА и стробирующий сигнал на шифратор 8. Шифратор 8 в зависимости от кода, поступающего из регистра 5, формирует один из управляющих сигналов (ЧТН, ЗАП, ПРМ, ВДЧ, РПР), выдаваемый в интерфейсную магистраль, а также осуo ществляет подключение к шинам АДР интерфейсной магистрали адресных сигналов. микропроцессора. Тем самым производится выбор адресуемой ячейки памяти или внешнего устройства, кроме того, в режиме «Запись, «Выдача, (ЗАП, ВДЧ), к

шинам ИНФ интерфейсной магистрали подключаются сигналы данных Д 154-0, а в режимах «Чтение, «Прием, (ЧТН, ПРМ) к шинам ИНФ подключаются информационные входы регистра 4. Через время задержQ ки TI блок 9 выдает исполнительный сигнал ВПЛ (выполнение). По сигналу ВПЛ адресованное периферийное устройство или устройство памяти в режимах «Запись, «Выдача, производят прием информации, и отвечают сигналом ответа ОТВ, а в режимах

5 «Чтение, «Прием выдают на шины ИНФ информационные сигналы и сопровождают их сигналом ОТВ, сигналы ИНФ выдаваемые внешними устройствами на фиг. 4... фиг. 6 заштрихованы.

g Приняв сигнал ОТВ, устройство производит сброс триггера б, тем самым микропроцессору выдается сигнал «Готов. В режимах «Чтение, «Прием по сигналу ОТВ производится также занесение информационных сигналов в регистр 4. Через время

5 задержки тг необходимое для занесения информации в регистр 4, блок 9 устройства осуществляет сброс сигнала ВПЛ. Внешние устройства на сброс ВПЛ отвечают сбросом ОТВ (если это источник, то сбрасываются также информационные сигналы). Блок 9 после сброса сигнала ОТВ производит отключение сигнала занятости ЗМА, а также адресных АДР, информационных ИНФ и управляющих (ЧТН, ЗАП, ПРМ, ВДЧ, РПР) сигналов, тем самым устройство полностью

5 отключается от интерфейсной магистрали и она теперь может быть использована другими активными устройствами для обмена данными.

Микропроцессор анализирует сигнал «Готов по заднему фронту фазы Ф 2. Если к этому времени триггер 6 не сбрасывается блоком 9 в состояние «Готов, то микропроцессор входит в режим ожидания TW, в котором готовность анализируется аналогичным образом. Вход микропроцессора в режим ожидания происходит при работе с медленно действующими внещними устройствами, которые сигнал ответа ОТВ выдает после прохождения фазы Ф 2 в такте Т 2.

9

Количество актов ожидания микропроцессора в этом случае не ограничивается.

Прием микропроцессором информации, занесенной в регистр 4 осуществляется в такте Т 3 при наличии сигнала «Прием (которым производится клапанирование информационных выходов регистра 4) и тактового сигнала Ф 1.

Таким образом, наличие триггера готовности 6 и блока 9 синхронной связи обеспечивает такую организацию связи микропроцессора с внешними устройствами, при которой по требованию микропроцессора к обмену на шине «Готов устанавливается сигнал неготовности и только после того, как устройство закончит цикл обмена в асинхрон ном режиме микропроцессору выдается сигнал готовности. Тем самым время между требованием микропроцессора к обмену и анализом готовности адресуемого внешнего устройства не регламентируется.

Из приведенных на фиг. 4, 5 диаграмм следует, что устройство занимает интерфейсную магистраль только на время наличия сигнала ЗМА (на время цикла обмена), выдаваемого устройством, все остальное время магистраль свободна и может быть использована для обмена информацией другими активными устройствами, подключенными к ней.

В случае, если микропроцессор производит обращение к памяти или устройству ввода-вывода, а интерфейсная магистраль занята (другое активное устройство осуществляет цикл связи), то аналогично взводится триггер 6 и микропроцессору выдается по шине «Готов сигнал неготовности, а блок 9 устройства осуществляет анализ «занятости интерфейсной магистрали (анализируется сигнал ЗМА, установленный внешним устройством). В этом случае микропроцессор входит в режим ожидания TW как и при неготовности внешнего устройства. Как только магистраль освобождается (внешний ЗМА 0), устройство устанавливает свой сигнал занятости ЗМА и организует сеанс связи в соответствии с диаграммой, приведенной на фиг. 6.

Организация прерываний микропроцессора осуществляется следующим образом.

Внешнее устройство, требующее прерывания программы, выдает в интерфейсную магистраль по шине ЗПР сигнал запроса прерывания. В устройстве этот сигнал транслируется на вход ПРЕР. микропроцессора. После выполнения очередной команды микропроцессор воспринимает сигнал ПРЕР. (если вход ПРЕР. не заблокирован) и во время обращения за следующей командой в коде состояний устанавливает сигнал П.Зп.ПРЕР. - подтверждение запроса прерывания. Устройство в соответствии с приведенными диаграммами организует цикл связи по интерфейсной магистрали. Однако в этом случае шифратор 8 в соответствии

10

с кодом состояния, принятым в регистр 5, формирует управляющий сигнал РПР - разрешение прерывания. Сигнал РПР проходит последовательно через все инициативные периферийные устройства. Ближайшее 5 периферийное устройство, выдавшее запрос на прерывание, воспринимает сигнал РПР, блокирует его дальнейшее прохождение и выдает на информационные шины ИНФ код вектора прерывания, сопровождая его сигналом ответа ОТВ. Устройство, аналогично

® описанному в режиме программного обмена, осуществляет занесение кода вектора прерывания в регистр 4, далее микропроцессор по условию Готов, Прием Ф 1 производит прием кода вектора прерывания и переходит

5 на программу обслуживания данного периферийного устройства.

Работа устройства в режиме организации связи и обмена информацией с активным доступом к интерфейсной магистрали осуществляется следующим образом.

0 Активное периферийное устройство, требующее управления магистралью, выставляет сигнал ЗДМ (запрос доступа к магистрали). Блок 10 устройства при наличии сигнала ЗДМ выдает сигнал РДМ (разрешение доступа к магистрали). Линия РДМ последовательно проходит через все активные устройства, подключенные к магистрали, и производит выбор ближайшего внешнего устройства, выдавшего сигнал ЗДМ, Выбранное активное устройство блокирует

0 дальнейшее прохождение РДМ, сбрасывает свой ЗДМ и выдает сигнал «Подтверждение запроса магистрали - ПЗМ. Блок 10 устройства фиксирует сигнал ПЗМ и выдает на блок 9 известительный сигнал, который блокирует установку сигнала ЗМА устfройством и одновременно сбрасывает сигнал РДМ. После этого внешнее устройство по выполнению условия ЗМА-РДМ 1 устанавливает свой ЗМА, сбрасывает ПЗМ и осушествляет цикл связи. Сброс ПЗМ вызывает снятие блокирующего сигнала, поступающего с блока 10 на блок 9.

Блокирование сигналом ПЗМ возможности использования устройством в данный момент интерфейсной магистрали осуществлено в целях разнесения во времени кон фликтнсй ситуации, когда внешнее и предлагаемое устройства пытаются одновременно использовать магистраль.

Блок 9 асинхронной связи работает следующим образом.

0

в исходном состоянии триггеры 16, 17 и 18 находятся в нулевом состоянии. Элемент 11 И анализирует состояние входных сигналов и переключается при выполнении условия - ЗМАФ.2Готов ПЗМ 1, т. е. когда интерфейсная магистраль не занята (ЗМА), триггер готовности находится в состоянии «не готов (Готов), а его значит, что микропроцессор требует обращения к интерфейсной магистрали, активные внешние устройства в ближайший момент времени не используют интерфейсную магистраль (ПЗМ). Переключение конъюктора 11 вызывает установ триггера 16 в единичное состояние, при этом в интерфейсную магистраль выдается сигнал занятости магистрали ЗМА, а на шифратор 8 управляюш,их сигналов подается разрешающий сигнал, по которому шифратор 8 выдает в интерфейсную магистраль один из управляющих сигналов, а также осуществляет управление по подключению к интерфейсной магистрали адресных и информационных сигналов. Через время задержки ti (элемент 12 И взводится триггер 17. В интерфейсную магистраль выдается сигнал выполнения ВПЛ. Адресуемое внешнее устройство по сигналу ВПЛ осуществляет выполнение предписываемой операции и отвечает сигналом ответа ОТВ. Получив сигнал ответа на входе элемента 14 И, выполняется условие ВПЛ-ОТВ 1. Элемент 14 И переключается и устанавливает триггер 18 в единичное состояние. Сигналом с единичного выхода триггера 18 сбрасывается триггер готовности Н и через время задержки тга сбрасывается триггер 17, а следовательно, снимается и сигнал ВПЛ. Внешнее устройство на сброс ВПЛ отвечает сбросом ОТВ. При выполнении условия ВПЛОТВ 1 переключается элемент 15 И и устанавливает триггер 18 в нулевое исходное состояние. Это в свою очередь вызывает сброс по входу с триггера 16 и соответственно съем сигнала ЗМА, (Шифратор 8 произведет отключение от интерфейсной магистрали управляющих, адресных и информационных сигналов). На этом цикл асинхронной связи при обмене информацией по интерфейсной магистрали заканчивается. Блок 10 работает следующим образом. Внешнее устройство, требующее доступ к интерфейсной магистрали, выдает сигнал запроса доступа к магистрали (ЗДМ). Элемент , 20- И по выявлении условия ЭДМПЗМ 1 переключается и в интерфейсную магистраль выдается сигнал РДМ разрещения доступа к магистрали. Внешнее активное устройство, получив сигнал РДМ, отвечает сигналом подтверждения запроса магистрали ПЗМ. По сигналу ПЗМ триггер 21 устанавливается в единичное состояние, а элемент 20 И производит сброс сигнала РДМ. С нулевого плеча триггера 21 на элемент 11 И блока 9 подается сигнал блокировки, запрещающий использование устройством интерфейсной магистрали. Далее внешнее устройство анализирует условие РДМЗМА 1 и при его выполнении устанавливает свой ЗМА, сбрасывает ПЗМ и организует цикл связи по интерфейсной магистрали. После сброса ПЗМ через время задержки тз производится установ триггера 22 в исходное (нулевое) состояние, тем самым снимается блокирующий сигнал, поступающий на блок 9. Наличие задержки гз указывает на то, что съем сигнала блокировки необходимо производить после окончания переходного процесса по установлению сигнала ЗМА, выданного внешним устройством. Предлагаемое устройство обеспечивает такую структуру обмена данными, при которой интерфейсная магистраль занята только на время цикла связи, а в промежутках между циклами обращения устройство осуществляет отключение сигналов микропро цессора от интерфейсной магистрали и в это время она может быть использована для передачи данных другими активными устройствами. Во время выполнения внешним устройством цикла обмена микропроцессор может производить внутренние операции, связанные с обработкой данных, формированием адреса обращения и др. В предложенном устройстве, если микропроцессор в ходе выполнения команды производят обращение по магистрали к памяти или устройствам ввода-вывода, а магистраль занята (другое активное устройство осуществляет цикл обмена), то микропроцессор входит не в режим «Захват, а в режим ожидания, аналогичный тому, который имеет место при неготовности внешнего устройства. Как только магистраль освобождается, устройство осуществляет цикл обращения. Кроме того, устройство обеспечивает возможность построения интерфейсной магистрали различной длины и конструкции, а также подключение к ней внешних устройств различного быстродействия. Такая организация связи микропроцессора с внешними устройствами и устройствами памяти позволяет в значительной степени повысить производительность микропроцессорных систем, содержащих несколько активных устройств, а также расширить диапазон применения микропроцессорных устройств. Формула изобретения 1. Устройство микропроцессорной связи, содержащее группу элементов И адреса, группу элементов И данных, регистр данных, регистр состояний, шифратор управляющих сигналов, генератор тактовых сигналов, элемент И, причем информационные входы элементов И группы адреса являются первой группой входов устройства, а выходы элементов И группы адреса являются первой группой выходов устройства, информационные входы элементов И группы данных соединены со второй группой входов устройства, а выходы элементов И группы данных являются второй группой выходов устройства, вход регистра данных является первым входом устройства, первый управляющий вход регистра данных соединен со вторым входом устройства, а выход регистра данных является первым выходом устройства, входы регистра состояний соединены со второй группой входов устройства, управ ля1ош,ий вход регистра состояний подключен к выходу элемента И, а выход регистра состояний подключен к первому входу шифратора управляющих сигналов, управляющий выход которого соединен с управляющими входами элементов И группы адреса, элементов И группы данных и вторым управляющим входом регистра данных, а выходы шифратора управляющих сигналов являются третьей группой выходов устройства, выход генератора тактовых сигналов сое динен с первым входом элемента И и является вторым выходом устройства, при этом второй вход элемента И соединен с третьим входом устройства, отличающееся тем, что, с целью повышения быстродействия в устройство введены RS-триггер готовности, блок асинхронной связи, блок анализа запросов, причем D-вход RS-триггера готовности является четвертым входом устройства, синхровход триггера готовности подключен к выходу элемента И, вход «Сброс триггера готовности соединен с первым выходом блока асинхронной связи, прямой выход триггера готовности соединен с первым входом блока асинхронной связи, а обратный выход триггера готовности является третьим выходом устройства, второй вход блока асинхронной связи соединен с выходом генератора тактовых импульсов, группа входов-выходов блока асинхронной связи является первой группой входов-выходов, устройства, второй выход блока асинхронной связи подключен ко второму входу шифратора управляющих сигналов, вход-выход блока асинхронной связи соединен с первым входом-выходом блока анализа запросов, вторая группа входов-выходов которого является второй группой входов-выходов устройства. 2. Устройство по п. 1, отличающееся тем, что блок асинхронной связи содержит триггеры, элементы И, элементы задержки и магистральные усилители, причем первый вход первого элемента И соединен с выходом первого магистрального усилителя и подключен к входу-выходу блока асинхронной связи, второй вход первого элемента И является вторым входом блока асинхронной связи, третий вход первого элемента И является первым входом блока асинхронной связи, четвертый вход первого элемента И соединен с входом-выходом блока асинхронной связи, а выход первого элемента И соединен с единичным входом первого триггера, тактирующий вход которого подключен к инверсному выходу второго триггера, а прямой выход первого триггера соединен со входом первого магистрального усилителя, входом первого элемента задержки и является вторым выходом блока асинхронной связи, выход первого элемента задержки подключен к единичному входу третьего триггера, нулевой вход которого соединен с выходом второго элемента задержки, а прямой выход третьего триггера подключен ко входу второго магистрального усилителя и первым входам второго и третьего элементов И, вторые входы которых подключены к выходу третьего магистрального усилителя, причем выход второго элемента И соединен с единичным, а выход третьего элемента И с нулевым входом второго триггера, прямой выход которого подключен ко входу второго элемента задержки и является первым выходом блока асинхронной связи, выходы первого и второго магистральных уси лителей и вход третьего магистрального усилителей являются входами-выходами блока асинхронной связи. 3. Устройство по п. - 1, отличающееся тем, что блок анализа запросов содержит триггер, элемент задержки и элемент И, причем первый вход элемента И, вход элемента задержки и единичный вход триггера соединены между собой и вместе со вторым входом и выходом элемента И являются вторыми входами-выходами блока анализа запросов, а инверсный выход триггера и второй вход элемента И соединены с первым входом-выходом блока анализа запросов. Источники информации, принятые во внимание при; экспертизе 1.«Электроника, № 8,. 1976, с. 95. 2.«Дэнси Кэйсоку, 04.76, вып. 182, . 37-42.

Фш.1

На ноньюпктор влока- Ог

Гл

Фё

а от триггера 6

отВлоко iO

/fSflOfpt/ в

fll

ЗМА.

19

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения микропроцессора с периферийными устройствами | 1987 |

|

SU1434440A1 |

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Каркас для размещения вдвижных блоков памяти | 1979 |

|

SU911751A1 |

| Устройство для сопряжения магистрали эвм с магистралью внешних устройств | 1984 |

|

SU1229765A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

iZ

На ЬкодК триггера 6

ВДЛ

ОТ5

i9

J

ш.

фиг. г

Фиг.5

Ч)

%

Авторы

Даты

1980-05-15—Публикация

1978-01-04—Подача