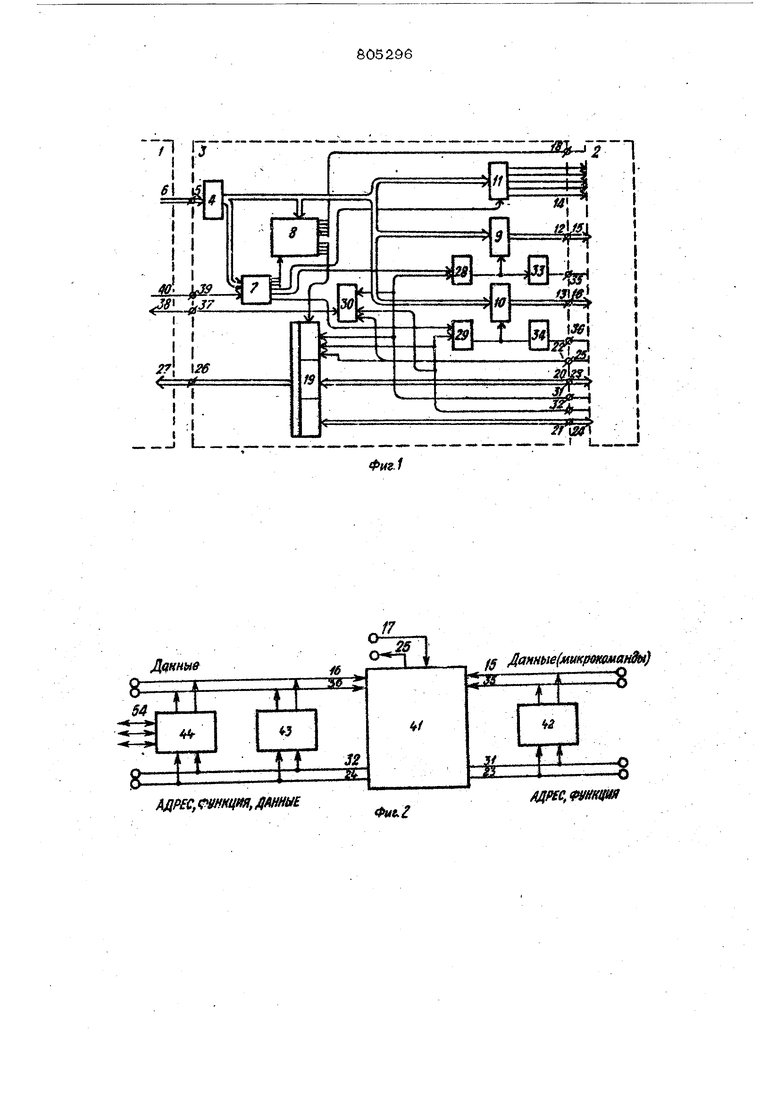

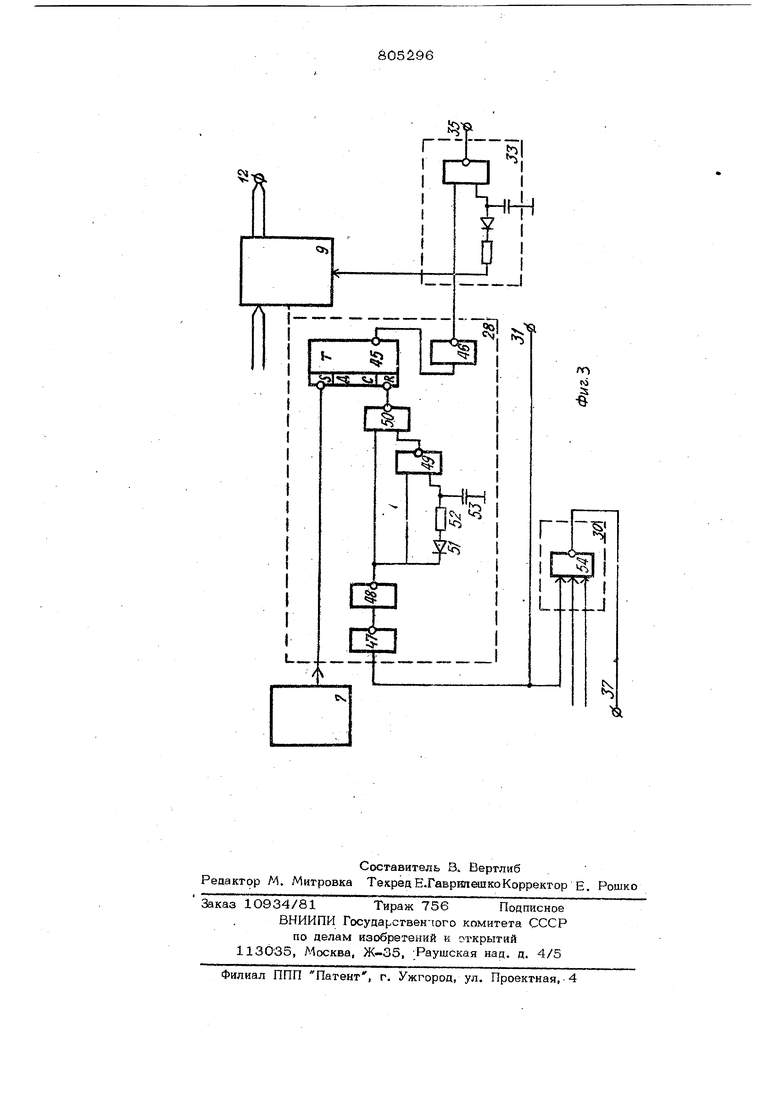

Изобретение относится к вычислительной технике и может быть использовано для сопряжения авук электронно- ычнсли тельных машин, например при отладке одной из них. Известны устройства цля сопряжения ведущей ЭВМ (обычно мини-ЭВМ). с ведомой ЭВМ, например микро-ЭВМ, для отладки программного обеспечения послец ней, содержащие схемы логического управления, переключатели, элементы памяти, и специфицированы на определенный тип микропроцессора ведомой ЭВМ lj. Однако использование подобных усг, ройств сопряжения предполагает наличие отлаженной аппаратуры микропроцессора, запоминающего устройства к блоков ввода-вывода ведомой ЭВМ, вследствие чего область их применения ограйичена. В основном они используются для отладки программного обеспечения серийных микро-ЭВМ. Наиболее близким по текнической сущ ности к предлагаемому является устройство сопряжения ведущего и ведомого устройств , содержащее блок адресации и аеши(|)рации, блок памяти, коммутатор, блок обработки асинхронных событий, блок контроля и клапан, ин4я рмацирнныв входы .которого являются входами устройства сопряжения, связанными с шиной ввода-вывода В9аущ.его устройства, а выходы кЛапана соединены с первыми входами блока адресации и дешифрации и-блока памяти, первые выходы которого подключены к выходам устройства . сопряжения, связанным с ведомым устройством, при этом вторые выходы блогка памяти соединены с первыми входами коммутатора, вторые входы которого подключены ко входам устройства сопряжения, связанным с шинами вывода и состояния ведомого устройства, а выходы коммутатора соединены с выходами устройства сопряжения, связанными с шиной ввода-вывода ведуцего устройства. Входы блока обработки асинхронных событий соединены со входами устройства сопря-. 38 Ж8НИЯ, связанными с шиной состояния вецомого усгройства, а выход его соединен с выкодом устройства сопряжения, связанным со входом шины адресацииуправления ведущего устройства. Второй вход блока адресации и двши( соединен со входом устройства сопряжения, связанным с выходом шины ааресации управления ведущего устройства, а блок контроля соединен с шинами адресации ввоца-«ывода ведущего устройства и бло ком обработки асинхронных событий. Это устройство сопряжения в основно используется для осуществления режима диагностики ведомого устройства. При этом производится следующая последовательность операций: сигналом ведущего устройства ведомое устройство выводится из рабочего режима, производится заполнение памяти устройства сопряжения, содержимое которой вызовет, в дальнейшем выполнение определенной диагностической операции., после чего ведущее уст poijCTBo выдает Сигнал работа, по кото рому ведомое устройстгто с помощью боль шого числа логических схем, содержащих в нем, осуществляет выдачу ответа на по лученную из блока памяти команду. Полу ченная ответная информация извлекается из определенных ячеек блока памяти и обрабатывается ведущим устройством. , Указанная последовательность должна повторяться для каждого акта взаимодействия ведущего и ведомого уст|)ойства. При этом время, необходимое для подготовки команды запроса, и анализ ответной информации составляют существенно большую величину, чем время, необходимое для выполнения ведомым устройством требуемой команды, что не позволяет вести групповой межмашинный обмен информацией в рнтме работы, присущем ведомому устройству 2. Недостатком известйого устройства является его низкое быстродействие, т. с. любое взаимодействие между ведущей и ведомой ЭЬМ осуществляется посредством многократного обращения к бло ку памяти устройства сопряжения. Кроме того, сложность известного устройства и наличие дополнительной нерегулярной логической схемы, необходимой для связи устройства сопряжения с ведомым устройством, явпяются причиной того, что условия автономной работы ведомого устройства отличаются от условий работы его совместно с ведущим устройством, что, в свою очередь, снижает достовер- ность обмеиа информацией межцу веаущи и ведомым устройствами. Цель изобретения - повышение быстродействия устройства при группозом обмене информацией между ведущей и ведомой ЭВМ. Поставленная цель аостигается тем, что в устройство для сопряжения двух вычислительных машин содержащее узел адресации и дешифрации, первый вход которого является управляющим входом устройства, память, первый выход которой является соответствующим выходом из группы управляющих выходов устройства, элемент И, вход которого является первым информационным входом устройства, а выход подключен, к входу памяти и второму входу узла адресации и дешифрации, первым выходом соединенного со вторым входом памяти, узел формирования выходных управляющих сигналов и коммутатор, выходы которых являются, соответственно, управляющим и инфо{ лационным выходами устройства, а первые, вторые и третьи входы - соединены соответственно с входом сигнала состояния устройства и первым и вторым входами синхронизации устройства, четвертый, пятый и шестой входы комму атора подключень соответственно ко второму выходу памяти и второму, и третьему информационным входам устройства, введены три элемента И, два формирователя импульсов и два -элемента задержки, причем второй, третий и четвертый выхоцы узла адресации и дешифрации подключены. соответствен1|о к управляющему входу второго элемента И и первым входам фор- мирователей импульсов, вторые входы которых соединены соответствен.но с первым и вторым входами синхронизации устройства, а выходы соответственно - с управляющими входами третьего и четвертого элементов И и через соответствующие элементы задержки - с первым и вторым выходами синхронизации устройства, информационные входы второго, третьего и четвертого элементов И соединены с выходом первого элемента И, выход второго элемента И является соответствующим выходом из группы управляющих выходов устройства, выходы третьего и четвертого элементов И являются , соответственно, вторым и третьим информационными выходами устройства, На фиг, 1 приведена блок-схема предлагаемого устройства; на фиг. 2 -структурная схема ведомой ЭВМ (чертой помечены шнны и линии микро-ЭВМ); на 5В фиг. 3 - функциональная схема формирователей импульсов. Нлок-схема устройства (фнг. 1) соаер жит ведущую 1 и ведомую ЭВМ 2, устрой ство 3 зля сопряжения, вктпочающеа элемент 4 И, соединенный первьвис инфор- мационньсм вкодом 5 устройства с шиной 6 вьшода информации ведущей ЭВМ 1, узел адресации и дешифрации 7, памяп 8, второй, третий и четвертый элементы 9-11 И, соединенные через второй я третий информационные выходы 12 и 13 устройства и управляющие выходы 14, соответственно, с шинами 15 и 16 ьвода и группой управляющих шин 17 ведомой ЭВМ, включающий я управяякшшй выход 18, KCMviMyraTop 19, поакпю 1е11ный через второй и третей информацисшные входы 20 и 21 устройства и вход 22 сигнала состо ия устройства соответственно с шинами 23 н 24 вывода и шиной 25 состояния ведсяиой ЭВМ, а выхоаом через первый информационный выход 26 устройства подключен к шине 27 ввода ведущей ЭВМ, формирователи 28 и 29 импульсов управления, узел ЗО формирования выходных управляющих сипаалов, входы 31 и 32 синхронизации устройства элементы 33 и 34 задержки, выхооы 35 н 36 синхронизации устройства, увравяв- юший выход 37, соединенный с шкндй 38 управления ведущей ЭВМ, и вхоа 39, соединенный с шиной 4О управления ведущей ЭВМ. Усгройство предназначено для работы с ведомой ЭВМ, которая имеет канальную организацию основных внутренних связей и асинхронный характер по выце- ленным каналам.. Ведомая ЭВМ (фиг. 2) включает бяок 41 обработки, модула ПЗУ 42, модули ОЗУ 43, специализированные блоки ввоаа вывода (ВУ) 4 4 через которые весомая ЗВМ связана с внешним объектом Kouf- роля и управления. Устройство работает следующим образом. Рассмотрим работу устройства сопря- жения в режиме отладки вновь раэрабаты ваемой специализированной микро- М. Процесс отладки микропрсшессораой системы, в которой вели2 об.вм вав&ъ разработанных аппаратуриык решеиив/ обычно производится методом иесдеабва тельного приближения, т. в. отладка проходит этап контропь-«справлваае. В режиме отладки следует обеспечив оперативную индикацию, регистрацию 6 корректировку, групповой ввод и вывод информации ПЗУ, ОЗУ, ВУ. Пусть ведущая ЭВМ 1 по отношению к ЭВМ 2 является гт ссивным устройст- вом и отдельныеМассивы ее ЗУ, ПЗУ, ОЗУ,ВУ используются в качестг е ячеек реальных блоков (ПЗУ, ОЗУ, ВУ/ ведомой микроЭВМ. После (-(впуска ЭВМ 2 по шинам 23 выставляет начальный адрес, который сопровождается синхросигналом, поступающим на вход 31, и через узел ЗО. воспринимающийся ведущей ЭВМ 1, как запрос на обслуживание, ЭВМ 1 считывает Содержимое слова запроса, формирует по нему начальный адрес соответствующего массива,в данном случае ПЗУ, переключает коммутатор 19 на нужный вход. Для этого ведущая ЭВМ 1 выставляет через вход 5 и элемент 4 И слово управления устройством сопряжения, которое дешифруется в узле 7, и переключает элементы памяти 8, управляющие коммутатором 19. Поспь этого ЭВМ 1 через ком- мутатор 19 и вход 20 считывает с шины 23 адрес ПЗУ, формирует в массиве ПЗУ исполнительный адрес, по которому считывает информацию и выставляет ее через вкод 5 на. элемент 4 И устрой- ства. Значения старших разрядов информационного слова, являющихся его признаком, после дешифрации в узле 7 поступают на формирователь 28, на второй Вход которого поступает синхросигнал со входа 31. Сигнал с выхода формирователя 28 открывает элемент 9 И. При этом запрашиваемая от ЭВМ 1 информация (без признака) с выхода элемента 4 И, минуя память 8 через элемент 9 И, поступает через выход 12 на шину , 15 ввода. Для устранения влияния переходных процессов на шине 15 через элемент задержки 33 выдается синхросигнал на выход 35, подтверждающий пригодность информации и воспринимаемый ведомой ЭВМ 2 как выполнение запроса. После приема информации с шяны 15 микро-ЭВМ 2 снимает синхросигнал на входе 31, Б результате чего элемент ® формирователь 28 закрывается и шина 15 освобождается. Таким образом, в каждом цикле своей работы микро-ЭВМ 2 считывает из массива ПЗУ ЭВМ 1 информацию, воспринимаемую как команду. По ходу программы у ЭВМ 2 возникает потребность обращения к своему ОЗУ, которое выпол няется одной командой. В этом случае в одном цикле микро-ЭВМ 2 выставляет 76 в устройство не один, а два aanpocia: обращение к ОЗУ для завершения текущей команды и обращенке к ПЗУ аля выборки следующей команаы. Ведущая ЭВМ 2 считывает слово запроса (как указано выше), по которому определяет очередность удоаяетворения запросов. В ааяяом случае пе|жым удовлетворяется запрос ОЗУ. Поэтому переключая коммутатор 19, ЭВМ 1 считывает (шформапто с шины 24 (адрес ОЗУ, операцию чтение или запись, а в случае записи и ааяные) Удовлетворение запроса по операции чтения ячейки массива ОЗУ производится в ЭВМ 1 аналогично чтению ксманды из массива ПЗУ с той лишь разницей, что выдаваемая ЭВМ 1 . информация через элемент 4 И поступает на элемент 1О И, управление котог рым производится через узел 7, на который поступает признак ОЗУ, и формирователь- 29. Через открытый элемент Ю И информация поступает по шине 16 в ЭВ,М 2. Синхросигнал с выхода элемента 34задержки, поступая «а выход 36, указывает на пригодность данных на шине 16. Происходит считывание этих данных; ЭВМ 2. В случае операции записи ЭВМ 1 с шины 24 через коммутатор 19 считываат и данные для записи в ОЗУ, кроме разрядов операции и адреса ОЗУ. Сформировав исполнительный адрес ОЗУ, ЭВМ 1 записывает туда принятые данные после чего она через элемент 4 И на узел 7 признак ОЗУ. Деши4ч:)оваиш 1й сигнал с вы хода узла 7 через формирователь 29 и зле мент 34 задержки поступает на выход 36, указывая 3BMi 2 на удовлетворение ее запроса. После приема синхросигнала с выхода 36 ЭВМ 2 снимает сигнал

запроса со входа 32. При этом формирова1| вль 29 закрывает элемент 1О И, освобождая шину 16, и приводит в исходное состояние элемент 34 задержки. Если запрос к ПЗУ (вход 31) не удовлетворен, ЭВМ 1 выполняет действия по его отработка, г. 9. извлекает следующую команду ив ПЗУ, аналогично ранее рассмотренному случаю начального пуска Для упра1элвния микро-ЭВМ в устройстве выделены иве группы управляющих сигналов: импульсные и потенциальные. К- первым относятся пуск однократный , останов, а ко вторым - захват шин, работа-шаг и др. Импульсные сигналы получаются стробированием данных, поступающих сэлемента 4 И через элемент 11 И и выходы 14 и 18 на шины 17, в то ъремя как потенциальные сигнапы.

а время запроса и передачи, ответной информации через устройство составляет менее 1 мкс, что, по крайней мере, ллень ше, чем в известном устройстве, использующем блок памяти в качестве буфера. Устройство сопряжения наиболее выгодно использовать тогда, когда в ЗУ ведущей ЭВМ заносится массив ПЗУ. Применение ; в ведущей ЭВМ канала прямого доступа к памяти позволяет довести общее время обращения и выдачи из ПЗУ через устройство сопряжения до 1-1,5 мкс. Это Speмя соразмерно с циклом работы го ПЗУ.

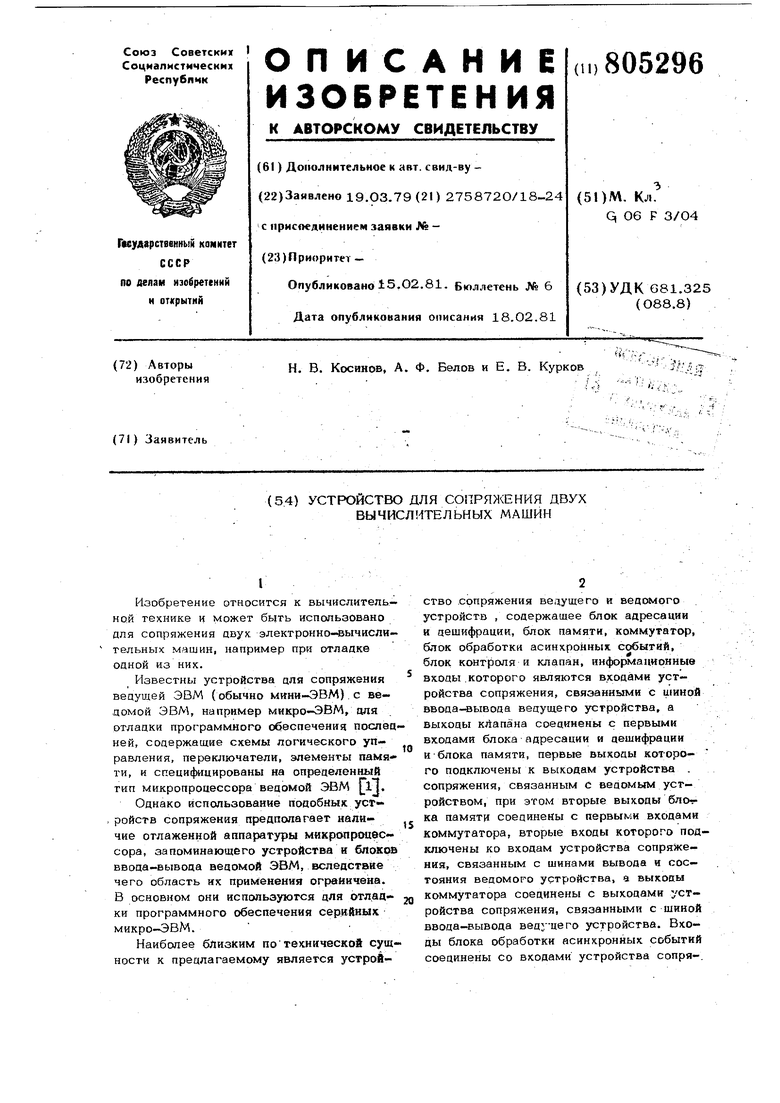

Данное устройство сопряжения может быть использовано и в режиме испытаний блоков ЗУ, интерфейсных блоков разрабатываемой микроб-ЭВМ. Ведущая ЭВМ шлеств с устройством сопряжения обеспе6выцаваемые также через элемент 11 И, сохраняются в памяти 8. Формирователь 28 (29) -фиг. 4 состоит из триггера 45 с выходным инвертором-усипителем 46 и оановибратора, образованного элементами 47-50 И, диодом 51, резистором 52 и конденсатором 53. Формирователь запускается импульсным сигналом, поступающим из узла 7, в резуу1ьтаге чего на инверторе 46 устанавливается уровень , открывающий элемент 9 И. Переключение триггера 45,- а следовательно, и отключение элемента 9 И происходит по положительному фронту сигнала на входе 31 устройства, который сигнализирует о снятии запроса по соответствующей магистрали. Длительность формируемого импульса составляет 2ОО-ЗОО НС. Схемотехника узла 30 обуславливается особенностями ведущей ЭВМ. Для мини-ЭВМ, например М-600О, достаточно обойтись обычной схемой 54 ИЛИ, которая на своем выходе удерживает сигнал запроса к ведущей ЭВМ на протяжении времени присутствия одного из запро- сов в виде потенциального уровня на любом входе. Таким образом, по1 ышение достоверности обмена информацией при использовании предлагаемого устройства сопряжения с еспечивается существенным сокращением объема оборудования (в частности объем памяти уменьшается в 1520 раз). Кроме того, выходные элементы И на шинах и линиях устройства в сторону ведомой микро-ЭВМ, допускаю- щие функцию проводное ИЛИ, не требуют никакого дополнительного оборудов н я для согласования с ведомой ЭВМ, 96 чивают максимальное быстродейсгвке, выдавая на испытываемый блок адрес операции и аанные и считывая контрольные данные. Для обеспечения такого режима следует по-иному подключаться к устройству сопряжения со стороны ведомой ЭВМ (фиг. 2). К выходам 12 и 35, по которым перецаются адрес, данные и операавя, подключаются шины испытываемык блоков ОЗУ, ВУ, (ПЗУ), которые в режиме от.лааки поаключа1отся к шинам 23 и 24 для выдачи информации запроса в ЭВМ 1 К коммутатору 19 для считывания информации из испытуемых; блоков поаключаются те шины, по которым в режиме отладки микро-ЭВМ 2 принимает запрашиваемую информацию. При переходе с режима на режим не трюбуется вводить никаких изменений в схему устройства. Вре менное согласование обеспечивается преж ними схемами управления клапанами и схемами задержки. Формулаизобретения Устройство для сопряжения двух вычислительных машин, содержащее узел адресации и дешифрации, первый вход которого является управляющим входом уст ройства, память, первый выход которой является соответствующим ьыкоасал нэ группы управляющих выходов устройства, элемент И, вход которого является первым информационным входом устройства, а выход подключен к входу памяти и вго- рому входу узла адресации « дешифраоик, первым выходом соединенного со вторым входом памяти, узел формирования выхоа- ных управляющих сигналов и коммутатор, выходы которых являются соответственно управляющим и информационным вы- 6 ходами устройства, а первые, вторые и третьи входы соединены соответственно, с входом сигнала состояния устройства и первым, к вторым гходами синхронизации устройства, четвертый, пятый и шес« той входы коммутатора подключены со ответственно ко eropo viy выходу пвмот и второму, и третьему информанионвым входам устройства, отличающвес я тем, что, с целью повышения быстродействия устройства, в него введены три элемента И, два формирователя импульсов и два элемента задержки, причем бторой, третей и четвертый выходы узла адресации и дешифрации подключены соответственно к управляющему входу второго элемента И и первым ВХОДИМ формирователей импульсов, вторые входы которых соединены соответственно с первым и вторым входами синхронизации уст рйства. а выходы соответственно - с управляющими входами третьего и четвертого элементов И и через соответствующие элементы задержки - с первым к вторым выходами синхронизации устройстве, информационные входы второго, третьего и четвертого элементов И соединены с вы- . ходом первого элемента И, выход второго элемента И является соответствующим выходом из группы управляющих выходов ycTpo teTBa, выходы третьего и четвертого элементов И являются соответственно вторым и третьим И1сформацяоннь1м выходами устройства. Источники информации, принятые во внимание при экспертизе. 1.Авторское свидетельство СССР по заявке J« 2688967, кл. Q Об F 3/О4, 2.Патент США № 3999О53, кл. 235-153 А, опублик. 1976 (прототип).

f J-.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1644150A1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Многоканальное устройство сопряжения | 1976 |

|

SU679973A1 |

АДКС, W«m АННЫ

Авторы

Даты

1981-02-15—Публикация

1979-03-19—Подача