1

Изофетение предназначено для ис- пользования в устройствах шсфровой вычислительйой техники для накопления н вывода информации во внешнее устройства, в частности, для накопления и вывода телеметрической информации о работоспосо бности узлов вычислительных устройств.

Известны устройства для Ы 1вода информаюш, содержащие буферный регистр, входы которого являются входами устройства, регистр выдачи, выходу которого 51ВДЯЮТСЯ выходами, устройства и схемы, обеспечивающие перепись информации из буферного регистра в регистр выдачи, вывод ивформадвн во внешние устройства и ов уление регистров устройства С1 .

Недостатками устройства являютсй его сложность и низкое качество . работы за счет потери информации.

Наиболее близким по технической сушности к предлагаемому является устройство для вывода информации, содержащее

буферную память, выходы которой соеди-, нены со сдвиговым регистром, выходы , сдвигового регистра соединены с входами группы элементов И, выходы которой подключены к входам узла ссшряжения, выходы которого являются выходами ycTpoifcTBa, первый, второй и третий элементы И, память управления и формирователь синхроимпульсов, причем информаотонный Jaxoд памяти управления является входом устройства, выходы . памяти управления цодключены к первым входам первого, второго и третьего элементов И, управляющему входу сдвигового регистра -и вторым входам группы элементов И, рыходы формирователя синхро-импульсов подключены к вторым Екодам первого, BToptTro и третьего элементов И, выходы которых соединены с управляющими входами буферной памяти, сдвигового регистра в памяти управления 12 .

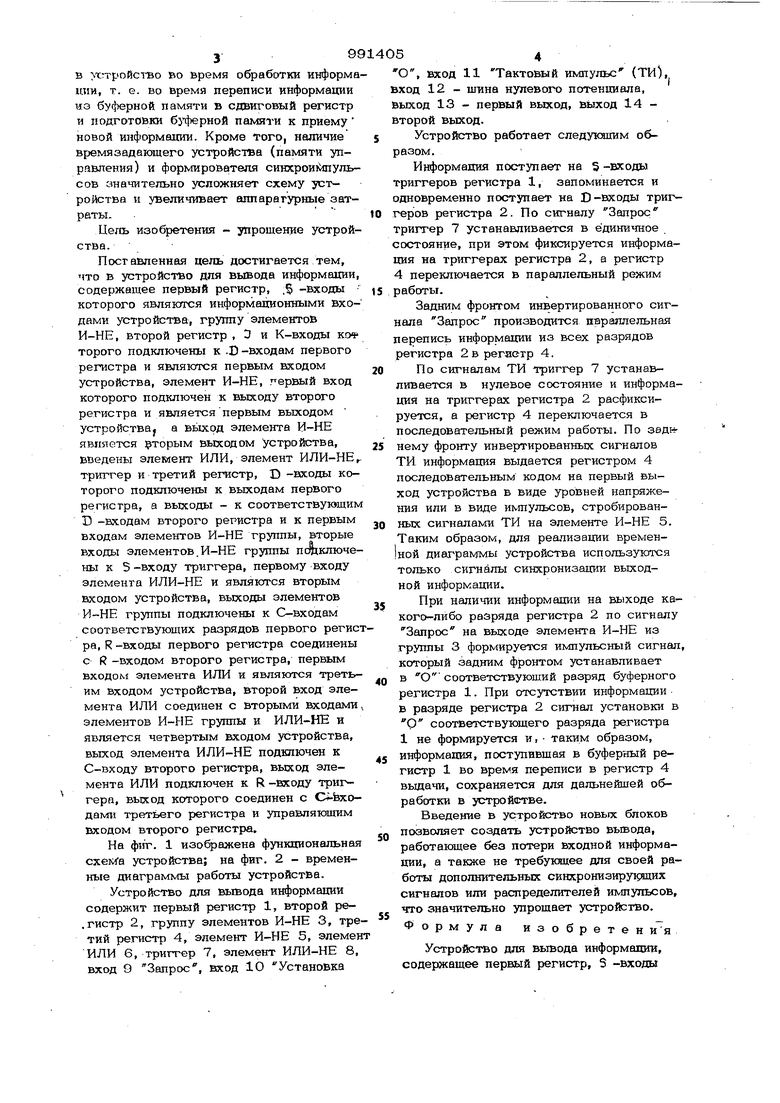

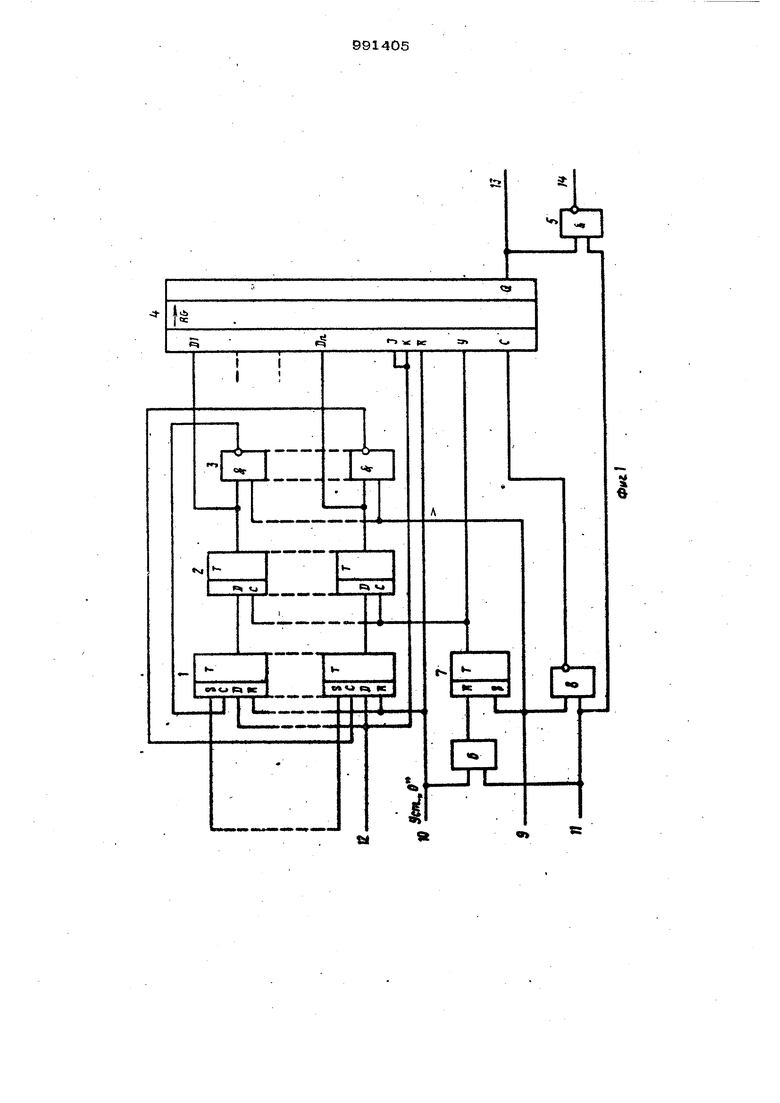

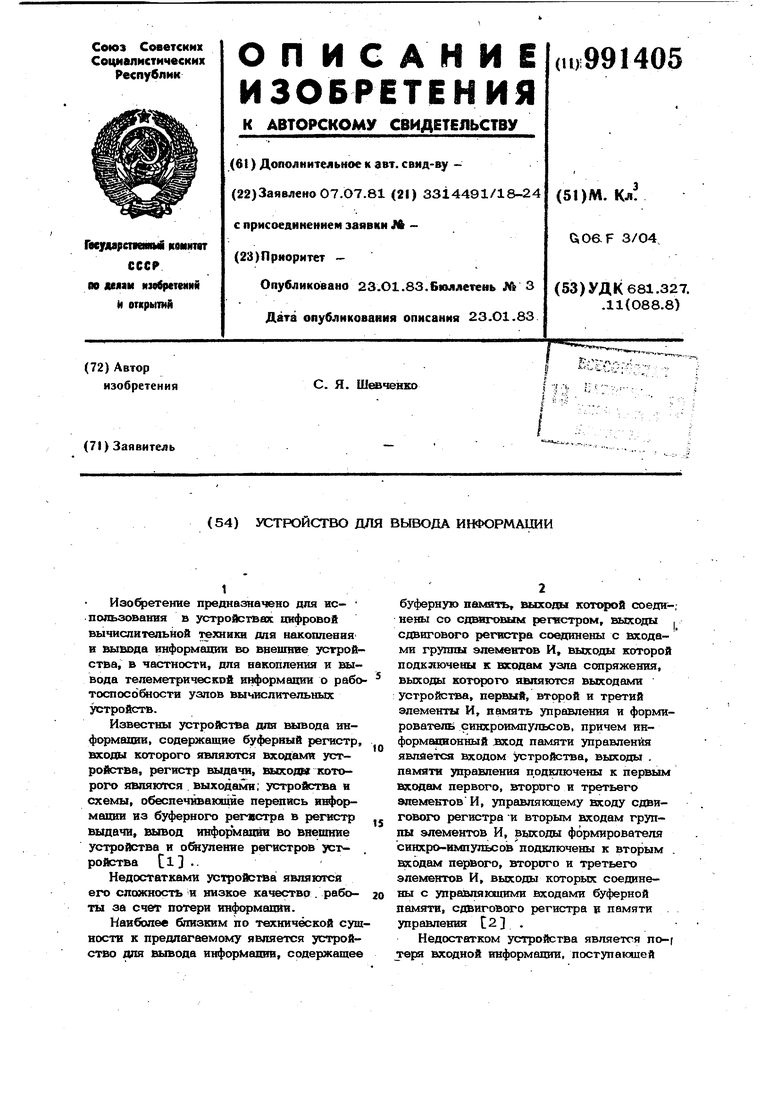

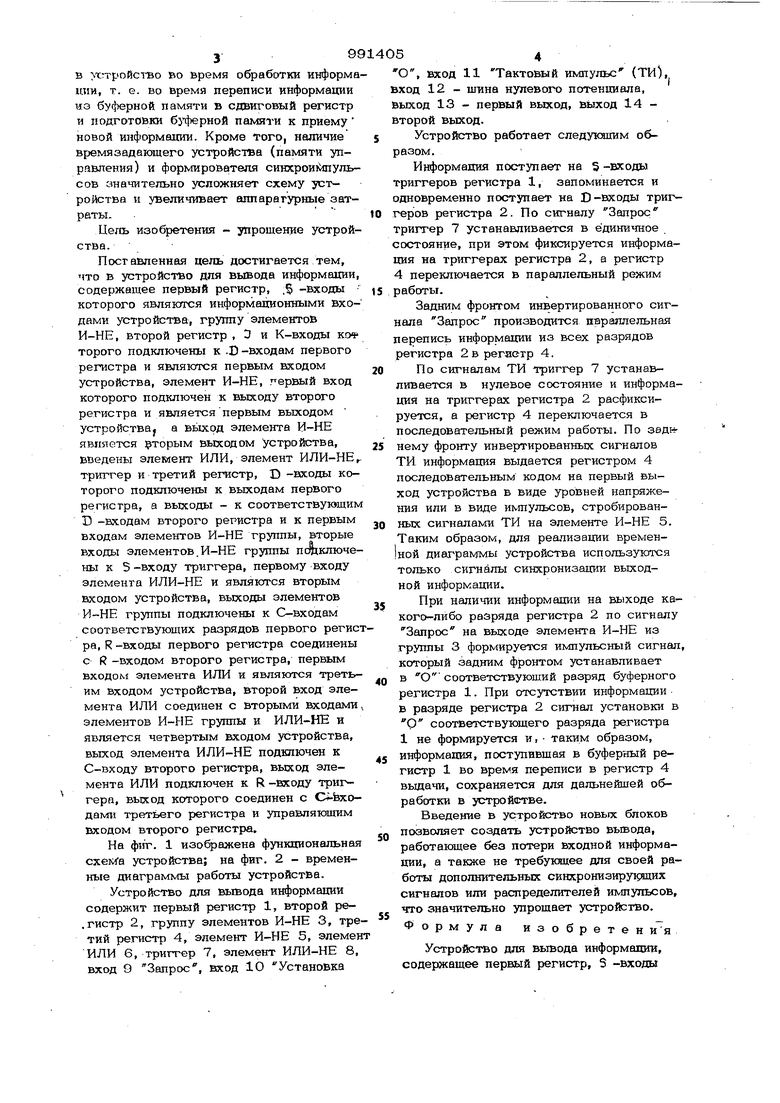

Недостатком устройства является no-f теря входной информации, поступающей 39 в хтройство во время обработки информ Ш1И, т. е. во время переписи информации 43 буферной памяти в сдвиговый регистр и подготовки 6jTl3epHofl памяти к приему новой информации. Кроме того, наличие время задающего устройства (памяти управления) и формирователя сиюсрои1 шуль сов значительно усложняет схему устройства и увеличивает аппаратурные затраты. Цепь изобретения - упрощение устрой ства. Поставленная цель достигается тем, что в устройство для вывода информации содержащее первый регистр, ,5 -входы которого являкггся информационными входами устройства, группу элементов И-НЕ, второй регистр , D и К-входы ко торого подключены к .D -входам первого регистра и являются первым входом устройства, элемент И-НЕ, первый вход которого подключен к выходу второго регистра и являетсяпервым выходом ycтpoйcтвaJ а вьисрд элемента И-НЕ явпяется вторым выходом устройства, введены элемент ИЛИ, элемент ИЛИ-НЕ триггер и третий регистр, D -вкоды которого подключены к выходам первого регистра, а выходы - к соответствующим D -входам второго регистра и к первым входам элементов И-НЕ группы, вторые входы элементов. И-НЕ группы подключе ны к 5 -ВХОДУ триггера, первому входу элемента ИЛИ-НЕ и являются вторым входом устройства, выходы элементов И-НЕ группы подключены к С-входам соответствующих разрядов первого регис ра, R-входы первого регистра соединены с R -входом второго регистра, первьп входом элемента ИЛИ и являются Входом устройства, второй вход элемента ИЛИ соединен с вторыми входами элементов И-НЕ группы и ИЛИ-НЕ и является четвертым входом устройства, выход элемента ИЛИ-НЕ подключен к С-входу второго регистра, выход элемента ИЛИ подключен к R -входу триггера, выход которого соединен с С -Ьходами третьего регистра и управляющим входом второго регистра. На ф1пг. 1 изображена функциональная схема устройства; на фиг, 2 - временные диаграммы работы устройства. Устройство для вывода информации содержит первый регистр 1, второй ре.гистр 2, группу элементов И-НЕ 3, тре тий регистр 4, элемент И-НЕ 5, элемен ИЛИ 6, триггер 7, элемент ИЛИ-НЕ 8, вход 9 Запрос, вход 10 Установка 5 вход 11 Тактовый импульс (ТИ), О ход 12 - шина нулевого потенциала, выход 13 - первый выход, выход 14 второй выход. Устройство работает следукшим образом. Информация поступает на 5 -входы триггеров регистра 1, запоминается и одновременно поступает на D-входы триггеров регистра 2. По сигналу Запрос триггер 7 устанавливается в единичное состояние, при этом фиксируется информация на триггерах регистра 2, а регистр 4 переключается в параллельный режим работы. Задним фронтом инвертированного сигнала Запрос производится пвраялельная перепись информации из всех разрядов регистра 2 в регистр 4. По сигналам ТИ триггер 7 устанавливается в нулевое состояние и информация на триггерах регистра 2 расфиксируется, а регистр 4 переключается в последовательный режим работы. По звдннему фронту инвертированных сигналов ТИ информация выдается регистром 4 последовательным кодом на первый выход устройства в виде уровней напряжения или в виде импульсов, стробированкых сигналами ТИ на элементе И-НЕ 5. Таким образом, для реализации временной диаграммы устройства используются только сигналы синхронизации выходной информации. При наличии информации на выходе какого-либо разряда регистра 2 по сигналу Запрос на выходе элемента И-НЕ из группы 3 формируется импульсный сигнал, который задним фронтом устанавливает в соответствующий разряд буферного регистра 1. При отсутствии информации в разряде регистра 2 сигнал установки в О соответствующего разряда регистра 1 не формируется и, таким образом, информация, поступившая в буферный регистр 1 во время переписи в регистр 4 вьщачи, сохраняется для дальнейшей обработки в устройстве. Введение в устройство новых блоков позволяет создать устройство вывода, работающее без потери входной информации, а также не требующее для своей работы дополнительных синхронизиру1рщих сигналов или распределителей импульсов, что значительно упрощает устройство. Формула изобретен Устройство для вывода информации, содержащее первый регистр, 3 -входы которого являются информациошплми fKOдами устройства, группу элементе И-НЕ второй регистр, 3 и К-входы которого подключены к D -входам первого регистра в являются пррвым входом устройств элемент И-НЕ, первый вхой которого подключен к выходу второго регистра и является первым выходом устройства, а выход элемента И-НЕ является впгорым выходом устройства, отличающееся тем, что, с целью упрошевия устройства, в него введены элемент ИЛИ элемент , триггер и третий регистр, D -входы которого подключены к выходам первого регистра, а выходы к соответствующим D -входам второго регистра и к первым входам элементов И-НЕ группы, вторые входы элементов И-НЕ группы подключены к S -входу триггера, первому входу элемента ИЛИ-НЕ W являются вторым входом устройства, выходы элементов 9 56 И-НЕ группы подкшочены к С-вкодам соответствующих разрядов первого регистра, R -входы первого регистра соединены с Я -входом регистра, перВЕлм входом элемента ИЛИ и являются третьим входом устройства второй вход элемента ИЛИ. соединен с вторыми входами элементов И-НН группы и ИЛИ-НЕ и является четвертым входом устройства, выход элемента ИЛИ-НЕ подключен к С-входу второго jierHCTpa, вы-; ход элемента ИЛИ подключен к R триггера, выход которого соединен с О-входами третьего регистра и управляющими, входом второго регистра. Источники информации, принятые во внимание при экспертизе 1.Авт1фское свидетельство СССР № 651336, кл. Q 06 F 3/04, 1979. 2.Авторское свидетельство СССР ;№ 773613, кл. G Об F 3/О4„198О (прототип).

ia

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1981 |

|

SU1121666A1 |

| Устройство для сопряжения | 1983 |

|

SU1124276A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Передатчик последовательного кода | 1988 |

|

SU1683177A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

4

II

«J

«- ж

MV C« PC

«u P «e

e

Авторы

Даты

1983-01-23—Публикация

1981-07-07—Подача