Поставленная цель достигается тем, wo в устройство введены последовательно соединенные регулируемый делитель частоты и формирователь тактовых импульсов, управляющий вход которого соединенС дополнительным выходом блок, управления, а выход подключен к информационному входу реверсивного коммутатора вертикальных кш{алов, последовательно соединенные регулируемый умножитель частоты, формирователь импульсов начала отсчета, узел управления и преобразователь исходного сигнала, выход которого подсоединен к сигнальному входу .блока селекции, сигнальные выходы и выходы управления которого подсоединены к соответствующим входам блока распределения, управляющие входы вертикальных каналов блока селекции соединены с выходами реверсивного коммутатора вертикальных каналов и управляющие .входы горизонтальных каналов блока селекции соединены с выходами реверсивного коммутатора горизонтальных каналов, соединенного с блоком регулирования режима реверсивного коммутатора горизонтальных каналов, информационные входы блока регулирова шя режима реверсивного коммутатора вертикальных каналов соединены с первым и последним выходами реверсивного коммутатора вертикальных каналов, при этом каждый из 2п вычислительных блоков дополнительно содержит многовходовый фазоинверсный узел, входы которюго соединены с выходами взвешивающих резисторовгруппы, двухканальный коммутатор, выход которого соединен с соответствующим входом интегратора, а управляющие входы через узел регулирования режима подключены к выходам управления блока распределения, первый узел памяти, вход которого подсоединен к выходу интегратора, а управляющие входы первых узлов памяти всех вычислительных блоков соединены вместе и подключены к соответствующему выходу блока управления, и Второй узел памяти, вход которого соединен с выходом первого узла памяти, выход соединен с соответствующим входом блока злементов И, а управляющие входы вторых узлов памяти всех вычислительных блоков соединены вместе и подключены к соответствующему выходу блока упрадления, причем соответствующие выходы масщтабного блока соединены со входами регулируемого делителя частоты, регулируемого умножителя частоты и преобразователя исходного сигнала, а з равляющий вход блока управления соединен с соответствующим выходом реверсивHOixD коммутатора горизонатльных каналов.

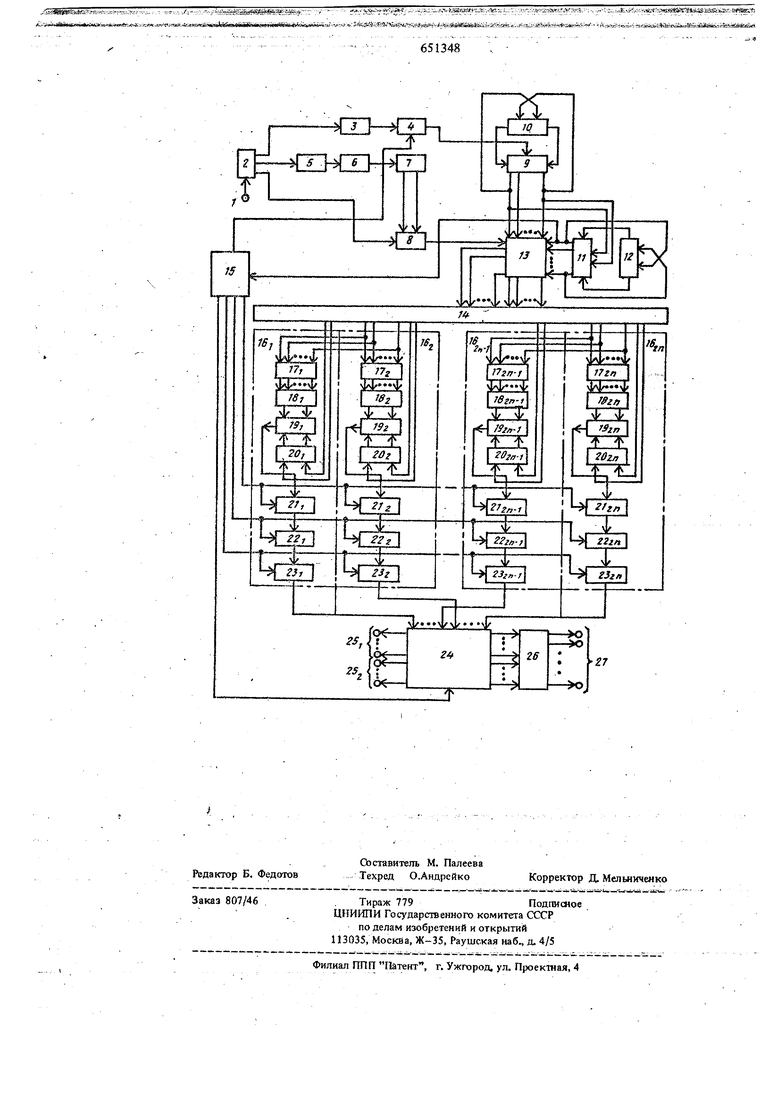

На чертеже представлена структурная схема устройства.,

Устройство для вычисления коэффициентов Фурье со входом 1 содержит масщтабньш блок 2, регулируемый делитель 3 частоты, формирова

тепь 4 тактовых импульсов, регулируемый умно житель 5 частоты, формирователь 6 импульсов начата отсчета, узел 7 управления, преобразователь 8 исходного сигнала, состоящий из связанных по своим входам и выходам двух управляемь1х запоминающих ячеек, реверсивный коммутатор 9 вертикальных каналов, блок 10 регулирования режима реверсивного коммутатора вертикальных каналов, реверсивньщ коммзтатор 11

горизонтальных каналов, блок 12 регулирования режима реверсивного коммутатора горизонтальных каналов, блок 13 селекщш, блок 14 распределения, блок 15 управления, вычислительные блоки 16i и 16j, ... 1б2п-|

группы 17i и Па, ..., взвепшнающих резисторов, многовходовых фззоинверсньк узлов 18i и 182, ... ISg. и ISjtt , двухканалькых коммутаторов 19i и 192 19гп узлов 20, и 20j, ... 20, и 20,, регулирования режима двухканальных коммутаторов по закону изменения знаков соответствующих четных и нечетных функций заданного базиса, интеграторов 21i и 21 2, ... 21„.|, и 212п , первых и вторых узлов 22, 22, ...

2п-1 гп 2. - 23.( 23g памяти соответственно, блок 24 . И, управляющие входы которых соединены вместе и подключены к управляющему входу блока, основные выходы 25, и 252 устройства, функционаггьный преобразователь 26, выполняющий oneравди

А -vB

Лп/

C« -f.2...,N), rt °п

3 в случае тригонометрического базиса, или операции

,Б, (ПИ,2,...,Ы-),

в случае любого другого базиса, дополнительные выходы 27 устройства.

Устройство работает следующим образом.

Исследуемый сигнал с интервалом повторения Т через вход I и масштабный блок 2 поступает на сигнальные входы регулируемого делителя 3 частоты, регулируемого змножителя 5 частоты и преобразователя 8 исходного сигнала.

Из колебаний, получаемых в результате делеНИИ частоты повторения исходного сигнала в заданное число раз в регулируемом делителе 3 частоты, в формирователе 4 формируются тактовые импульсы, которые поступают на информационный вход реверсивного коммзтатора 9 вертикальных каналов, а из колебаний, получаемых в результате умножения частоты повторения

исходного сетнала в заданное число раз в 1rt1регулируемомумножителе 5 частоты, в формирователе 6 импульсов начала отсчета формируются реперные импульсы, которые поступают на информационный вход узла 7 управления.

Пор,воздействием реперных импульсов узла 7 управреИия преобразователь 8 исходного, сигнала в момент начала каждого реперного импульса одновременно запоминает и считывает до начала следующего реперного импульса одно мгновенное значение исходного сигнала. В результате этого на его выходе формируется копия сигнала с интервалом повторения (nm+l)T, которая поступает на сигнальный вход.блока 13 селекции.

Под воздействием тактовых импульсов реверсивный коммутатор 9 вертикальных каналов, прямой и обратный ходы которого управляются блоком 10 регулирования режима реверсивного коммутатора вертикальных каналов, вырабатывает опросные импульсы, которые поступают на вертикальные входы блока 13 селекщш. Одновременно с этим под воздействием опрошых импульсов реверсивного комлчутатора 9 вертикалыгых каналов, снимаемых с его первого и последнего выходов, реверсивный коммутатор 11 горизонтальных каналов, прямой и обратный ходы которого управляются блоком 12 регулирования режима реверсивного коммутатора горизонтальных каналов, вырабатывает опросные импульсы, которые поступают на горизонтальные входьг блока 13 селек1иш. При этом совпаде1гае во времени на вертикальных и горизонтальных входах блока 13 селекции опросных импульсов реверсивного коммутатора 9 вертикальных каналов и реверсивного коммутатора 11 горизонтальных каналов приводит к появлению на соответствующих выходах управления и сигнальных выходах блока 13 селекции управляющих импульсов и выборок копии сигаала, которые через блок И распределения поступают на соответствующие управляющие и сигнальные входы 2п

, вычислительных блоков 16, и 162-.-, jl б результате этого выборки копии сигаала, проходя через группы 17i и 172,...172f,. и , взвешргоающих резисторов, многовходовые фазоинверсные узлы ISi и 182, ... IS и двухканальные коммутаторы 19) и 192,..., 2г реж11мы работы которых уп равляются узлами 20i и 202,.. гп регулирования режима по закону изменения знаков соответствующих четных и нечетных функций заданного базиса, интегрируются в интеграторах 21) и 212,...21

, и 212„ со

гп- сбросом.

По истече1ши интервала времени (nm+l)T опросный импульс с первого канала реверсивного коммутатора 11 горизонтальных каналов запускает блок 15 управлетшя.

Вырабатываемые в блоке 15 управления импульсы поступают на управляющие входы формирователя 4 тактовых импульсов, интеграторов 21, 212,...21 2,. ч 21211. со сбросом первых и вторых узлов 22, 222, n-i in 23|, 232 ... памяти и блока 24 злементов И. После сброса накопленных значений в интеграторах 21i, 212, sn-i 212f открывается формирователь 4 тактовых импульсов, и тактовые импульсы снова начинают поступать на информационный вход реверсивного коммутатора 9 вертикальных каналов. В результате этого, повторяется описанный цикл вьгаисления коэффициентов Фурье.

После перезаписи во вторые узлы 23t, 232 ,...23 ч 23,j , памяти зафиксированных

в первых узлах 22i, 222,... ч 22g памяти вьнисленных значений последние снова переводятся в режим слежения за накапливаемыми значениями в интеграторах 211, 212,... 2l2f)-i in Од}1овреме1шо с этим вторые узлы 23), 232,.- In-L памяти переводятся из режима записи новых значений в режим их считывания через блок 24 элементов И на основные выходы 251 и 252 устройства и через блок 26 функционального преобразования допслнительные выходы 27 устройства.

Изобретение позволяет существенно повысить точность вычисления коэффициентов Фурье повторяющихся сигаалов и сигналов с высокочастотным заполнением при отображении этих сигналов

рядами Фурье в любом заданном базисе функций вследствие преобразования частоты повторения (или несущей частоты) ситала в сторону нижних частот без использования источника опорной частоты. В результате этого «ювышается. достоверность вычисления коэффищ{ентов Фурье в заданном базисе функций и расширяется сфера применения устройства, что приводит к улучшению его технических и эксплутационных характеристик.

Формула изобретения

Устройство для вычисления коэффициентов : Фурье, содержащее масщтабньш блок, вход которого является входом устройства, блок управле, ния, блок регулирования режима реверсивного коммутатора вертикальных каналов, реверсивный коммутатор вертикальных каналов, два входа которого соединены с соответствующими выходами блока регулирования режима реверсивного коммутатора вертикальных каналов, блок распределения с подсоединенными к нему сигнальными входами 2п вычислительных блоков, каждый из которых состоит из группы взвешиваемых резисторов и интегратора, управляющие входы интеграторов всех вычислительных блоков соединены вместе и подключены к соответствующему выходу блока управления, блок элементов

И, основные выходы которого являются основными выходамн устройства, а дополнительные выходы через блок функцнонального преобразования соединены с дополнительными выходами устройства, управляющий вход блока элементов И подсоединен к соответстующему выходу блока управления, отлпчгСк Щебс т1Ш Ws, с цёдыо повышения точности вычисления коэффициентов Фурье, в него введены последовательно соединенные регулируемый делитель частоты н формнрователь тактовых импульсов, управляющий вход которого соединен с дополнтггельным выходом блока управления, а выход подаслючён к информ.адионному входу реверсивного коммутатора вертикальных каналов, последовательно соединенные регулируемый умножитель частоть, фо|рмНроваТель импульсов начала отсчета, узел управления и преобразователь исходаого сигнала, выход которого подсоединен к сигнальному входу блока селекции, сигнальные выходы и выходы управления которопэ подсоед шенЁ1 к соответствующим входам блока распределения, управляющие входы вертикальных каналов блока се 7|ШШи ШёШНёны с выходам ревёрсШюго коммутатора вертикальных каналов и управляющие входы горизонтальных каналов блока селеквди соединены с выходами реверй вного коммутатора горизонтальных каналЬв, соединенного с блоком регулировавдя режима реверсивного коммутатора горизонтальных каналов, информационные входы блока регулирования режима реверсивного коммутатора вертикальных каналов соединены с первым н последним выходами реверсивного коммутатора вертикальных каналов.

при этом каждый из 2п вьгчислительных блоков дополнительно содержит многовходовый фазоинверсный узел, входы которого соединены с выходами взвещивающих резисторов группы, двухканальнь1й коммутатор, выход которого соединен с соответствующим входом интегратора, а управляющие входь черёз узел регулирования режима подйлШены ТГ 1Шодам управления блока распределения, первый узел памяти, вход которого гюдсоединен к выходу интегратора, а управляющие входы первых узлов памяти всех вычислительных блоков соединены вместе и подключень1 к соответствующему выходу блока управления, и второй узел памяти, вход которого соединен с выходом первого узла памяти, йыход соединен с соответствующим входом блока элементов И, а управляющие входы вторых узлов памяти всех вычислительных блоков соединены вместе и подключены к соответствующему выходу блока управления, причем соответствующие выходы масштабного блока соединены со входами регулируемого делителя частоты, регулируемого умножителя частоты и 11реобразов;ателя исходного сигнала, а управляющий вход блока управления соединен с соответствующим выходом реверсивного коммутатора горизонтальных каналов.

1. . ..-,.---... .

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР N 480993, G 01 R 23/16, 1973. .

2.Авторское свидетельство СССР N 456226, G01 R 23/00, 1973.

/5

I urn

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов ряда фурье | 1976 |

|

SU646339A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВИБРАЦИИ РОТОРНЫХ МЕХАНИЗМОВ | 1992 |

|

RU2057309C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВИБРАЦИИ РОТОРНЫХ МЕХАНИЗМОВ | 1992 |

|

RU2073835C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВИБРАЦИИ РОТОРНЫХ МЕХАНИЗМОВ | 1992 |

|

RU2057310C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Функциональный генератор | 1980 |

|

SU883931A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЧАСТОТНОЙ НАСТРОЙКОЙ ПРИЕМНИКА | 1989 |

|

SU1841036A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

Авторы

Даты

1979-03-05—Публикация

1976-08-02—Подача