(54) ДИСКРЕТНЫЙ СИНХРОНИЗАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИСКРЕТНЫЙ СИНХРОНИЗАТОР | 1972 |

|

SU332558A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Цифровая система фазовой автоподстройки частоты | 1983 |

|

SU1149405A1 |

| Устройство выделения опорного сигнала | 1977 |

|

SU653758A1 |

| Устройство фазирования | 1977 |

|

SU734889A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство фазирования | 1979 |

|

SU788410A1 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU873444A1 |

1

Изобретение относится к радиотехнике, а именно к радионавигации, и может быть использовано в приемоиндикаторах фазовых радионавигационных систем-.

По основному авт.св. № 332558 известен дискретный синхронизатор, содержащий последовательно соединенные задающий генератор, схему добавлениявычитания, управляемый делитель, схему выделения, фазовых искажений и входное устройство, реверсивный счетчик, схему записи единиц с двумя выходами, схему автосброса единиц, выходы которой соединены через сумматоры с входами схемы добавлениявычитания, вногоды схемы записи единиц соединены соответственно через кольцевой регистр добавления и кольцевой регистр вычитания с входами схемы автосброса единиц 1.

Однако известный дискретный синхронизатор медленно входит в синхро низм.

Целью изобретения является уменьшение времени вхождения в синхронизм

Для этого в дискретный синхронизатор, содержащий последовательно соединенные задающий генератор, схему Добавления-вычитания, управляемый

делитель, схему выделения фазовых искажений и входное устройство, реверсивный счетчик, схему записи единиц с двумя выходами, схему автосброса единиц, выходы которой соединены через сумматоры с входами схемы добавления-вычитания, выходы схемы записи единиц соединены соответственно через кольцевой регистр добавления и кольцевой регистр вычитания с входами схемы автосброса единиц, введен анализатор, входы которого соединены соответственно с выходами задающего генератора и входного устройства, а выходы подключены к дополнительным входам управляемого делителя.

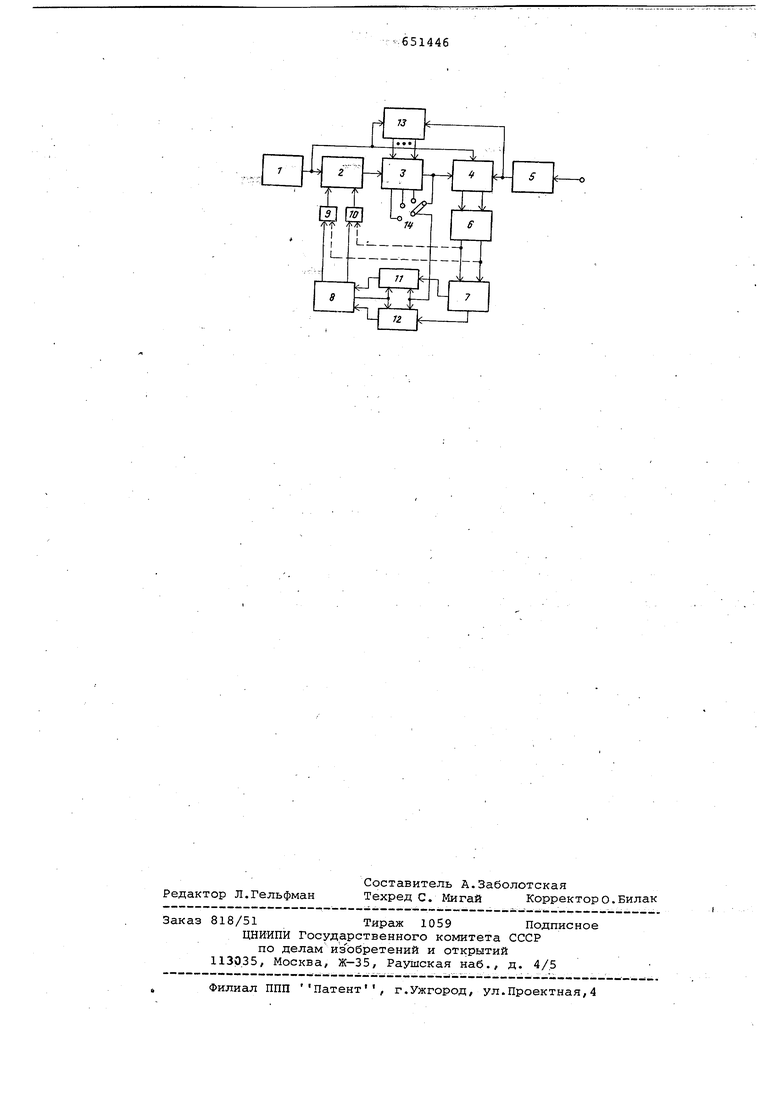

На чертеже изображена функциональная электрическая схема устройства.

Дискретный синхронизатор содержит последовательно соединенные задающий генератор 1, схему добавления-вычитания 2, управляемый делитель 3, схему выделения фазовых искажений 4 и входное устройство 5, реверсивный счетчик 6, схему записи единиц 7с двумя выходами, схему автосброса единиц 8, выходы которой соединены через сумматоры 9, 10 с входами схемы добавления-вычитания 2, выходы схемы записи единиц 7 соединены соответст effHQ через кольцевой регистр добавения 11 и кольцевой регистр вычитаия 12 с входами схемы автосбррса диниц 87 аналйзатор 13-, в;Шйй К оого сЬединены соответственно с выодами задающего генератора 1 и входого устройства 5, а выходы подклюены к дополнительным входам управяемого делителя 3, переключатель 14.

Устройство работает следующим образом. На входы анализатора 13 постуттают соответственно импульсы с выхода задающего генератора 1 и импульсы фронтов принимаемого сигнала. ПРОИСХОДИТизмерение отношения частот этих двух последовательностей иНпулесоВ, например, подсчет числа импульсов с выхода задающего генератора 1 за период частоты входного сигнала. Число, полученное в результате измерения, представляет собой коэ1} фициент деления, который должен обеспечиваться управляемым делителем 3 для того, чтобы частота опорного на его совпадала: с значениемчастоты принимаемого сигнала. Для уменьшения воздействия шумов измерение отношения частот пов-торяется определенное,число раз, а затем результаты измерений усредняются. При первоначальном вводе устройства в синхронизм с сигналом, частота которого имеет растройку относительйо опорной частоты, или в случае нарушения в процессе работы фаз6:в6й сйнхрОнизации вследствие ухода чгастоты принимаемого сигнала от ее номинального значения, усредненное значение результатов измерения отношения частот, представлющее собой требуемый коэффициент деления, поступает ввиде кода с вь1хода анализатора 13 на дополнительные входы управляемого делителя 3, задавая коэффициент деления последнего. Час fOTci опорного сигнала на входе управ ляемого делителя 3 будет равна с точностью, определяемой инструментальной ошибкой измерения отношения частот, частоте принимаемого сигнала. Инструментальная ошибка зависит от Соотношения частот принимаемого сигнала и задающего генератора и может быть сделана достаточно малой. Расс6гл ас6в анйе частот опорнЬгои п рй ййкгаемогЬ №гнала полностью определяется этой ошибкой. Поэтому вне за ййсимбстй 6т pkcCof ла сованйя опорной и принимаемой частот синхронизация будетг осуществляться только в рёжиW-зДх;., и, следова:тёльмо7 в ремя синхронизации будет невелико. Точный ввод устройства в синхронизм осуществляется следующим образом. Прннима, сигнал поступает на, входное устройство 5, формирующее ймпульсы фр нгсЯ Принимаемого сигнала, коТОрйе поступают на схему выделения фазовых искажений 4.Сюда же поступают импульсы с выхода управляемого делителя 3 и импульсы от задающегогенератора 1. Схема вьщеления фазоBbJx искажений формирует импульсы, ширйНа которых соответствует величине фа;зового рассогласования, заполняеisteie импульсами задающего генератора

частота задающего генератора 1, что достигается путем вычитания (добавления) импульсов, поступающих на управляемый делитель 3. При заполнении реверсивного счетчика 6 через

схему записи единиц 7 в кольцевой регистр вычитания 12 (добавления 11) записывается единица. Эта единица будет передвигаться тактовыми импульсами определённой частоты. Частота тактовых импульсов может изменяться с помощью переключателя 14. С кольцевого регистра вычитания 12 (добавления 11) через схему автосброса единиц ё и соответствующий сумматор подаются команды на вычитание (добавление) в схему дббавления-вычитания

При устранении рассогласования в кольцевой регистр вычитания 12 (добавления 11) не будут записываться единицы, но уже записанное количество единиц будет выдавать команды на подстройку фазы.

Введение анализатора обеспечивает работу устройства в режиме захвата и, следовательно, существенно сокращает время синхронизации. Например/ если частота принимаемого сигнала имеет первоначальную расстройку относительно частоты опорного напряжения, в десять.раз превышающую полосу захвата устройства-прототипа, то время втягивания устройства-прототипа в синхронизм достигает нескольких минут, а время синхронизации данного устройства не превышает нескольких секунд при равенстве остальных характеристик.

Формула изобретения

Дискретный синхронизатор по ЕШТ. св. № 332558, отличающийс я тем, что, с целью уменьшения времени вхождения в синхронизм, введен анализатор; входы которого соединены соответственно с выходами задающего генератора и входного устройства, а вБКбда подключены к дополнительным входам управляемого делителя. Источники информации, принятые во

внимание при экспертизе

Авторы

Даты

1979-03-05—Публикация

1977-04-18—Подача