(54) УСТРОЙСТВО ВЫДЕЛЕНИЯ ОПОРНОГО СИГНАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазирования | 1977 |

|

SU734889A1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| Устройство фазирования | 1979 |

|

SU788410A1 |

| Устройство для автоматического измерения амплитуды переменного сигнала | 1987 |

|

SU1513406A2 |

| Устройство для радиоприема | 1989 |

|

SU1699006A1 |

| Устройство для автоматического измерения амплитуды переменного сигнала | 1977 |

|

SU711482A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Устройство компенсации сдвигачАСТОТ | 1979 |

|

SU843270A1 |

Изобретение относится к электросвязи и может использоваться в модемах для передачи данных, в которых применены сигналы AM, ФМ и ФАМ.

Известно устройство выделения опорного сигнала, содержащее первый блок добавления - вычитания, перемножитель, первый вход которого является входом устройства, а второй вход через последовательно соединенные первый делитель частоты и второй блок добавления - вычитания соединен с выходом задающего генератора, а выход перемножителя соединен с входом фильтра, а также последовательно соединенные ограничитель и блок формирования импульсов, другой вход которого соединен с выходом блока тактовых колебаний, а выход - с первым входом первого фазового различителя, другой вход которого соединен с выходом второго делителя частоты .

Однако в таком устройстве больщие искажения выделяемых колебаний.

Цель изобретения - уменьщение искажения выделяемых колебаний.

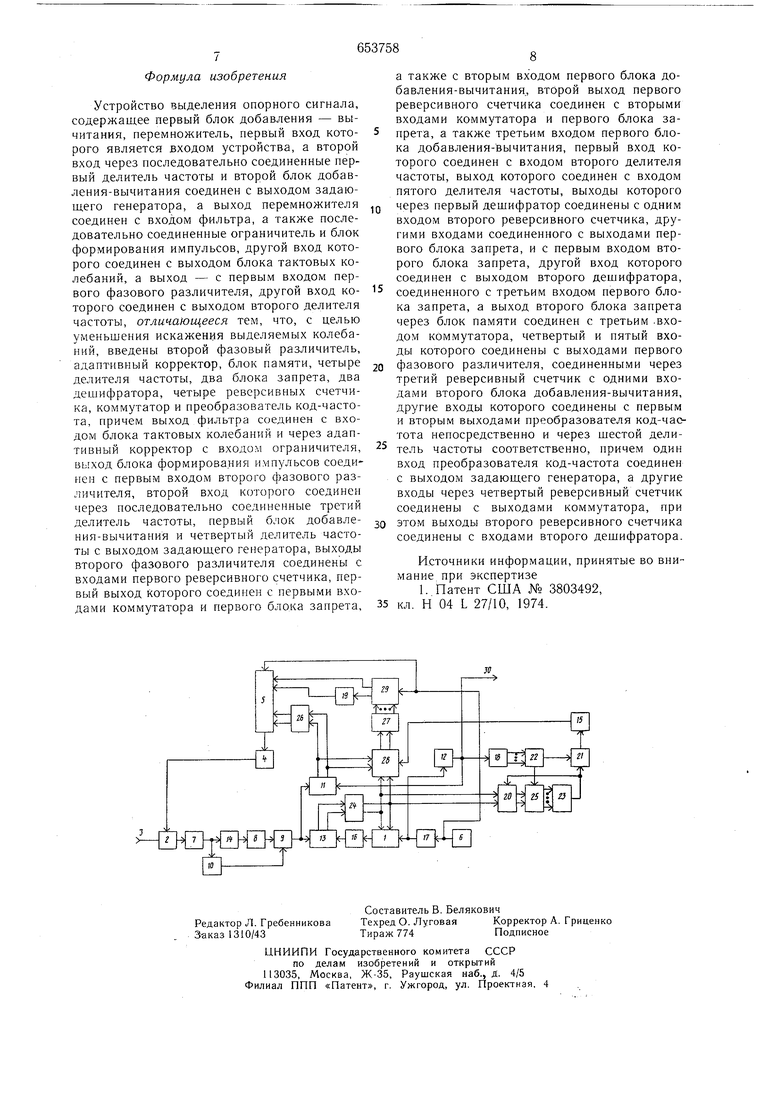

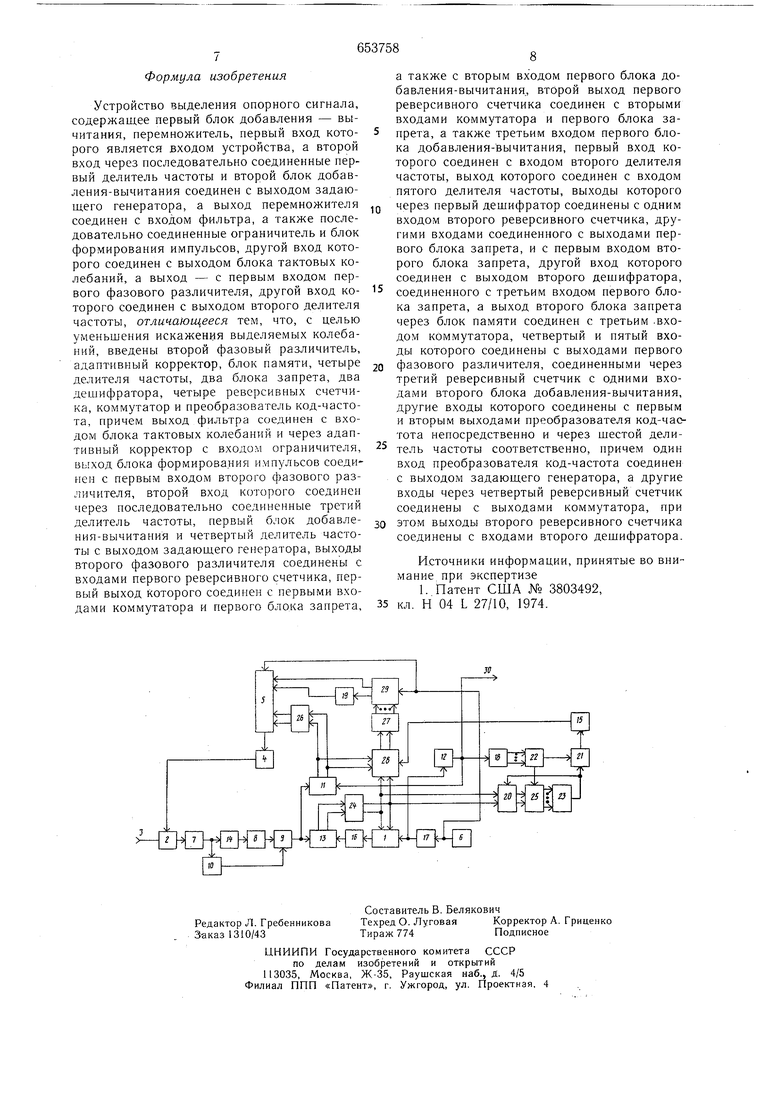

Для этого в устройство выделения опорного сигнала, содержащее первый блок добавления - вычитания, перемножитель, первый вход которого является входом устройства, а второй вход через последовательно соединенные первый делитель частоты и второй блок добавления - вычитания соединен с выходом задающего генератора, а выход перемножителя соединен с входом фильтра, а также последовательно соединенные ограничитель и блок формирования импульсов, другой вход которого соединен с выходом блока тактовых колебаний, а выход - с первым входом первого фазового различителя, другой вход которого соединен с выходом второго делителя частоты, введены второй фазовый различитель, адаптивный корректор, блок памяти, четыре делителя частоты, два блока запрета, два дещифратора, четыре реверсивных счетчика, коммутатор и преобразователь код-частота, причем выход фильтра соединен с входом блока тактовых колебаний и через адаптивный корректор с .входом ограничителя, выход блока формирования импульсов соединен с первым входом второго фазового различителя, второй вход которого соединен через последовательно соединенные третий делитель частоты. первый блок добавления - вычитания и четвертый делитель частоты с выходом задающего генератора, выходы второго фазового различителя соединены с входами первого реверсивного счетчика, первый выход которого соединен с первыми входами коммутатора и первого блока запрета а также с вторым входом первого блока добавлениявычитания, второй выход первого реверсивного счетчика соединен с вторыми входами коммутатора и первого блока запрета, а также третьим входом первого блока добавления-вычитания, первый вход которого соединен с входом второго делителя частоты, выход которого соединен с входом пятого делителя частоты, выходы которого через первый дешифратор соединены с одним входом второго реверсивного счетчика, другими входами соединенного с выходами первого блока запрета, и с первым входом второго блока запрета, другой вход которого соединен с выходом второго дешифратора, соединенного с третьим входом первого блока запрета, а выход второго блока запрета через блок памяти соединен с третьим входом коммутатора, четвертый и пятый входы которого соединены с выходами первого фазового различителя, соединенными через третий реверсивный счетчик с одними входами второго блока добавления-вычитания, другие входы которого соединены с первым и вторым выходами преобразователя кодчастота непосредственно и через шестой делитель частоты соответственно, причем один вход преобразователя код-частота соединен с выходом задающего генератора, а другие входы через четвертый реверсивный .счетчик соединены с выходами коммутатора, при этом выходы второго реверсивного счетчика соединены с входами второго дешифратора. На чертеже дана структурная электрическая схема предлагаемого устройства выделения опорного сигнала. Устройство содержит первый блок 1 добавления-вычитания, перемножитель 2, первый вход которого является входом 3 устройства, а второй вход через последовательно соединенные первый делитель 4 частоты и второй блок 5 добавления-вычитания соеди-. нен с выходом задающего генератора 6, а выход перемножителя 2 соединен с входом фильтра 7, а также последовательно соединенные ограничитель 8 и блок 9 формирования импульсов, другой вход которого соединен с выходом блока 10 тактовых колебаний, а выход - с первым входом первого фазового различителя 11, другой вход которого соединен с выходом второго делителя 12 частоты, второй фазовый различитель 13, адаптибный корректор 14, блок 15 памяти, четыре делителя 16-19 частоты, два блока 20 и 21 запрета, два дешифратора 22 и 23, четыре реверсивных счетчика 24-27, коммутатор 28 и преобразователь 29 код-частота, причем выход фильтра 7 соединен с входом блока 10 тактовых колебаний и через адаптивный корректор 14 с входом ограничителя 8, выход блока 9 формирования импульсов соединен с первым входом второго фазового различителя 13, второй вход которого соединен через последовательно соединенные третий делитель 16 частоты, первый блок 1 добавления вычитания и четвертый делитель 17 частоты с выходом задающего генератора 6, выходы второго фазового различителя 13 соединены с входами первого реверсивного счетчика 24, первый выход которого соединен с первыми входами коммутатора 28 и первого блока 20 запрета, а также с вторым входом первого блока 1 добавления-вычитания, второй выход первого реверсивного счетчика 24 соединен с вторыми входами коммутатора 28 и первого блока 20 запрета, а также третьим входом первого блока 1 добавления-вычитания, первый вход которого соединен с входом второго делителя 12 частоты, выход которого соединен с входом пятого делителя 18 частоты, выходы которого через первый дешифратор 22 соединены с одним входом второго реверсивного счетчика 25, другими входами соединенного с выходами первого блока 20 запрета, и с первым входом второго блока 2 запрета, другой вход которого соединен с выходом второго дешифратора 23, соединенного с третьим входом первого блока 20 запрета, а ВЫХОД второго блока 21 запрета через блок 15 памяти соединен с третьим входом коммутатора 28, четвертый и пятый входы которого соединены с выходами первого фазового различителя 11, соединенны.ми через третий реверсивный счетчик 26 с одни.ми входами второго блока 5 добавления-вычитания, другие входы которого соединены с первым и вторым выходами преобразователя 29 код-частота непосредственно и через шестой делитель 19 частоты соответственно, причем один вход преобразователя 29 кодчастота соединен с выходом задающего генератора 6, а другие входы через четвертый реверсивный счетчик 27 соединены с выходами коммутатора 28,, при этом выходы второго реверсивного счетчика 25 соединены с входами второго дещифратора 23, кроме того выход 30 устройства. Устройство работает в режиме вхождения в синхронизм и в установившемся режиме. Режим вхождения в синхронизм можно разбить на два этапа. Первый - устранение влияния расхождения частот и второй - подгонка фазы опорного колебания. Основное влияние на работу устройства оказывает третье кольцо автоподстройки, образованное каскадным соединением перемножителя 2, фильтра 7, адаптивного корректоpa 14, ограничителя 8, блока 9 формирования, второго фазового различителя 13, третьего делителя 16, первого блока добавления-вычитания, коммутатора 28, четвертого реверсивного счетчика 27, преобразователя 29, второго блока 5 добавления-вычитания и первого делителя 4. Входной сигнал попадает на вход перемножителя 2. Фильтром 7 выделяется требуемая боковая полоса, и сигнал проходит через адаптивный корректор 14, после чего ограничивается по амплитуде ограничителе 8. В блоке 9 формирования, в каждом единичном интервале формируется короткий импульс, положение которого определяется положением первого фронта или нулевого пересечения наполняющего колебания следующего после тактового импульса, поступающего от блока 10 тактовых колебаний. Положение и.мпульса сравнивается во второл фазовом различителе 3 с фазой колебания, поступающего от третьего делителя 6 частоты. Результат сравнения используется для устранения различия по фазе, для чего подается через первый реверсивный счетчик 24 на первый блок 1 добавлениявычитания. Возможность подгонки по фазе выбирается так, чтобы можно было отслеживать различие по фазе, возникающее при любых возмол ных расхождениях частот в канале. При наличии расхождения частот на знаковом выходе первого реверсивного счетчика 24 будут преобладать сигналы какой-либо одной полярности. Эти сигналы через коммутатор 28 и четвертый реверсивный счетчик 27 юпадают на преобразователь 29, который обеспечивает совместно с ujecTbiM делителем 19 частоты подачу на второй блок 5 добавления-вычитания последовательности импульсов с частотой, равной (с точностью до половины величины щага по частоте) величине расхождения частот несущего колебания и выделяемого опорного колебания, снимаемого с выхода второго делителя 12 частоты, управление коммутатором 28 осуществляется с выхода блока 15 памяти, сигнал на выходе которого свидетельствует о наличии расхождения час: тот, превыщающем полосу захвата первого фазового кольца. Первое фазовое кольцо состоит из перемножителя 2, фильтра 7, адаптивного корректора 14, ограничителя 8, блока 9 формирования, первого фазового различителя 11, третьего реверсивного счетчика 26, второго блока 5 добавления-вычитания и первого делителя 4. Сигнал о. наличии расхождения форми.руется на выходе второго дешифратора 23, в зависимости от состояния второго реверсивного счетчика 25 в конце интервала времени, определяемого сигналом от первого дещифратора 22, подключенного к пятому делителю 18 частоты. Работа этой части схемы начинается по поступлению импульса установки на второй реверсивный счетчик 25 от первого дещифратора 22. На входы второго реверсивного счетчика 25 подаются сигналы о фазовом различии с выхода первого реверсивного счетчика 24 через первый блок 20 запрета. При наличии преобладания, в подаваемых сигналах, что свидетельствует о расхождении частот, превышающем возможности захвата первого фазового кольца, второй реверсивный счетчик 25 до конца заданного интервала наполняется, в результате чего на выходе второго дещифратора 23 возникает сигнал запрета постугмения да.тьиейших сигналов на второй реверсивный счетчик 25. В конце заданного интервала этот сигнал считывается в блок 15 памяти через второй блок 21 запрета по импульсу, поступающему от первого дешифратора 22. После записи результата сравнения в блок 15 памяти сразу же происходит установка второго реверсивного счетчика 25 в исходное состояние, в результате чего сигнал запрета снимается с первого блока 20 запрета и начинается новая проба наличия расхождения частот. После устранения расхождения частот до величины меньщеи полосы захвата первого фазового кольца, первое фазовое кольцо производит подгонку фазы принимаемого сигнала к фазе выделяемого опорного колебания. Фаза принимаемого сигнала сравнивается с фазой колебания от второго делителя 12 в первом фазовом различителе И. Результат сравнения через третий реверсивный счетчик 26 подается на второй блок 5 добав.1ения-вычитг.ния, что обеспечивает вхождение устройства в синхроПосле вхождеяия в син.хроннзм происходит изменение сигнала на выходе блока 15 памяти. На преобразователь 29 будут подаваться сигналы управления от первого фазового различителя 11. Это обеспечивает установку значения частоты сигнала подстройки, поступающего от преобразователя 29. обеспечивающего отсутствие преобладаний на выходе первого фазового различителя и, что обеспечивает первым фазовым кольцом только фазовых, а не частотных Отклонений несущего колебания сигнала от опорного колебания (в пределах половины щага по частоте преобразователя 29). Уменьшение фазовых качаний выделенного опорного колебания по отношению к сигналу позволяет увеличить помехоустойчивость модема передачи данных, величина выигрыша составляет 1,5-2 дБ. Устройство с адаптивным корректором 14 позволяет увеличить помехозащищенность до 5-6 дБ.

Авторы

Даты

1979-03-25—Публикация

1977-03-16—Подача