Изобретение может быть использовано в радиотехнических импульсных системах и регенераторах.

Известные дискретные синхронизаторы, содержащие последовательно соединенные задающий генератор, схему добавления - вычитания, упра вляемый делитель, схему выделения фазо.вых искажений, реверсивный счетчик, схему записи единиц с двумя входами, схему автосброса единиц, выходы которой соединены через сумматоры со входами схемы добавления-вычитания, имеют малую полосу схватывания и удержания.

Для увеличения полосы схватывания и удержания в предлагаемом дискретном синхронизаторе выходы схемы записи соединены соответственно через кольцевой регистр добавления и кольцевой регистр вычитания со входами схемы автосброса.

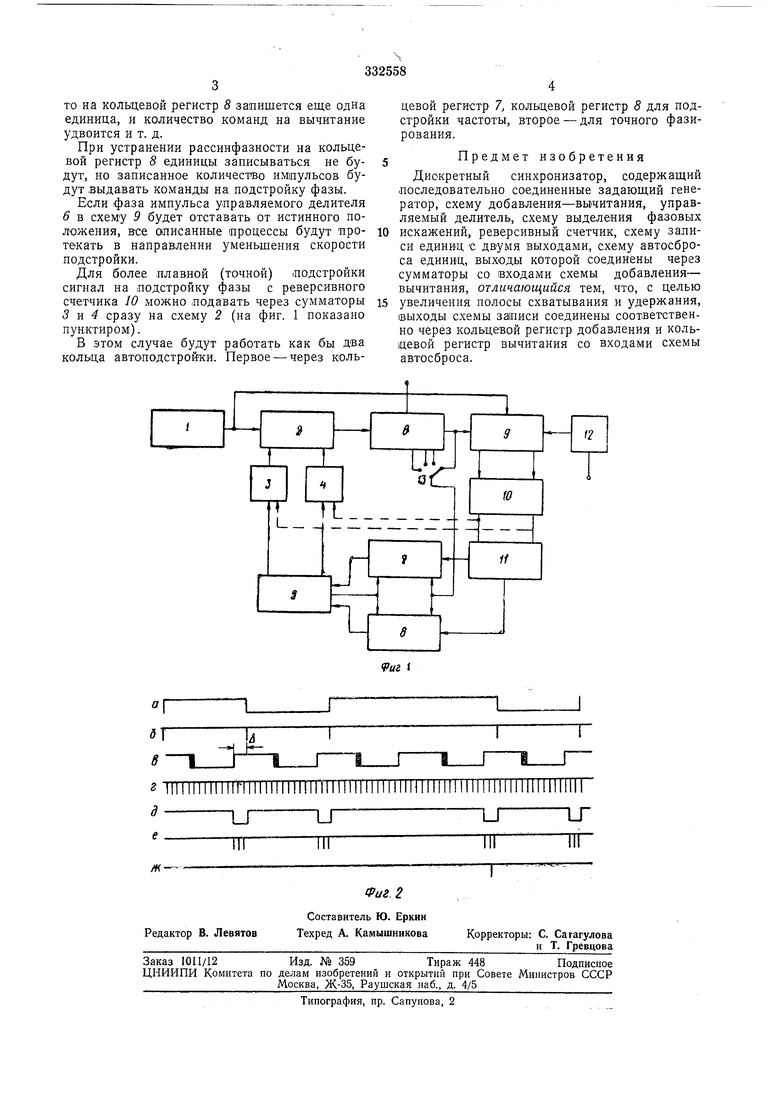

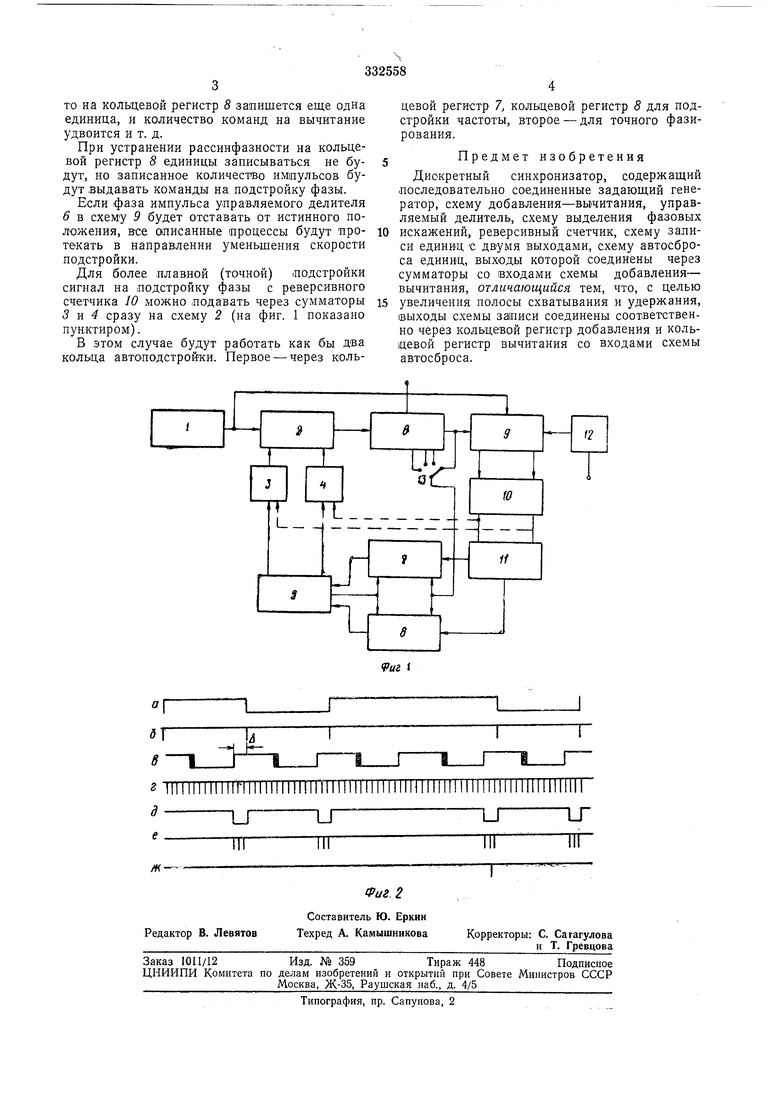

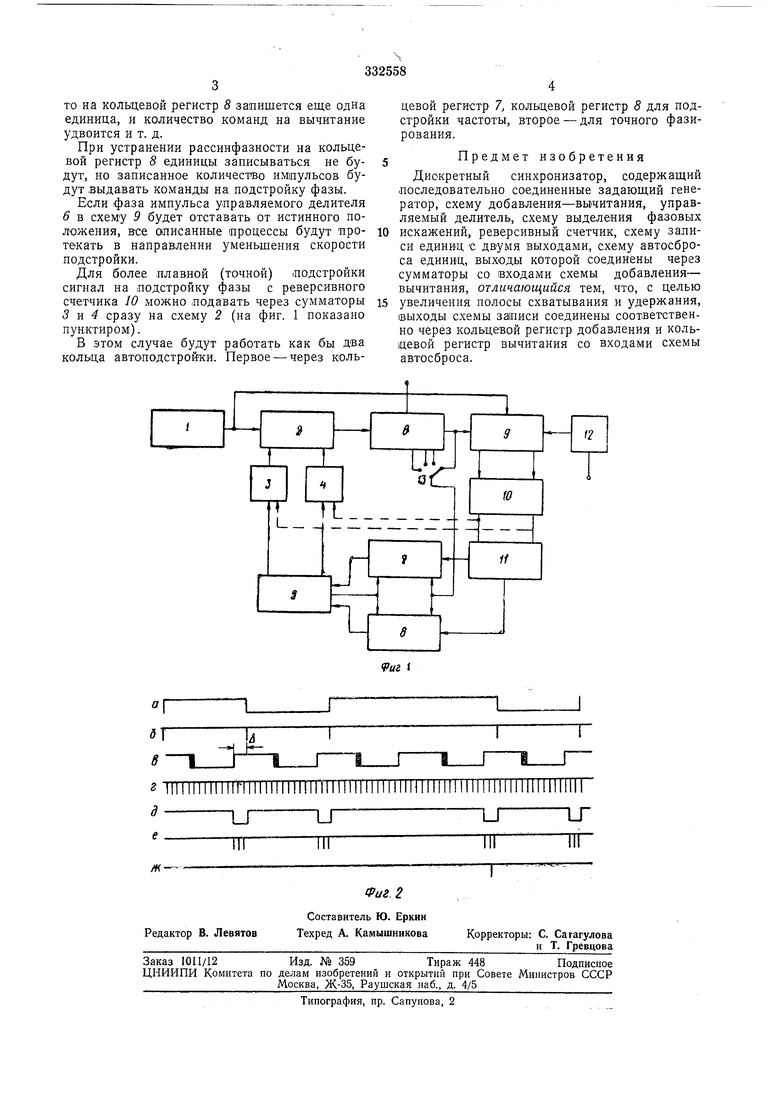

На фиг. 1 приведена блок-схема синхронизатора; на фиг. 2 - диаграмма напрял епий в различных точках схемы.

Дискретный синхронизатор состоит из задающего генератора 1, схемы добавления - вычитания 2, сумматоров 3, 4, схемы автосброса единиц 5, управляемого делителя 6, кольцевого регистра добавления 7, кольцевого регистра вычитания 8, схемы выделения фазовых иска/кепий 9, реверсивного счетчика 10, схемы записи единиц 11, выходного устройства 12, переключателя 13.

Дискретная система синхронизации работает следующим образом.

Входной сигнал (фиг. 2,а) поступает на входное устройство 12, формирующее импульсы фронтов входного сигнала (фиг. 2,6), которые поступают на схему выделения фазовых искажений 9. Сюда же поступают импульсы с

управляемого делителя 6 (фиг. 2,в) и импульсы (фиг. 2,г) с задающего генератора 1.

Схема выделения фазовых искажений формирует импульсы величины рассогласования (фиг. 2,д), которые заполняются импульсами

задающего генератора / (фиг. 2,е). Эти импульсы поступают на реверсивный счетчик.

Как видно из фиг. 2, импульс управляемого делителя 6 опережает свое истинное положение на величину Д. Для устранения этого необходимо уменьшить частоту задающего генератора 1, что достигается путем вычитания импульсов, поступающих на управляемый делитель 6. Поэтому при заполнении реверсивного счетчи-ка 10 (фиг. 2,ж) через схему 11 на

кольцевой регистр 5 запишется единица. Эта единица будет передвигаться тактовыми импульсами, идущими через переключатель 13.

то на кольцевой регистр 5 запишется еще одна единица, и количество команд на вычитание удвоится и т. д.

При устранении рассинфазности на кольцевой регистр 8 единицы записываться не будут, но записанное количество имиульсов будут .выдавать команды на подстройку фазы.

Если фаза импульса управляемого делителя 6 в схему 9 будет отставать от истинного положения, Все описанные процессы будут протекать в направлении уменьшения скорости подстройки.

Для более плавной (точной) .подстройки сигнал на подстройку фазы с реверсивного счетчика 10 можно подавать через сумматоры 3 и 4 сразу на схему 2 (на фиг. 1 показано пуЕктиром).

В этом случае будут работать как бы Два кольца автоподстройки. Первое - через кольцевой регистр 7, кольцевой регистр 5 для подстройки частоты, второе - для точного фазирования.

Предмет изобретения

Дискретный синхронизатор, содержащий последовательно соединенные задающий генератор, схему добавления-вычитания, управляемый делитель, схему выделения фазовых

искажений, реверсивный счетчик, схему записи единиц С двумя выходами, схему автосброса единиц, выходы которой соединены через сумматоры со входами схемы добавления- вычитания, отличающийся тем, что, с целью

увеличения полосы схватывания и удержания, выходы схемы записи соединены соответственно через кольцевой регистр добавления и кольцевой регистр вычитания со входами схемы автосброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дисретный синхронизатор | 1977 |

|

SU651446A2 |

| Цифровая система фазовой автоподстройки частоты | 1983 |

|

SU1149405A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Дискретный синхронизатор | 1973 |

|

SU516172A1 |

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| Двухступенчатый параллельно-последовательный регенератор | 1985 |

|

SU1246394A1 |

| Цифровое устройство фазовой синхронизации | 1985 |

|

SU1358103A1 |

| Устройство выбора каналов для разнесенного приема | 1988 |

|

SU1525925A1 |

Даты

1972-01-01—Публикация