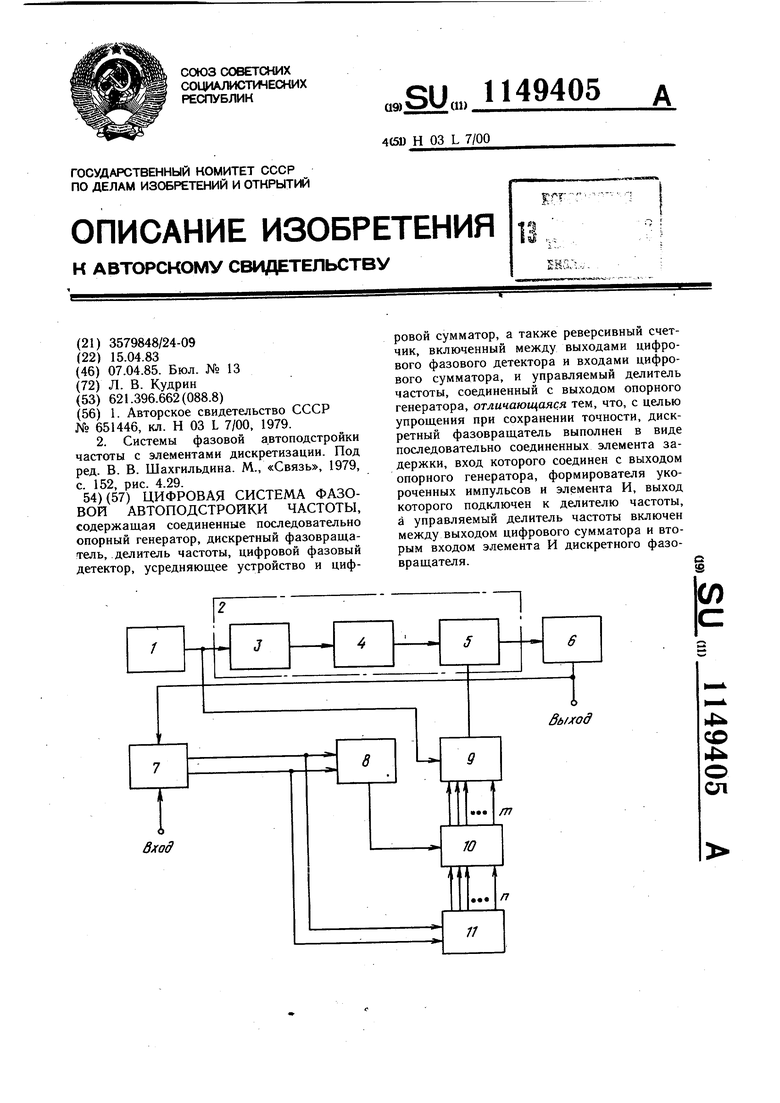

Изобретение относится к радиотехнике и может быть использовано в радиоизмерительной технике. Известная цифровая система фазовой синхронизации содержит соединенные последовательно задающий генератор, схему добавления - вычитания, управляемый делитель, схему выделения фазовых искажений, кроме того имеется входное устройство, реверсивНый счетчик,, схема записи единиц с двумя выходами, схема автосброса единиц. Выходы схемы автосброса единиц соединены через сумматоры с входами схемы добавления - вычитания. Выходы схемы записи единиц соединены соответственно через кольцевой регистр добавления и кольцевой регистр вычитания с входами схемы автосброса единиц. Устройство содержит также анализатор, входы которого соединены с выходами задающего.генератора и входного устройства. Выходы анализатора подключены к дополнительным входам управляемого делителя 1. Недостаток системы - высокие требования к быстродействию элемед1тов. Наиболее близкой к изобретению по технической сущности является цифровая система фазовой автоподстройки частоты, содержащая последовательно соединенные опорный генератор, дискретный фазовращатель (выполненный в виде узла добавления - вычитания), делитель частоты, цифровой фазовый детектор, усредняющее устройство и цифровой сумматор, а также реёерсивйый счетчик, включенный между выходами цифрового фазового детектора и входами цифрового сумматора, и управляемый делитель частоты, соединенный с выходом опорного генератора. В известном устройстве управляемый делитель частоты выполнен в виде последовательно соединеннь;х блока частот, подключенного к опорному генератору, и дещифратора, управляемого цифровым кодом 2. Однако известное устройство является сложным в реализации в том случае, когда требуемся высокая точность синхронизации, так как при высоких требованиях к точности синхронизации растут требования к быстродействию элементов устройства. Цель изобретения - упрощение при сохранении точности. Цель достигается тем, что в цифровой системе фазовой автоподстройки частоты, содержащей соединенные последовательно опорный генератор, дискретный фазовращатель, делитель частоты, цифровой фазовый детектор, усредняющее устройство и цифровой сумматор, а также реверсивный счетчик, включенный между выходами цифрового фазового детектора и входами цифрового сумматора, и управляемый делитель частоты, соединенный с выходом опорного генератора, дискретный фазовращатель выполнен в виде последовательно соединенных элемента задержки, вход которого соединен с выходом опорного генератора, формирователя укороченных импульсов и элемента И, выход которого подключен к делителю частоты, а управляемый делитель частоты включен между выходом цифрового сумматора и вторым входом элемента И дискретного фазовращателя. На чертеже представлена структурная электрическая схема цифровой системы фазовой автоподстройки частоты. Устройство из опорного генератора 1, дискретного фазовращателя 2, в состав которого входят элемент 3 задержки, формирователь 4 укороченных импульсов и элемент И 5, делителя 6 частоты, цифрового фазового детектора 7, усредняющего устройства 8, управляемого делителя 9 частоты, цифрового сумматора 10 и реверсивного счетчика 11. Предлагаемое устройство работает следующим образом. Опорный генератор 1 обеспечивает прямоугольное импульсное напряжение с частотой, больщей частоты выходного сигнала. Элемент 3 задержки задерживает импульсы опорного генератора 1 на время, больщее времени задержки сигнала в управляемом делителе 9. Формирователь 4 укороченных импульсов укорачивает импульсы так, чтобы их задний фронт проходил раньще, чем задний фронт соответствующих импульсов, прошедщих через управляемый делитель 9. Элемент И 5 обеспечивает бланкирование части импульсов опорного генератора 1, определяемой коэффициентом деления управляемого делителя 9. Цифровой фазовый детектор 7 определяет, опережает либо отстает определенный фронт входного сигнала от опорного импульса и выдает сигналы опережения либо отставания. Усредняющее устройство 8 обеспечивает работу пропорциональной ветви коррекции. Для этого оно подсчитывает на заданном интервале число опережений и отставаний и в зависимости от результата сравнения чисел опережений и отставаний выдает сигнал для соответствующей коррекции фазы выходного сигнала. Управляемый делитель 9 обеспечивает элемент И 5 бланкирующими импульсами, используя сигнал опорного генератора 1 и управляющий т- разрядный код цифрового сумматора 10. Цифровой сумматор 10 суммирует п-разрядный код управления, формируемый в реверсивном счетчике 11, с сигналом управления ot усредняющего устройства 8. Реверсивный счетчик 1 выполняет функции интегратора, интегрируя отсчеты цифрового фазового детектора 7. Если в один из периодов усреднения сигналов опережение фазой выходного сигнала

фазы входного сигнала будет больше, то, проинтегрировав эти данные за время усреднения, реверсивный счетчик 11 увеличит код управления управляемым делителем 9. Кроме того, усредняющее устройство 8 формирует на следующий период усреднения управляющий сигнал пропорциональной части, цифровой сумматор 10 суммирует сигнал управления от усредняющего устройства 8 с кодом от реверсивного счетчика 11 и увеличивает результирующий код для управляемого делителя 9. При этом частота импульсов на выходе управляемого делителя 9 увеличивается и больщее, чем ранее число импульсов опорного генератора 1 бланкируется, что приводит к увеличению периода выходного сигнала и задержке его фазы. Процесс повторяется до тех пор, пока от цифрового фазового детектора 7 не,, приходит сигналов запаздывания больше, чем сигналов опережения. При этом уменьщается код реверсивного счетчика 11, а усредняющее устройство 8 на следующий период усреднения отключает сигнал управления пропорциональной части, что приводит к уменьшению частоты следования импульсов

на выходе управляемого делителя 9 и к увеличению частоты выходного сигнала, к опережению его фазой фазы входного сигнала. Таким образом, коррекция фазы выходного сигнала системы зависит от суммы воздействия, определяемого интегралом функции оценок разности фаз входного и выходного сигналов, и воздействи я, имеющего квантование по двум уровням и определяемого средним значением этой функции на предыдущем интервале усреднения. Это обеспечивает условия работы цифровой системы фазовой синхронизации с астатизмом второго порядка. Система имеет параметры, соответствующие параметрам известного устройства, если сумма добавляемых и вычитаемых импульсов за период усреднения в известном устройстве равна числу вычитаемых импульсов в предлагаемом устройстве за аналогичный интервал времени.

Отсутствие необходимости вписывать добавочные импульсы для уменьшения периода выходного сигнала позволяет упростить аппаратуру при сохранении точности, определяемой быстродействием примененных углов и частотой опорного генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Дисретный синхронизатор | 1977 |

|

SU651446A2 |

| Устройство автоподстройки несущей частоты | 1984 |

|

SU1298946A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

| Генератор-калибратор временных интервалов | 1985 |

|

SU1367138A1 |

| Устройство фазовой автоподстройки частоты | 1979 |

|

SU930695A1 |

| Формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией | 1982 |

|

SU1136323A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| СПОСОБ ФОРМИРОВАНИЯ КОГЕРЕНТНОГО ОПТИЧЕСКОГО СИГНАЛА СУММИРОВАНИЕМ ПУЧКОВ ИЗЛУЧЕНИЯ N ЛАЗЕРОВ В ВЕРШИНЕ КОНИЧЕСКОЙ ПОВЕРХНОСТИ И ПЕРЕДАТЧИК КОГЕРЕНТНОГО ОПТИЧЕСКОГО ИЗЛУЧЕНИЯ, РЕАЛИЗУЮЩИЙ ЭТОТ СПОСОБ | 1992 |

|

RU2109384C1 |

ЦИФРОВАЯ СИСТЕМА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ, содержащая соединенные последовательно опорный генератор, дискретный фазовращатель, делитель частоты, цифровой фазовый детектор, усредняющее устройство и цифровой сумматор, а также реверсивный счетчик, включенный между выходами цифрового фазового детектора и входами цифрового сумматора, и управляемый делитель частоты, соединенный с выходом опорного генератора, отличающаяся тем, что, с целью упрощения при сохранении точности, дискретный фазовращатель выполнен в виде последовательно соединенных элемента задержки, вход которого соединен с выходом опорного генератора, формирователя укороченных импульсов и элемента И, выход которого подключен к делителю частоты, а управляемый делитель частоты включен между выходом цифрового сумматора и вторым входом элемента И дискретного фазовращателя. С S (Л 4 СО 4; о сд

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дисретный синхронизатор | 1977 |

|

SU651446A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Системы фазовой а.втоподстройки частоты с элементами дискретизации | |||

| Под ред | |||

| В | |||

| В | |||

| Шахгильдина | |||

| М., «Связь, 1979, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1985-04-07—Публикация

1983-04-15—Подача