(54) АНАЛОГОиЦИФРОВОЙ ПРЕ(ЖРАЭОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU782153A1 |

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

| Параллельно-последовательный аналого- цифровой преобразователь | 1977 |

|

SU758512A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790295A1 |

| Аналого-цифровой преобразователь | 1973 |

|

SU711676A1 |

| Устройство для измерения ошибок позиционирования шагового электродвигателя | 1990 |

|

SU1697254A1 |

| Интегрирующий аналого-цифровой преобразователь | 2023 |

|

RU2802872C1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU767965A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| ПИРОМЕТР ИЗЛУЧЕНИЯ | 1993 |

|

RU2113696C1 |

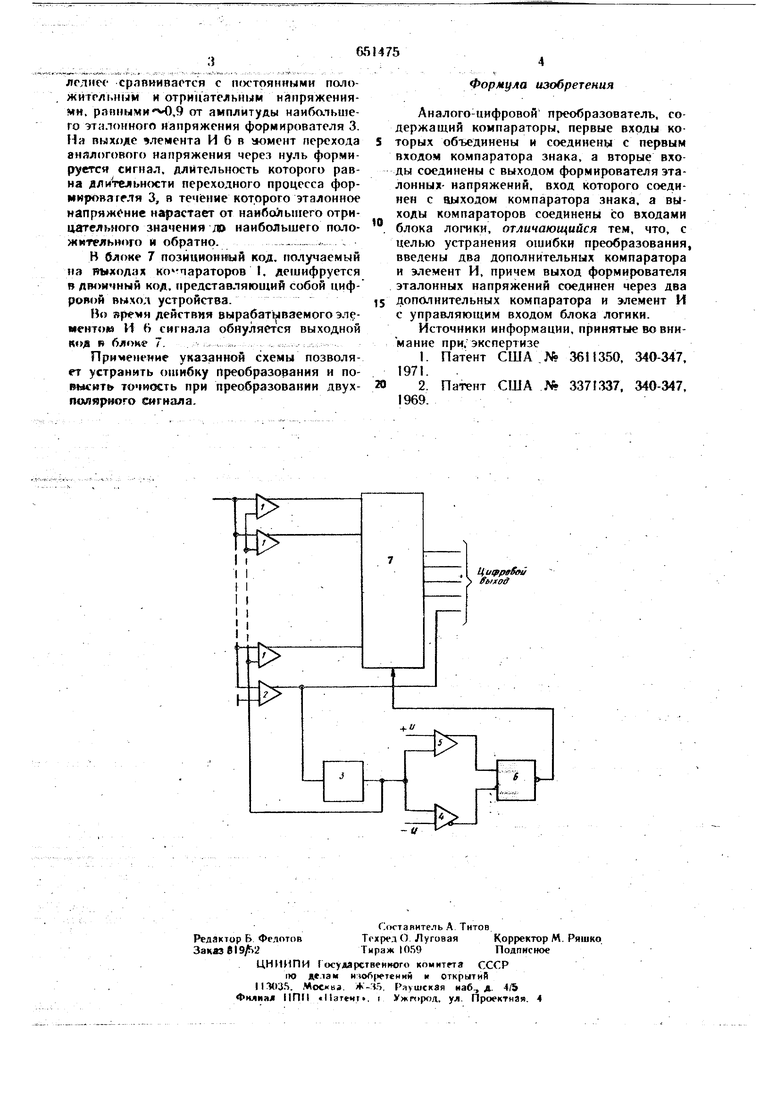

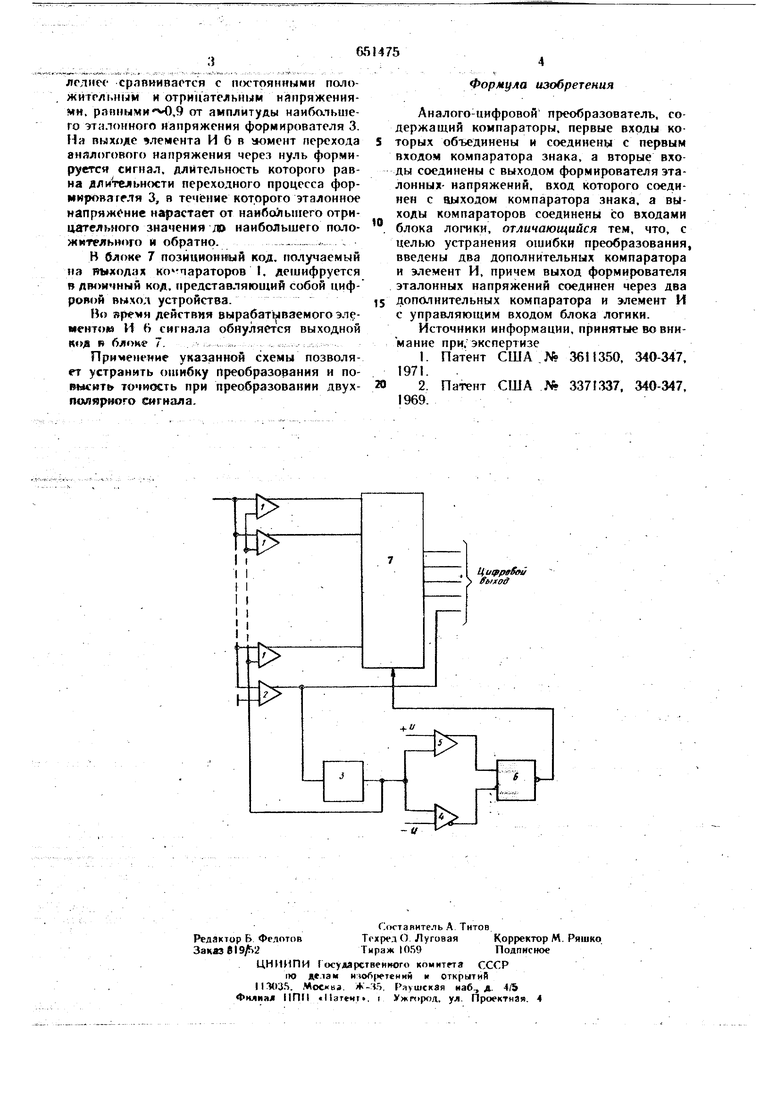

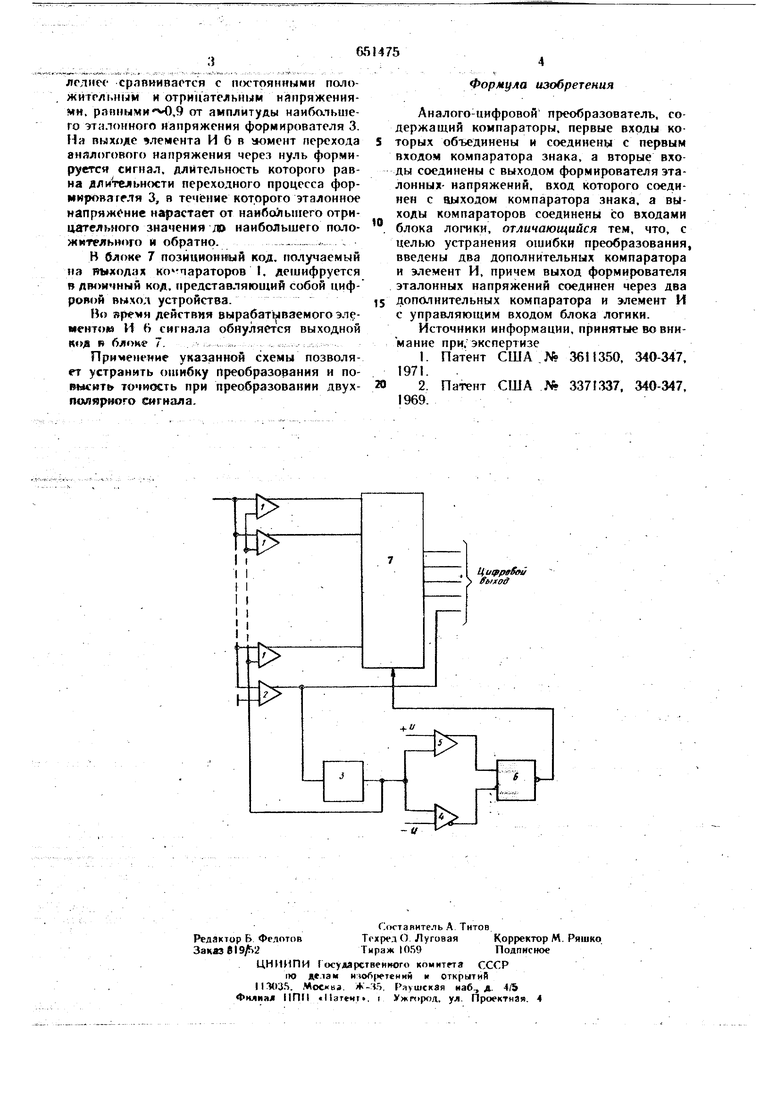

Изобретение относится к измерительной технике. Известен аналого-цифровой преобразователь, содержащий компараторы, источники эталонных напряжений, в котором двухполярный аналоговый сигнал сравнивается с постоянными эталонными напряжениями обоих знаков 1). Однако это устройство действует с недостаточной точностью. Известен аналого-цифровой преобразователь, содержащий компаратор на транзисторе, компаратор знака на транзисторе, формирователь эталонных напряжений, вхОд которого соединен с выходом компаратора знака, состоящий из транзистора и делителя на резисторах; входы компараторов соединены с шиной источника сигнала 2. В этом устройстве в момент перехода сигнала через нуль может появиться ошибка квантования. Це-ть изобретения - устранение ошибки преобразования. Достигается она тем, что в аналого-цифровой преобразователь, содержащий компараторы, компаратор знака, формирователь эталонного напряжения и блок логики, введены два допатнительных компаратора и элемент И, причем выход формирователя эталонных напряжений через два допатнительных компаратора и элемент И соединен с управляющим входом блока логики. Структурная электрическая схема устройства приведена на чертеже. Устройство содержит 2 компараторов I, компаратор знака 2, формирователь 3 эталонных напряжений, компараторы 4, 5, элемент И 6, блок 7 логики. Аналоговый сигнал поступает одновременно на компаратор знака 2 и. на все 2 компараторов I и сравнивается в последних с 2 эталонными напряжениями того или иного знака, вырабатываемыми формирователем 3 в зависимости от полярности входного сигнала по сигналу компаратора 2. Компаратор 2 определяет знак входного сигнала и меняет знак в момент перехода этого сигнала через нуль. Знак входного сигнала определяет, в каком коде использовать цифровой выход устройства (в прямом или обратном). На компараторы 4 и 5 подается наибольщее значение эталонного напряжения, вырабатываемого формирователем 3, где послглмес сравииваотся с п(х-тоянными положйггльиым и отрицательным напряжениями, рапнымиМ),) от амплитуды наибатьшего эталонного напряжения формирователя 3. На вьаходе элемента И 6 в аомент перехода аналогового напряжения через нуль формируется сигнал, длительность которого равна длительности переходного процесса формирователя 3, в течение которого эталонное напряжение нарастает от наибо)ыиего отрицательного значения да наибольшего паюжмтельного и обратно.-- ., ,

В блгже 7 ПОЗИЦИОНН1ЫЙ код, получаемый иа тшходая KovnapaTopoB I. дешифруется в двоичный код, представляющий собой цифровой вм.хол устройства.

Во время действия вырабатываемого элрMCHToiM И в сигнала обнуляется выходной код в блоке 7. . ч,,й„ . ,.,.;,:,:,-.

Прихенемие указанной схемы позволяет устранить ошибку преобразования н повысите точность при преобразовании двухполяркого сигнала.

-ПФ

Формула изобретения

Аналого-цифровой преобразователь, содержащий компараторы, первые входы которых объединены и соединены с первым входом компаратора знака, а вторые входы соединены с выходом формирователя эталонных- напряжений, вход которого соединен с аыходом компаратора знака, а выходы компараторов соединены со входами блока логики, отличающийся тем, что, с целью устранения ошибки преобразования, введены два дополнительных компаратора и элемент И, причем выход формирователя эталонных напряжений соединен через два дополнительных компаратора и элемеит И с управляющим входом блока логики.

Источники информации, принятые во внимание при/экспертизе

I Hu pffSou

Pb/KOff

-и

Авторы

Даты

1979-03-05—Публикация

1977-12-01—Подача