Изобретение относится к области электронной измерительной техники. Известен аналого-цифровой преобразователь параллельно-последовательного действия, содержащий набор компараторов, последовательный делитель, выходы которого подключены к первым входам компараторов, блок цифроаналогового преобразователя, входы которого соединены с выходами компараторов, а выход подключен ко вторим входам компараторов, тактовый генератор и блок управления И Недостатком известного устройств является погрешность преобразования возникающая вследствие существовани входных токов компараторов по цепи последовательного делителя. Наиболее близким по техническому решению является преобразователь 2 содержащий набор компараторов, выходы которых подключены к. входам блока цифроаналогового преобразователя, пе15вые входы подключены к последовательному делителю, а втори входы объединены и подключены к выходу блока ;цифроа«алогового преобр зователя, генераторы тока смещения, подключенные к верхнему и нижнему концам делителя, причем источник си нала соединен с одним из концов делителя . Недостатком этого устройства является погрешность преобразования, возникающая вследствие существования входных токов компаратора по цепи делителя. Целью изобретения является повышение точности преобразователя. Поставленная цель достигается тем, что в параллельно-последовательный амплитудно-цифровой преобразователь, содержащий компараторы, первые входы которых подсоединены к последовательному делителю, вторые входы объединены и подсоединены к выходу цифроаналогового преобразователя, а выходы подсоединены к входам цифро-аналового преобразователя, выходы генераторов токов смещения подсоединены к противоположным концам последовательного делителя, вход первого генератора тока смещения соединен с первым выходом блока управления, второй выход которого соединен со входом цифроаналогового преобразователя, причьм третий выход со входом второго генератора тока смещения, а вход соединен с выходом тактового генератора, дополнительно введен усилитель и суммиру-юащй блок, первый вход которюго соединен со входной источника сигнала, второй вход соединек с входной шиной источника опорного напряжения, а его выход соединен с первым входом усилителя, второй вход .которого соединен с выходом первого генератора тока смещения, а его выход соединен с выходом второго генератора тока смещения.

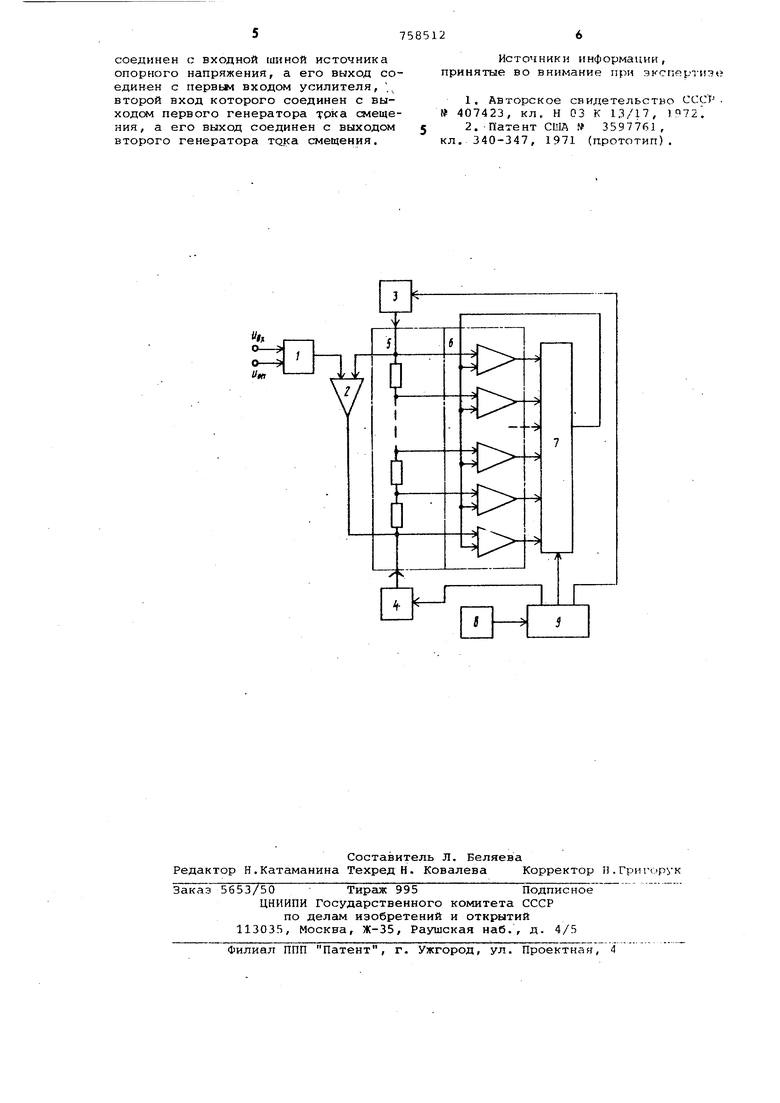

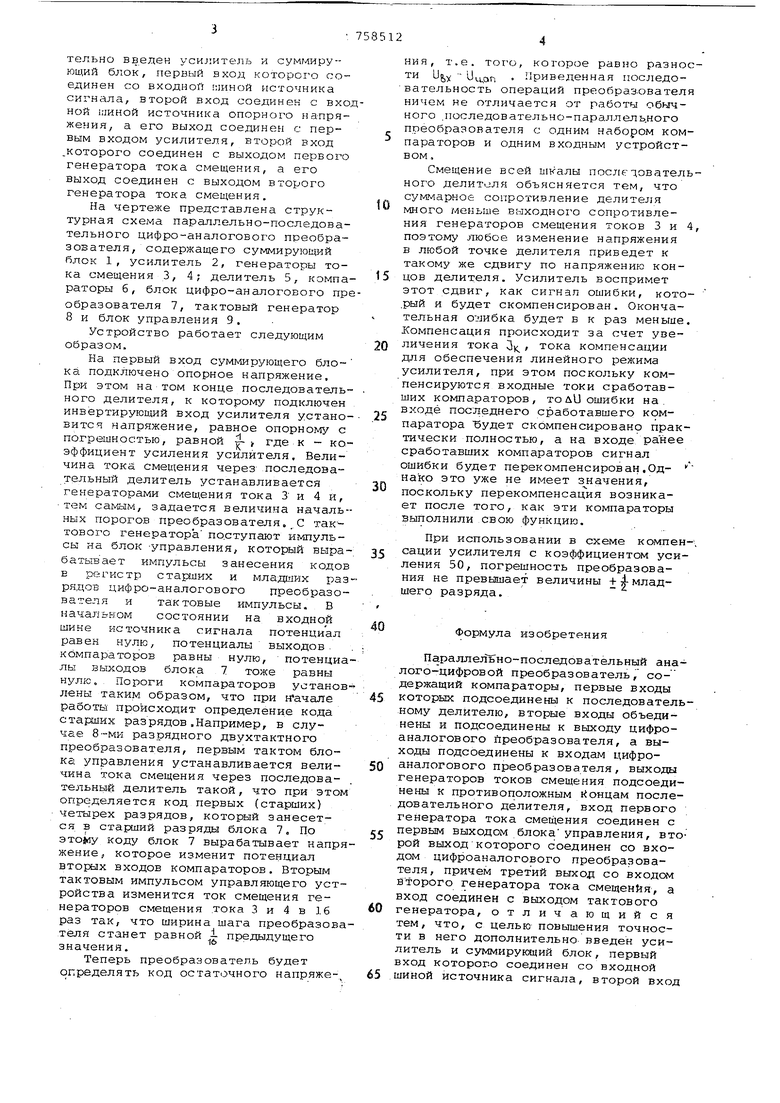

На чертеже представлена структурная схема параллельно-последовательного цифро-аналогового преобразователя, содержащего суммирующий блок 1, усилитель 2, генераторы тока смещения 3, 4; делитель 5, компараторы 6, блок цифро-аналогового преобразователя 7, тактовый генератор 8 и блок управления 9.

Устройство работает следующим образом.

На первый вход суммирующего блока подключено опорное напряжение. При этом на том конце последовательного делителя, к которому подключен инвертирующий вход усилителя установитсл напряжение, равное опорному с погрешностью, равной 4- где к - ко,эффидиент усиления усилителя. Величина тока смещения через последовательный делитель устанавливается генераторами смещения тока 3 и 4 и, тем самым, задается величина начальнь-х порогов преобразователя. С тактового генератора поступают импульсы на блок -управления, который вырабатывает импульсы занесения кодов Е старших и младв:к(х разр55дов цифро-аналогового преобразователя и тактовые импульсы. В начальном состоянии на входной шике источника сигнала потенциал равен нулю, потенциалы выходов. компараторов равны нулю, потенциалы 1зыходов блока 7 тоже равны нулю. Пороги компараторов уставов л-ены таким образом, что при начале работы происходит определение кода старших разрядов.Например, в случае 8-ми разрядного двухтактного преобразователя, первым тактом блока управления устанавливается величина тока смещения через последовательный делитель такой, что при этом определяется код первых (старших) четырех разрядов, который занесется в старший разряды блока 7, По этому коду блок 7 вырабатывает напряжение, которое изменит потенциал вторых входов компараторов. Вторым тактовым импульсом управляющего устройства изменится ток смещения генераторов смещения тока 3 и 4 в 16 раз так, что ширина шага преобразователя станет равной i предыдущего значения.

Теперь преобразователь будет определять код остаточного напряжения, т.е. того, которое равно разности Ufjy - Ui.;,ari Приведенная последовательность операций пре.образ.ователя ничем не отличается от работы обычного .последовательно-параллель.ного преобразователя с одним набором компараторов и одним входным устройством.

Смещение всей шкалы последовательного делителя объясняется тем, что сумг арное сопротивление делителя много меньше выходното сопротивления генераторов смещения токов 3 и 4 поэтому любое изменение напряжения в любой точке делителя приведет к такому же сдвигу по напряжению концов делителя. Усилитель воспримет этот сдвиг, как сигнал ошибки, который и будет скомпенсирован. Окончательная О7либка будет в к раз меньше. Компенсация происходит за счет увеличения тока Д|, тока компенсации для обеспечения линейного режима усилителя, при этом поскольку компенсируются входные токи сработавших компараторов, то &U ошибки на. входе последнего сработавшего компаратора будет скомпенсировано практически полностью, а на входе ранее сработавших компараторов сигнал ошибки будет перекомпенсирован.Од- нако это уже не имеет значения, поскольку перекомпенсация возникает после того, как эти компараторы выполнили свою функцию.

При использовании в схема компен сации усилителя с коэффициентом усиления 50, погрешность преобразования не превьзшает величины +4-младшего разряда.

Формула изобретения

Параллельно-последовательный аналого-цифровой преобразователь, содержащий компараторы, первые входы которых подсоединены к последовательному делителю, вторые входы объединены и подсоединены к выходу цифроаналогового йреобразователя, а выходы подсоединены к входам цифроаналогового преобразователя, выходы генераторов токов смещения подсоединены к противоположным {Концам последовательного делителя, вход первого генератора тока смещения соединен с первым выходом блокауправления, второй выход которого соединен со входом цифроаналогового преобразователя, причем третий выход со входом второго генератора тока смещения, а вход соединен с выходом тактового генератора, отличающийся тем, что, с целью повышения точности в него дополнительно введен усилитель и суммирующий блок, первый вход которог-о соединен со входной .шиной источника сигнала, второй вход

соединен с входной шиной источника опорного напряжения, а его выход соединен с первьи входом усилителя, ,. второй вход которого соединен с выходом первого генератора ТРка смещения , а его выход соединен с выходом второго генератора тока смещения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР . 407423, кл. Н 03 К 13/17, |072. 2. -Патент США № 3597761, кл, 340-347, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1985 |

|

SU1298687A2 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1091331A1 |

| Цифро-аналоговый преобразователь | 1980 |

|

SU949800A1 |

| Цифровой акселерометр | 1984 |

|

SU1242831A1 |

| Устройство аналого-цифрового преобразования для измерения параметров моноимпульсных сигналов | 1980 |

|

SU924849A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Емкостный уровнемер | 1987 |

|

SU1615558A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU711678A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

Авторы

Даты

1980-08-23—Публикация

1977-06-20—Подача