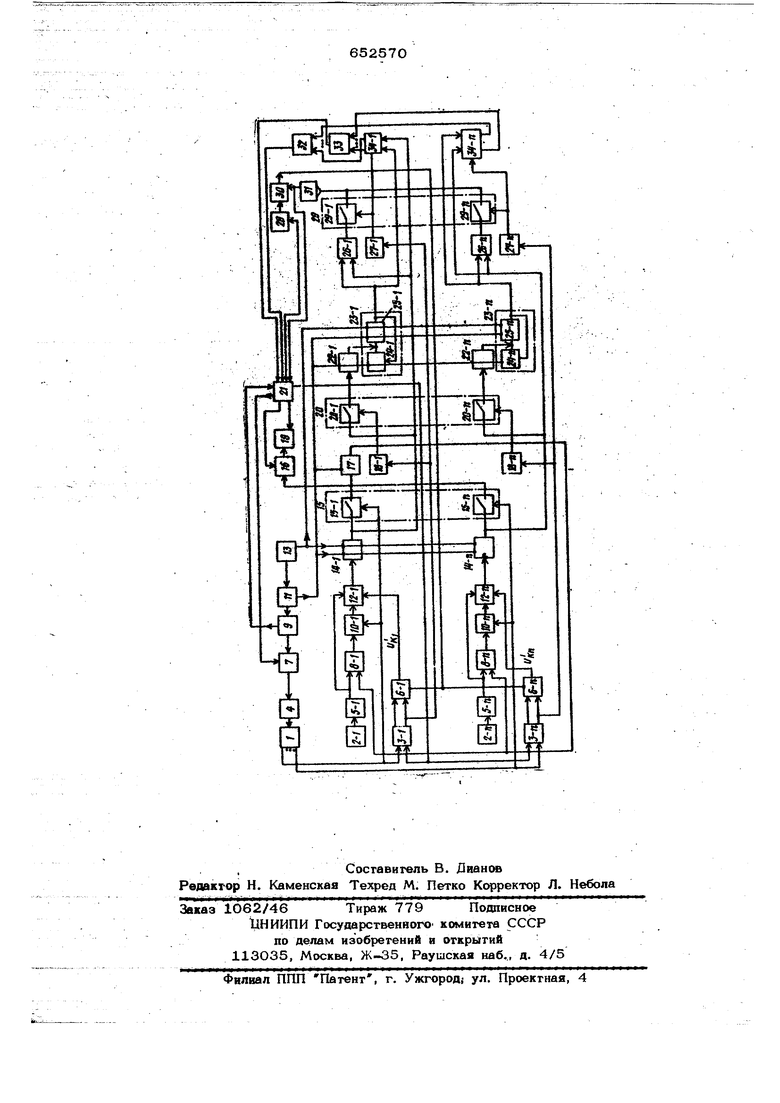

Изобретение относится к обпасти аВтт томатики и вычйспитепьной техники и может быть использовано при построении гибридных (анапого-цифрошлх) измеритель но-вычислительных комплексов. По основному авт. св. № 479119 известно устройство централизованного контроля, содержащее датчики, блоки измерения, коммутатор фаз, аналого-цифровой преобразователь, цифровой регистра тор, генератор тактовых им льсов, счетчик, дешифратор- ас1феделителЬ9 задатчики фазовых уставок, фазовые компараторы, блок допускового контроля, блок управления, управляемый ключ, дифференциальные усилители, управляемые Элементы памяти, аналоговые сумматоры, генератор ступенчатого напряжения, генератор опорных импульсов, масштабные преобразователи напряжения В фа и фазы В напряжение. Недостаток этого устройства заключается В том, что, корректируя статические погрешности прямых звеньев преобраз ования, оно не учитывает динамические погрешности, обусловленные инерционностью звеньев прямого тракта преобразования (главным образом, датчиков) относительно изменения процессов в контролируемом объекте. Цель изобретения заключается в повышении точности контроля путем коррекции динамических погрешностей при сохранении общего принципа построения устройства В виде однородной структуры, использующей ВО всех звеньях преобразования динамические элементы (преобразователи) типа напряжение-фаза и фаза-напряжение, управляемые базисным (общим для всего устройства) набором многозначных 4ункциональных генераторов развертывающих сигналов. Это достигается тем, что в предлагаемое устройство введены дополнительные коммутаторы фаз, многовходовые элементы ИЛИ, последовательно соединенные триггер, второй управляемый ключ и функциональньтй генератор, вход управпения isoToporo и м-осод триггера, соединенный со входом управпения указанного ключа, подключены к блоку управления, и по числу датчиков-двухвходовые элемен- ты ИЛИ; блоки динамической памяти, подключенные к генераторам ступенчатого напряжения и опорных импульсов и че.рез дополнительные преобразователи фаза напряжение - к первому дополнительному коммутатору фаз, блоки определения попярности, выходы которых через многовхо довые элементы ИЛИ подключены к блоку управления, а входы - к выходам преобразователей напряжение - фаза и через соответствующие блоки динамической памяти-к первому допопнитеньному коммутатору фаз; блоки памяти, информационные входы которых подсоединены к выходу второго управляемого кзаача, а выходы соединены со входами аналоговых сумматоров, и логические бпоки, причем первьш входа первых логических блоков подключены к выходу блока управ1Шний, а вторые входы - к выходам дешифратора-распределителя, ко Входам упрйвяяемых элементов памяти и коммутатора фаз, а выходы первых логических блоков соединены со входами блоков памяти, через вторые ло гические блоки - со входами первого, Дополнительного коммутатора фаз и через третьи логические бпоки - со входами соответствующих блоков определения полярности и второго дополнительного коммутатора фаз, выходы которого подключены ко входу триггера, а через д хвходовые элементы ИЛИ - к выходам блоков динамической памяти, преобрезоватейей напряжение-фаза и ко входам первого допопнительного коммутатора фаз и соответствующего бпойа определения полярности. На чертеже показано тфеддагаемое устройство, где 1 - дешифратор-распределитель, 2-1 - 2-П - датчики информативных параметров, 3-1 - 3 -W- первы логическиебпоки,4-счетчик, 5-1 - 5-П Опоки измерения параметра, 6-1 - 6-.fi блоки памяти, 7 - управпяемЪ1й ключ, 8-1 - 8 - и -дифференциальные усилители,. 9 - генератор тактовых импульсов, 10-1 - 1О- П -управляемые элементы памяти, 11 - генератор ступенчатого напряжения, 12-1 - 12- Л -аналоговые сумматоры, 13 - генератор опорных . импульсов, 14-1 - 14-П-грубые маештабные преобразователи напряжения в фазу (Н-Ф), 15 - коммутатор фаз с ключами -15-1 - 15- У|, 16 - аналого-циф- ровой преобразователь (ЛЦП), 17 - точный масштабный преобразователь фазы в напряжение (Ф-Н), 18-1 - 18 - Мвторые логические блоки, 19 - цифровой регистратор (UP), 20 - первый дополнительный коммутатор фаз с ключами 20-1 - 2О-П , 21 - блок управления, 22-i 22-.И-дополнительные масштабные преобразователи фазы в напряжение 1Ф-Н), 23-1 - 23-П-блоки динамической памяти, содержащие 24-1 - 24-П масштабные преобразователи фазы в напряжение (Ф-Н) и 25-1 - 25-ц-масштабнГые преобразователи напряжения h фазу (Н-Ф), 26-1 - 26-м- двухвходовые элементы ИЛИ, 27- 1 - 27-И-третьи, логические блоки , 28 - функциональный, генератор, 29 - второй дополнительный ком1«утатор фаз, содержащий ключи 29-1- 29- П , 30 - второй управляемый ключ, 31 - триггер, 32, 33 - многовходовые элементы ИЛИ, 34-1 - 34-11- блоки определения полярности. Устройство работает следующим образом. Контролируемые параметры с датчиков 2-1 - 2- .П поступают на блоки измерения 5-1 - 5-11 1 снимаются с них в виде изменяющихся напряженийUj((U«. ...,U)( оторые поступают постоянно на входы аналоговых сумматоров 12-1 - 12-П и дифференциальных усилителей 8-1 - 8-П. Один раз зй цикл обегания всех каналов (последовательно для каждого канала) поступающее на вход дифференциального усилителя 8- i напряжение разбаланса (гдеи.,напряжение на выходе масштабного преобразователя Ф-Н 17), фиксируемое управляемым элементом памяти Ю- i (сигнал включения элемента памяти подается с дешифратора-распределителя 1 одновремекно с сигналом включения соответс вующей позиции коммутатора 15- i) и суммируемое с ц,-в аналоговом сумма. торе 12-jl , отрабатывается по цепи обратной связи до чуля, т.е. до равенства Uv. U, . Время отработки кратно периоду тактовых импульсов, вырабатываемых генератором тактовых импуньсов 9, и задается с блока управления 21, управляющего ключом 7. Управляемый ключ 7 на время отработки размыкается и не пропускает эти импульсы на вход счетчика 4, который управляет дешифраторомраспределителем 1. Таким образом, осуществляется остановка коммутатора 15 на несколько тактов на отрабатываемой Позиции. При этом на входы остальньгх суммат ipoB поступают напряжения U и&и, где AUj - напряжение на выходе управ ;ляемого элемента памяти Ю-;j {ди: AU й4 .- - коэффициент дифференциального усилителя 8-j ), полученное в предыдущем цикле стегания, так как блоки памяти сигналом управления с дешифратора-распределителя 1 отключены от выходов дифференциальных ус лителей и сохраняют свое состояние. При этом ,. L, ,, , где К..,- коэффициент преобразования точного п{3еобразоватепя 17 (Ф-Н); Ч преобразованная фаза на выходе i -го преобразователя Н-Ф (14- i ). Выражение-(1) показывает, что точность преоб, разования определяется точным преобразователем фазы в напряжение (Ф-Н) 17, а звенья прямого TpaKta (преобразователи 14- i) могут быть достаточно грубы ми. Кроме статических погрешностей, вносимых узлами прямого тракта преобразов ния, корректируемых описанным выше образом, существуют также и дина ически 5 погрешности, обусловленные инерцион- костью элементов прямого тракта, главным образом, дatчикoв. Эти погрешности в устройстве корректируются образом. В процессе обегания контроли{ емых датчиков 2-1 - 2- П на cooTBeiv ствуюшие дополнительные входы зналоговых сумматоров 12-1 - 12- П поступают напряжения коррекции динамических характеристик иц (с выходов блоков паияти 6-1 - 6- п). Корректирующие напряжения U„ -вырабатываются путем разновременного сравнения фаз. При этом фаза с выхода табного преобразователя Н-Ф 14- ключ первого дополнительного коммутатора фаз 20 (2О- i) поступает на вход масштабного преобразователя (Ф-Н) 22- 1 , который преобразует ее в на. пряжение. С выхода дополнительного преобразователя Ф-Н 22- i напряжение Подается на вход блока динамической памяти 23- 1 и запоминается им на время двух полных циклов (периодов) обегания контролируемых датчиков 2-1 - 2-П так как вторые логические блоки 18-;1 - 18-ц, управляемые импульсами с вы)Хода деши4чэатора-распределитейя 1 через соответствующие первые логические блоки 3-1 - 3-П , обеспечивают повтор; ное подключение ключей 20-1 - 2О- h первого дополнительного коммутатора фаз 20 с пропуском одного цикла. При дополнительной обработке используются не заломненные, блоками динамической памяти 23-1 - 23-п уровни напряжений, а соответствующие им фазы, снимаемые с выходов преобразователей Н-Ф 25-1 - 25- П этих блоков. В следующем цикле подключаются ключи 29-1 - 29- п второго дополнительного коммутатора фаз 29, управляемые третьими логическими блоками 27-i -27- П 5 которые также подключены к выходам первых логических блоков 3-1 -3i-п. При этом вторые логические блоки 18-1 - 18-И и третьи логические блоки 27-1 - 27-п осуществляют коммутацию разновременно со сдвигом на период., . Ключи второго дополнительного коммутатора фаз 29 коммутируют фазы с выходов блоков динакягческоЙ памяти 2 - 2 3- п и выходов масштабных преобразователей Н-Ф 14-1 - 14- я через соответствующие двухвходовые элементы ИЛИ 26-1 -26-м на вход триггера 31, Который выполняет вычитание фаз, характеризующих измеряеьлую величину в двух последовательных циклах контроля для каждого датчика в отдельности. Тем. самым, выделяются признаки, характеризуюшие скорость изменения выходных сигналов каждого датчика 2- i в виде приращения преобразованных фаз за время одного цикла. Триггер 31 работает в счетном режиме, первой фазой он устанавливается в рабочее положение и открывает второй управляемый ключ 30, а второй фазой он сбрасывается и закрывает указанный За время дЧ, когда второй управляемый ключ ЗО открыт, напряжение с выхода функционального генератора 28, учитывающее скорость изменения сигнала на выходе датчика 2- i , поступает на информационные входы блоков памяти 6-1 - 6- П, один из которых, подключенный к i -му выходу дешифратора 1 через первы логический блок 3-1 , запоминает корректирующий сигнал и передает его на дополнительный вход анало14)вого сумматора 12- i . Функциональный генератор 28 защгскается блоком управления 21, который, в свою очередь, связан с выходом триггера 31 и выполняет оценку информати ности выдепенных отклонений Д%-, т.е. необходимость выполнения коррекции. Генератор 28 апп роксимирует динамическую поправку с учетом усредненной .динамической (например переходной) характеристики датчиков. В случае необХбйймости аппроксимирующая функция генератора 28 может изменяться по сиг налам с бпока управления 21 в зависимости . от Величин накапливаемых откпоненийЛ Сигналы, вырабатываемые блоком управления 21, учитывают не только абcoWTHSie значения текущих и предшестйующих отклонений , но и их знаки. Информация о знаке отклонения вырабатывается в блоках определения пбпярнрсти 34-1 - 34- п, которые управляются с выходов третьих логических бйоков 27-1 т 27-n, благодаря сигналы +, вьфабатываёмыё многовхбдбШш элементом ИЛИ 33, или -, вырабатываемые аналогичным элементом 32, поступают на входы блока управления 21 синхронно с сигналом ОТ ШОНвНИЯ в соответствующем канапе. Аналоговый сумматор 12- суммирует напряжение с вьгхода блока измерения S-iy.ii корректирующие напряжения напряжение разбаланса Д U с выхода управляемого элемента памяти 10-1, а также напряжение динамической коррекции и с выхода блока памяти 6- i . Сум марное напряжение с выхода сумматора 12- i преобразуется S фа масштабным преобразователем 14- i с некоторой погрешностью прямого тракта , котррая как указано вьппе, раз за цикл t послед овательно для каждого канала) отрабатывает .ся по цепи обратной связи до нуля. Во время отработки время стШИя коммутатора . фаз 15 на соотбетстбующей позиции 15- i увепичивается на время, кратное периоду тактовых импульсов генератора 9.. Первый логический блок 3- t , управляемый сигналами с блока управления 21, во время обегания контролируемых каналов передает по первому выходу сигналы с дешифратора-распределителя 1 б§з изменения на входы, элементов 6-1, 18-1,27- i .Во время отработки напряжени разбаланса логический блок выделяет из всего времени стояния на

данной позиции такт, равный перио тактоЬых импульсов генератора 9, в тезадается блоком управления 21, который одновременно управляет работой аналогочение которого происходит обычным поряд ком ирмеренне, преобразование и регистрация. В конце этого периода блок 3вырабатывает по второму выходу ямпупьс, запрещающий прохождение сигнапа с бпока памяти 6- f на вход сумматора 12- 1 . Оставшееся время стояния на i -и позиции используется дпя собственно отработки, т.е. коррекции прямого тракта преобразования. В течение этого времени сигналами с блока управления 21 запрещается измерение аналого-цифровым . преобразователем 16 контролируемых niapiaMeTpOB и регистрация этих параметров цифровым регистратором 19. Работа блока управйеяия синхронизирована генератором тактовых импульсов 9. Каждый канал корректируется один раз за цикл опроса (т.е. за П циклов опроса корректируются все i кaнaпoв, при этом остальные (некорректируемые) каналы охфашиваю.Рся с частотой генератора 9. Частота генератора 9 синхронизирована частотой генератора ступенчатого напряжения 11. Частота f j генератора 11, в свою очередь, связана с частотой f генератора опорных импупьсов 13 зависимостью -ii, m- m где m - число состояний блоков дина- , мической памяти 23-1 - 23-П , выбираемое исходя из требуемой разрещающей способности преобразования. В связи с тем, что коррекция динамических погрешностей выполняется на основе отработки ДЧ,- , полученных путем разновременного сравнения теку-, 7яёй фазы с запомненным значением, полученным в предыдуицем цикле, корректура получается с запаздыванием во времени на один цикл. Во избежание этого при „. больщой скорости изменения сигнапа может быть выполнена либо упреждающая (экстраполирующая) коррекция в одном из холостых циклов (тогда следующий цикл будет скорректирован без запаздывания и без упреждения), либо для каждого контролируемого канала, в котором сонаружено значительное изменение AHj, может быть введен дополнительный расчетный такт, в течение которого вводится соответствующая динамическая поправка. Тот ипи иной алгоритм коррекции Цифрового преобразователя 16 таким образом, что поспедний отображает скоррек тированные значения информативных параметров. Фор,мула изобретения Устройство для централизованного контроля по авт. свид. №479119, отпинающееся тем, что, С Пёпыо повышения точности устройства, в него введены дополнительные коммутаторы фаз, многовходовые элементы ИЛИ, последовательно соединенные тригпер, второй управляемый ключ и функциональный генератор, вход управления которого и выход триггера, соединенный со вхо дом управления указанного ключа, подключены к блоку управления, и по числу. датчиков - двухвходовые элементы ИЛИ, :блоки динамической памяти, подключен ные к генераторам ступенчатого напряжения и опорных импульсов и через допотштепьяые преобр ователи фаза- напряжение - к первому дополнительному коммутатору фаз, блоки определения полярности, выходы которых через многовходовые элементы ИЛИ подключены к блоку управления, а входы - к выходам преобразователей н&пряжение-фвза и через соответствующие блоки динамической памяти к первому дополнительному коммутатору фаз; блоки памяти, информационные которых подсоединены к выходу второго управляемого кшоча, а выходы соединены со входам1в аналоговых сумматоров, и логические блоки, причем первые входы первых лот ических блоков подключены к выходу блока управления, а вторые входы - к выходам деши4фатора-распределитепя, ко входам упра1&пяемых элементов памяти я коммутатора фаз, а выходы первых логических блоков соединены со входами блоков памяти, через вторые логические блоки - со входами первого допоннитепьногО коммутатора фаз и через третьи логические блоки - со входами соответствующих блоков определения полярности и второго дополнительного коммутатора фаз, выхошл которого подключены ко входу триггера, а входы через двухвходовые элементы ИЛИ - к выходам блоков динамической памяти, преобразователей напряжение фаза и ко входам первсво дополнительного коммутатора фаз и соответствующего блока определения полярности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Цифроаналоговая следящая система | 1986 |

|

SU1405025A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| Устройство для автоматической компенсации емкостного тока однофазного замыкания на землю | 1982 |

|

SU1107214A1 |

| Устройство для измерения показателей качества электроэнергии трехфазной сети | 1982 |

|

SU1064233A1 |

| Устройство измерения параметров дисбаланса | 1990 |

|

SU1795318A1 |

| Устройство для цетрализованного контроля | 1976 |

|

SU661515A1 |

| Устройство для централизованного контроля | 1973 |

|

SU479119A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство контроля | 1985 |

|

SU1291931A1 |

Авторы

Даты

1979-03-15—Публикация

1974-11-15—Подача