Изобретение относится к вычислительной технике и может быть использовано для повышения производительности цифровых вычислительных машин (ЦВМ). Известен также мультиплексный канал 1, в котором повышение производительности и пропускной способности достигается за счет сокраш,ения обращений в оперативное запоминающее устройство (ОЗУ) за командной информацией. Наиболее близким предлагаемому устройству по технической сущности и структуре является мультиплексный канал ЦВМ системы IBM-360 2, содержащий регнстр номера подканала, вход которого соединен с первым входом мультиплексного канала, регистр команд ввода-вывода, вход которого соединен со вторым входом мультиплексного канала, а выход - со входом блока памяти подканала, связанным двухсторонней связью с регистром активного подканала, вход и выход которого соединен с первым входом и выходом регистра связи с интерфейсом, второй вход и выход которого соединен с первым входом и выходом узла связи с ОЗУ, а третий вход и выход - подключен к первому входу-выходу мультиплексного канала, причем второй вход и выход узла связи с ОЗУ соединен со вторым входом-выходом мультиплексного канала, а третий выход - подключен к регистру активного подканала; устройство управления, первый выход которого подключен к выходу мультиплексного канала, а первый вход-выход - к входу-выходу регистра номера подканала, второй вход-выход - к входу-выходу регистра команд вводавывода, третий вход-выход - к третьему входу-выходу узла связи с ОЗУ, четвертый вход-выход - к четвертому входу- выходу регистра связи с интерфейсом, пятый вход-выход - к третьему входу-выходу регистра активного подканала, шестой вход-выход - к второму входу-выходу блока памяти подканала. Недостатком канала - прототипа, присущим также другим рассмотренным аналогам, является потеря производительности ЦВМ, связанная с простоем оборудования процессора во время ожидания результатов запуска периферийных устройств. Целью предлагаемого изобретения является повышение производительности ЦВЛ1 путем исключения ожидания процессором

результатов запуска периферийного устройства.

Поставленная цель достигается тем, что в мультиплексном канале введены дешифратор, блок формирования очереди, шифратор, причем выходы регистра номера подканала через дешифратор, блок формирования очереди и шифратор подключены к адресным входам блока памяти подканалов, причем блок формирования очереди связан двусторонней связью с устройством управления.

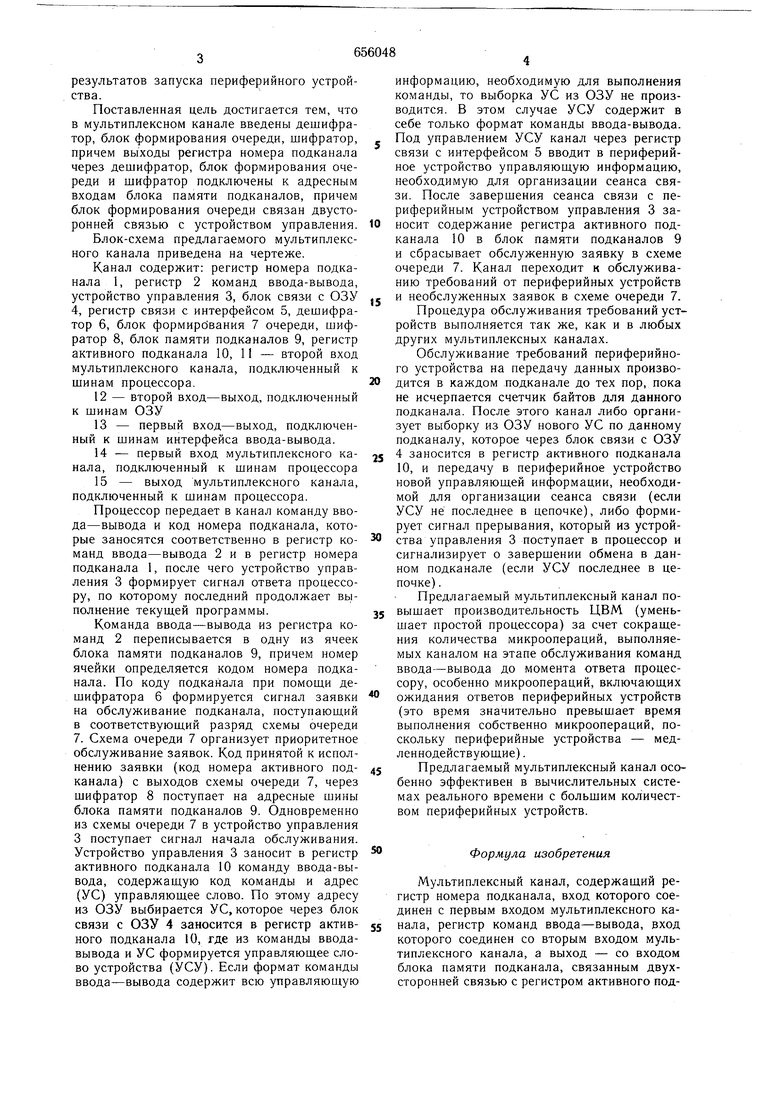

Блок-схема предлагаемого мультиплексного канала приведена на чертеже.

Канал содержит: регистр номера подканала 1, регистр 2 команд ввода-вывода, устройство управления 3, блок связи с ОЗУ 4, регистр связи с интерфейсом 5, дешифратор 6, блок формирбвания 7 очереди, шифратор 8, блок памяти подканалов 9, регистр активного подканала 10, 11 - второй вход мультиплексного канала, подключенный к шинам процессора.

12- второй вход-выход, подключенный к шинам ОЗУ

13- первый вход-выход, подключенный к шинам интерфейса ввода-вывода.

14-- первый вход мультиплексного канала, подключенный к шинам процессора

15- выход мультиплексного канала, подключенный к шинам процессора.

Процессор передает в канал команду ввода-вывода и код номера подканала, которые заносятся соответственно в регистр команд ввода-вывода 2 и в регистр номера подканала 1, после чего устройство управления 3 формирует сигнал ответа процессору, по которому последний продолжает выполнение текуш.ей программы.

Команда ввода-вывода из регистра команд 2 переписывается в одну из ячеек блока памяти подканалов 9, причем номер ячейки определяется кодом номера подканала. По коду подканала при помощи дешифратора 6 формируется сигнал заявки на обслуживание подканала, поступаюш,ий в соответствующий разряд схемы очереди 7. Схема очереди 7 организует приоритетное обслуживание заявок. Код принятой к исполнению заявки (код номера активного подканала) с выходов схемы очереди 7, через шифратор 8 поступает на адресные шины блока памяти подканалов 9. Одновременно из схемы очереди 7 в устройство управления 3 поступает сигнал начала обслуживания. Устройство управления 3 заносит в регистр активного подканала 10 команду ввода-вывода, содержащую код команды и адрес (УС) управляющее слово. По этому адресу из ОЗУ выбирается УС, которое через блок связи с ОЗУ 4 заносится в регистр активного подканала 10, где из команды вводавывода и УС формируется управляющее слово устройства (УСУ). Если формат команды ввода-вывода содержит всю управляющую

информацию, необходимую для выполнения команды, то выборка УС из ОЗУ не производится. В этом случае УСУ содержит в себе только формат команды ввода-вывода. Под управлением УСУ канал через регистр связи с интерфейсом 5 вводит в периферийное устройство управляющую информацию, необходимую для организации сеанса связи. После завершения сеанса связи с периферийным устройством управления 3 заносит содержание регистра активного подканала 10 в блок памяти подканалов 9 и сбрасывает обслуженную заявку в схеме очереди 7. Канал переходит к обслуживанию требований от периферийных устройств и необслуженных заявок в схеме очереди 7.

Процедура обслуживания требований устройств выполняется так же, как и в любых других мультиплексных каналах.

Обслуживание требований периферийного устройства на передачу данных производится в каждом подканале до тех пор, пока не исчерпается счетчик байтов для данного подканала. После этого канал либо организует выборку из ОЗУ нового УС по данному подканалу, которое через блок связи с ОЗУ 4 заносится в регистр активного подканала 10, и передачу в периферийное устройство новой управляющей информации, необходимой для организации сеанса связи (если УСУ не последнее в цепочке), либо формирует сигнал прерывания, который из устройства управления 3 поступает в процессор и сигнализирует о завершении обмена в данном подканале (если УСУ последнее в цепочке) .

Предлагаемый мультиплексный канал повышает производительность ЦВМ (уменьшает простой процессора) за счет сокращения количества микроопераций, выполняемых каналом на этапе обслуживания команд ввода-вывода до момента ответа процессору, особенно микроопераций, включающих ожидания ответов периферийных устройств (это время значительно превышает время выполнения собственно микроопераций, поскольку периферийные устройства - медленнодействующие) .

Предлагаемый мультиплексный канал особенно эффективен в вычислительных системах реального времени с большим количеством периферийных устройств.

Формула изобретения

Мультиплексный канал, содержащий регистр номера подканала, вход которого соединен с первым входом мультиплексного канала, регистр команд ввода-вывода, вход которого соединен со вторым входом мультиплексного канала, а выход - со входом блока памяти подканала, связанным двухсторонней связью с регистром активного подканала, вход и выход которого соединен с первым входом и выходом регистра связи с интерфейсом, второй вход и выход которого соединен соответственно с первым входом и выходом узла связи с оперативным запоминающим устройством, а третий вход и выход подключен к первому входу-выходу мультиплексного канала, причем второй вход и выход узла связи с оперативным запоминающим устройством соединен со вторым входом-выходом мультиплексного канала, а третий выход - подключен к регистру активного подканала; устройство управления, первый выход которого подключен к выходу мультиплексного канала, а первый вход-выход подключен к входу-выходу регистра номера подканала, второй вход-выход - к входу-выходу регистра команд ввода-вывода, третий вход-выход- к третьему входу-выходу узла связи с оперативным запоминающим устройством, четвертый вход-выход - к четвертому входу- выходу регистра связи с интерфейсом, пятый вход-выход к третьему входу-выходу регистра активного подканала, щестой вход- выход к второму входу-выходу блока памяти подканала, отличающийся тем, что, с целью повыщения производительности в устройство введены дешифратор, блок формирования очереди, шифратор, причем выход регистра номера подканала, через дешифратор, блок формирования очереди и шифратор подключен к адресн лм входам блока памяти подканалов, причем блок формирования очереди связан двухсторонней связью с устройством управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 478308, кл. G 06 F 3/06, 1974, 2.Коган Б. М., Каневский М. М. Цифровые вычислительные машины и системы. М., «Энергия, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1978 |

|

SU744540A2 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Устройство для вывода информации | 1981 |

|

SU960788A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для назначения подканалов | 1984 |

|

SU1264189A1 |

| Система обмена | 1978 |

|

SU809138A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Мультиплексный канал | 1979 |

|

SU860048A1 |

Авторы

Даты

1979-04-05—Публикация

1977-01-24—Подача