(54) УСТРОЙСТВО ДЛЯ JEftlBOflA ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Мультиплексный канал | 1977 |

|

SU656048A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

Изобретение относится К вычисга1тельной технике и может быть использовано для вывода информации на ;электронно-лучевые трубки и другие ;Внешние устройства, которые требуют .регенерации выводимой информации.

Известно устройство, содержащее регистр номера подканала, регистр команд, устройство управления, блок связи с ОЗУ/ регистр связи с интерфейсом, дешифратор, блок памяти подканалов, регистр активного подканала, блок формирования очереди и шифратор tl.

Недостатком этого устройства является низкое эффективное быстродействие ЦВМ из-за потерь мгшшнного времени на организацию обмена инфор1мацией.

Известно устройство, содержащее формирователь адреса, регистр связи и коммутатор, причем первый вход регистра связи соединен с выходом/Коммутатора, вход которого подключен к первому выходу регистра связи, в котором с целью повышения быстродействия введены синхронизато{, шифратор, блок оперативной памяти и блок долговременной памяти, причём выход синхронизатора через ш фратор соединен

.с первым входом формироцателя адреса, второй вход которого подключен к первому выходу блока долговременной памяти,второй выход которого соединен с вторым входом регистра связи, а вход блока долговременной памяти подключен к выходу формирователя адреса и первому входу блока оперативной памяти, второй вход которого сое10 с вторым выходом регистра связи, а выход блока оперативной памяти подключен к третьему входу регистра связи С2.

15

однако недостатком этого устройства является отсутствие возможности модификации адресной части командных слов, хранимых в блоке долговременной памяти, что не позволяет по

20 одному командному слову вести вывод информации из различных областей блог ка оперативной памяти. Кроме того, устройство не позволяет использовать одни и те же подпрограммы для отво25да информации на различные устройства, оно не позволяет оперативно по командам процессора изменять программа вывода.

Целью изобретения является расши30рение области применения устройства

путем модификации адресной части командных слов.

Поставленная цель достигается тем что в устройство для вывода информации, содержащее первый блок памяти, второй блок памяти, первый формирова тель адреса, шифратор, первый регист первый выход первого блока памяти и второго блока памяти соединены (соответственно с первым и вторым входами первого регистра, выход кото рого является первым выходом устройства, введены сумматор адреса, треTmVi, четвертый и пятый блоки памяти второй формирователь адреса, второй и третий регистры, формирователь оче реди запроса, первый вход второго блока памяти является первым входом устройства и соединен с входом второго регистра, с первыми входами третьего, четвертого и пятого блоков памяти, вторые входы которых соединены с выходом шифратора и третьим входом первого регистра, первые выходы тре тьего, четвертого и пятого блоков памяти являются вторым выходом устройства, второй выход третьего блока памяти является третьим i выходом устройства и соединен с входом первого формирователя адреса, выхЬд которого соединен с третьим входом третьег блока памяти, второй выход четвертого блока памяти соединен с входом первого блока памяти и .входом второг формирователя адоеса, вуход которого соединен с третьим входом четвертого блока памяти, второй илход пятого блока памяти соединен с первым входом суиматора адреса, второй вход которого соединен с вторым выходом первого блока памяти, выход суыматор.а адреса соединен с вторым входом второго блока памяти, третий вход KOTQporo является вторым входом устройства, выход третьего регистра соединен с первым входом формирователя очереди запроса, второй вход которого соединен с выходом второго регистра, выход формирователя очереди запроса соединен с входом шифратора, вход третьего регистра является третьим взводом устройства.

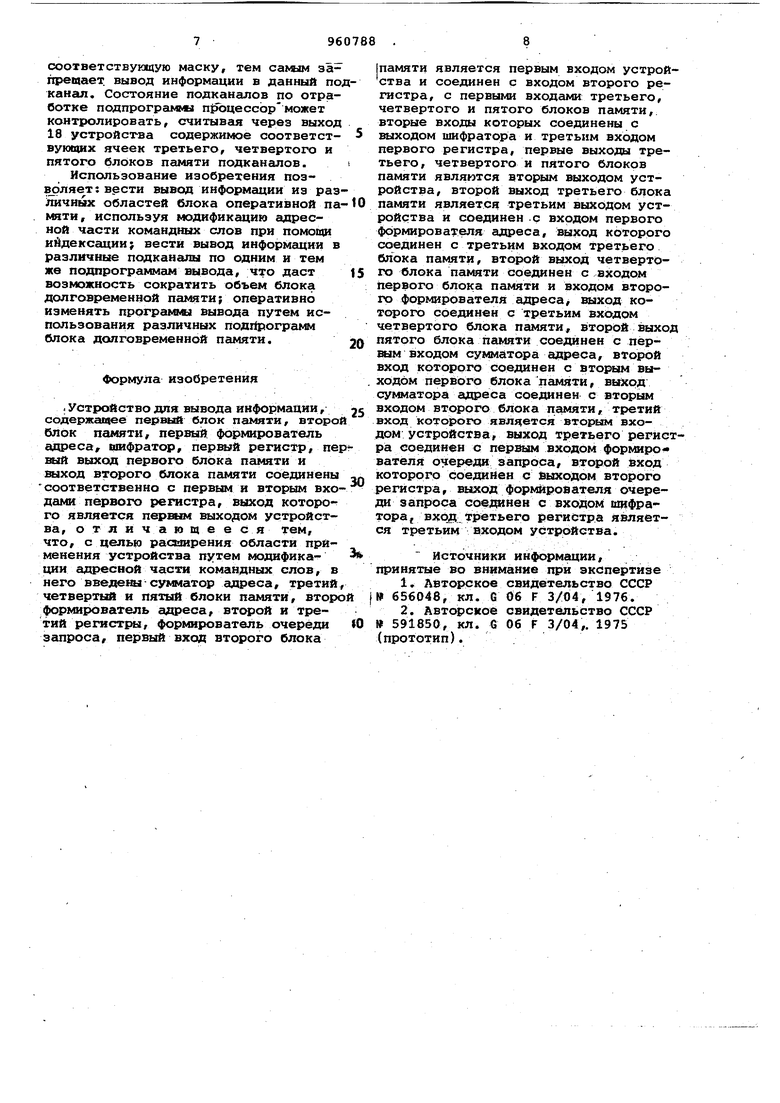

На чертеже изображена структурная схема устройства.

Устройство содержит первый блок 1 рамяти, сумматор 2 адреса, второй ёлок 3 памяти, первый регистр 4, амфратор 5, третий блок 6 памяти, четвертый блок 7 памяти, пятый блок 8 памяти, первый формирователь 9 адреса, второй формирователь 10 ..адрёг са, формирователь 11 очереди.запроса, второй регистр 12, третий регистр 13, первый вход 14 устройства, второй вход 15 устройства, третий вход 16 устройства, первый выход 17 устройства, второй выход 18 устройства, третий выход 19 устройства.

Блок 1 памяти предназначен для долговременного хранения подпрограмм илвода информации.

Сумматор 2 адреса формирует исполнительный адрес блока 3 памяти.

Блок 3 памяти предназначен для хранения информации, поступающей из процессора, и является блоком оперативной памяти.

Первый регистр 4 предназначен для промежуточного хранения управляющей иформсщии, выдаваемой в подканал.

Третий блок 6 памяти предназначен для хранения текущих адресов подпрограмм вывода, находящихся в памяти процессора.

Четвертый блок 7 памяти предназначен для хранения текущих адресов подпрограмм вывода, находящихся в блоке 1 памяти.

Пятый блок 8 памяти содержит индекс элементов выдаваемой информации

Формирователи 9 и 10 адреса служат для модификации адресов программ вывода, находящихся в памяти процессора, и подпрограмм из блока 1 памят

Второй регистр 12 представляет собой регистр маски.

Третий регистр 13 предназначен для хранения признака состояния подкналов.

Входы 14 - 16 устройства предназначены для приема управлякацей информации .

Выходы 1.7 - 19 устройства предназначены для вывода информации.

Устройство работает следующим образом.

Для каждого подканала в оперативной памяти процессора формируется программа вывода. Эта программа представляет последовательность управляюдах слов (УС). В УС указывается начальный адрес подпрограммы вывода, хранящейся в блоке 1 памяти, и индекс элементов, которые должны выводиться по этой подпрограмме. Последнее слово программы вывода содержит признак конца пpoгpaм 4:I вывода и начальный адрес этой программы в оперативной памяти процессора.

подпрограмма вывода информации представляет последовательность командных слов, хранимых в блоке 1 памяти.

Командное слово имеет следующую структуру: адрес абонента в подканале (для электронно-лучевой трубки это могут быть: регистр координат, ргистр отклонения по координатам X и Y, цифроаналоговые преобразователи и т.д.); адресная часть, определяюща область нахождения управлякяцей информации в блоке 3 пагляти, поле признаков (признак индексации, признак конца сеанса связи, признак конца подпрограммы вывода). .

Начальные адреса сформированных подпрограмм вывода записываются в ячейки третьего блока б памяти подканалов через информационный вход 14 устройства по командам процессора.

Информация для вывода записывается 5 в блок 3 памяти через вход 14 устройства по адресу, подаваемому на вход 15 устройства.

Запуск устройства на вывод информации осуществляется установкой Ю через вход 14 устрбйст ва соответствукадей маски во второй регистр 12. Единичное состояние разряда регистра 12 маски указывает на готовность информации.для вывода в данный под- 15 канал.

Готовность подканала к приему информации определяется третьим регистром 13 состояния подканалов. Единичное состояние соответствующего разря- 20 да данного регистра указывает на готовность к приему информации данным подканалом. ,

По начальному пуску формирователь очереди запуска определяет номер при- 25 оритетного подканала и через шифратор 5 передает его на адресные входы блоков 6 - 8 памяти подканалов и вход первого регистра 4. По этому адресу из блока 6 памяти выбирается нача- л льный адреспрограммы вывода, которой через выход 19 устройства подается в память процессора, а также в первый формирователь 9 адреса. Производится обращение к памяти процессора и первое. управлякядее слово программь через вход 14 устройства записывается в четвертый 7 и пятый В блоки подканалов по адресу, определяемому шифратором 5. В четвертый блок 7 памяти подканалов записывается начальный ад- 0 рее подпрограммы вывода, а в пятыйблок 8 памяти - индекс выдаваемых до данной пoдпpoгpa 4мe элементов. Модифицированный адрес с выхода первого формирователя 9 адреса переписыва- 45 1ется в третий блок 6 памяти. Отработка подпрограммы вывода на чинается с обращения к четвертому 7 |и пятому 8 блокам памяти подканалов. |Из ячейки четвертого блока, 7 памя- 50 ти подканалов с адресом, равным номеру активного подканала, выбирается адрес командного слова подпрограмкы, который подается в блок 1 памяти и во второй формирователь 10 адреса. jj Производится обращение к блоку 1 памяти и выборка из него командного слова. Адресная часть командного слова подается на один из входов сумматора 2 адреса, на другой вход которого подается индекс из пятого блока 8 памяти. С выхода сумматора 2 адреса исполнительный адрес подается на вход блока 3 памяти. Производится обращение к этому блоку и информация с его выхода переписывается в регистр

При выборке/командного слова с призиаком конца сеанса связи устройство устанавливает соответствующий разряд третьего регистра 13 состояния подканалов в нулевое состояние, тем сакым снимает подканал с обслуживания. Подканал ставится в очередь на обслуживание после окончания отработки управляющей информации и выработки им сигнала; который устанавливает соответствующий разряд регистра состояния подканалов в единичйое состояние

Форитрователь 11 очереди запроса олбирает следующий подканал. Его номер с выхода шифратора 5 подается на адресные входы блоков б . 8 памяти подканалов и вход регистра 4. Далее отработка подпрограмкы ведется аналогично.

При считывании из блока 1 командного йлова с признаком конца подпрогра фи устройство организует цикл обращения к памяти процессора по адресу, выбираемому из. третьего блока 6 памяти подканалов. Управляющее слово записывается в четвертый 7 и пятый 8 блоки памяти подканалов. На этом обслуживание данного подкаНсша заканчивается и устройство переходит к обслуживанию следующего подканала.

Если при обращении к памяти процессора за следующим управляющим словом приходит управляющее слово с признаком конца программы вывода, то устройство производит запись начльного адреса программы из этого управляющего слова в третий блок 6 памяти подканалов череэ информационный вход 14.

Затем устройство организует цикл обращения к памяти процессорна за первым управляющим словом nporpaMNSJ данного подканала, которое записывается в четвертый 7 и пятый 8 блоки памяти подканалов.

На этом обслуживание данного подканала заканчивается и устройство переходит к обслуживанию следующего подкангша.

Для изменения пррграмки вывода какого-либо подкансШа процессор ставит соответствующую маску, тем самым запрещает, вывод информации в данный по канал. Состояние подканалов по отработке подпрограммы niJoueccbp может контролировать, считывая через выход 18 устройства содержимое соответствуюцих ячеек третьего, четвертого и пятого блоков памяти подканалов. Использование изобретения позволяет: вести вывод информации из раз личных областей блока оперативной па мяти, используя модификацию адресной части командных слов при помощи индексации; вести вывод информации в различные подканалы по одним и тем же подпрограммам вывода, что даст возможность сократить объем блока долговременной памятиi оперативно изменять программа вывода путем использования различных подпрограмм блока долговременной памяти. Формула изобретения Устройство для вывода информации, содержащее первый блок памяти, второ блок памяти, первый формирователь адреса, шифратор, первый регистр, пе wM выход первого блока памяти и вахоа второго блока памяти соединены соответственно с первым и вторым вхо дами первого регистра, выход которого является первым выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства путем модификации адресной части командных слов, в него BBejc HH сумматор адреса, третий четвертый и пятый блоки памяти, втор формирователь адреса, втсфой и третий регистры, формирователь очереди запроса, первый Bxctfl второго блока (памяти является первым входом устройства и соединен с входом второго регистра, с первыми входами третьего, четвертого и пятого блоков памяти, вторые входы которых соединены с выходом шифратора и третьим входом первого регистра, первые выходы третьего, четвертого и пятого блоков памяти являются вторым выходом устройства, второй выход третьего блока памяти является третьим выходом устройртва и соединен -с входом первого формирователя адреса, выход которого соединен с третьим входом третьего блока памяти, второй выход четвертого блока памяти соединен с входом первого блока памяти и входом второго формирователи адреса, выход которого соединен с третьим входом четвертого блока памяти, В1торой выход пятого блока памяти соединен с первым входом сумматора адреса, второй вход которого соединен с вторым выходом первого блока памяти, выход сумматора адреса соединен с вторым входом второго блока памяти, третий вход которого является вторым входом устройства, выход третьего регистра соединен с первым входом формиро вателя очереди запроса, второй вход которого соединен с бьлходом второго регистра, выход формирователя очереди запроса соединен с входом шифратора, вхол третьего регистра является третьим входом устройства. Источники информации/ принятые во внимание при экспертизе 1.Авторское свидетельство СССР 656048, кл.С 06 F 3/04, 1976. 2.Авторское свидетельство СССР 591850, кл. 6 06 F 3/04,. 1975 (прототип).

bs

(г

5

Авторы

Даты

1982-09-23—Публикация

1981-01-07—Подача