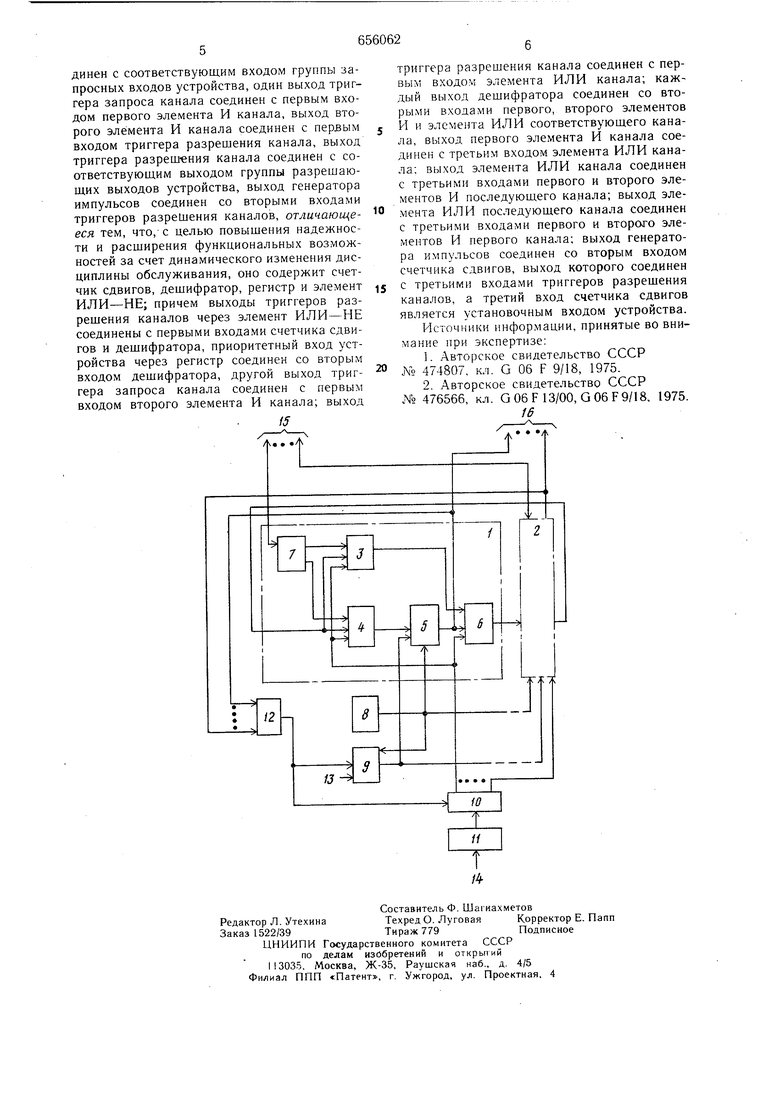

(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА второго элемента И канала соединен с первым входом триггера разрешения канала, выход триггера разрешения канала соединен с соответствующим выходом группы разрешающих выходов устройства, выход генератора импульсов соединен со вторыми входами триггеров разрешения каналов, введены счетчик сдвигов, дещифратор, регистр и элемент ИЛИ-НЕ. Выходы триггеров разрешения каналов через элемент ИЛИ-НЕ соединены с первыми входами счетчика сдвиРОВ и дещифратора. Приоритетный вход устройства через регистр соединен со -вторым входом дешифратора. Другой выход триггера запроса канала соединен с первым входом второго элемента И канала. Выход триггера разрешения канала соединен с первым входом элемента ИЛИ канала. Каждый выход дешифратора соединен со вторыми входами первого, второго элементов И и элемента ИЛИ соответствующего канала. Выход первого элемента И канала соединен с третьим входом элемента ИЛИ канала, выход элемента ИЛИ канала - с третьими входами первого и второго элементов И последующего канала. Выход элемента ИЛИ последнего канала соединен с третьими входами первого и второго элементов И первого канала. Выход генератора импульсов соединен со вторым входом счетчика сдвигов, выход которого соединен с третьими входами триггеров разрешения каналов, а третий вход счетчика сдвигов является установочным входом устройства. Структурная схема устройства представлена на чертеже. Каждый канал 1, 2 многоканального устройства приоритета содержит элементы И 3, 4, триггер разрешения 5, элемент ИЛИ 6 и триггер запроса 7. Устройство содержит также генератор 8 импульсов, счетчик сдвигов 9, дешифратор 10, регистр 11, элемент ИЛИ-НЕ 12, установочный вход 13, приоритетный вход 14, группу 15 запросных входов и группу 16 разрешающих выходов. Устройство работает следующим образом. В начальный момент все триггеры разрешения 5 каналов 1, 2 обнулены. Триггеры запроса 7, на которые не поступил запрос, также обнулены и своими выходами блокируют второй элемент И 4 и включают первый элемент И 3 соответствующего канала. На выходе элемент ИЛИ-НЕ 12 - присутствует сигнал «единица. При поступлении импульсов сдвига от генератора 8 эта «единица переписывается в триггер разрешения канала 1, если поступил запрос в канал 1, либо по цепи переноса (элемент И 3, элемент ИЛИ 6) «единица переписывается в следующий канал и т. д. в том же такте, пока не дойдет до канала, принявшего запрос на обслуживание. Первый сигнал разрешения перебрасывает элемент ИЛИ-НЕ 12 в нулевое состояние. Таким образом, в каждом такте работы устройства обслуживается очередной запрос с наименьшим номером. После обслуживания всех запросов элемент ИЛИ-НЕ 12 снова устанавливается в единичное состояние, и цикл обслуживания повторяется. Любой запрос обслуживается независимо от наличия других запросов, а время ожидания зависит от числа поступивших запросов. Программное управление временем ожидания достигается введением счетчика 9. В счетчик 9 записывается уставка, определяюш,ая требуемое время ожидания обслуживания. Счетчик 9 подсчитывает число сдвигов в цикле, и при переполнении счетчика 9 сигнал переноса старшего разряда сбрасывает все триггеры разрешения 5. После этого цикл работы повторяется, причем его длительность не может превысить время, определяемое счетчиком 9. Порядок обслуживания запросов определяется номером запроса. Первым в цикле обслуживается запрос с меньшим номером. Программное изменение приоритета достигается тем, что двоичный код номера приоритета, записанный в регистр 11 преобразуется дешифратором 10 в позиционный код, причем «единица передается от элемента ИЛИ-НЕ 12 на элемент ИЛИ 6 (N- 1)-го канала, где N - номер канала, записанный в регистре И. Этот же выход дешифратора 10 блокирует работу элементов И 3, 4, разрывая тем самым кольцо цепи сдвигов, так, что «единица, записанная в N-й канал, продвигается по цепи каналов, пока не дойдет до (N- 1)-го канала. После этого элемент ИЛИ-НЕ 12 выдает сигнал «единица, и дикл работы повторяется. Каждый канал связан только с двумя соседними каналами, Таким образом, введение новых узлов деидифратора, регистра, счетчика сдвигов, элемента ИЛИ-НЕ и новых связей между ними позволило устранить недостатки известного устройства. Число внутренних связей уменьшено от 1,5 N до 2 N. При этом обеспечено программное изменение приоритета и времени обслуживания и исключено взаимное влияние процессоров, что позволило повысить надежность устройства. Формула изобретения Многоканальное устройство приоритета, содержащее генератор импульсов, а в каждом канале - триггер запроса, триггер разрешения, два элемента И и элемент- ИЛИ причем вход триггера запроса канала сое

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1982 |

|

SU1080143A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU840906A1 |

| Многоканальное устройство управления вводом информации в микроЭВМ | 1984 |

|

SU1234844A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2589317C1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| Устройство для приоритетного управления | 1982 |

|

SU1081641A1 |

| Устройство для моделирования системы сбора данных | 1988 |

|

SU1534469A1 |

| Многоканальное устройство динамического приоритета | 1981 |

|

SU970371A1 |

| Многоканальное устройство приоритета | 1989 |

|

SU1661765A1 |

Авторы

Даты

1979-04-05—Публикация

1977-10-18—Подача