,(54)МНОГОКЛНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Многоканальное устройство приоритета | 1984 |

|

SU1180895A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1982 |

|

SU1076895A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1983 |

|

SU1132283A1 |

| Контроллер с переменным приоритетом | 1980 |

|

SU907550A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

Изобретение относится к цифровой вычислительнойтехнике и может быть использовано в блоках управления уст ройствами общего пользования, например общей памятью вычислительной сис темы. Известны многоканальные приоритет ные устройства, выполненные в виде идентичных блоков (по одному в каждо канале), каждый из которых содержит последовательно соединенные дешифратор , счетчик и селектор тактов, блок формирования и маскирования запросов и блок хранения кодов приоритетов, соединенный с блоком сравнения и с интерфейсным блоком. В процессе рабо ты устройства логические блоки форми руют на общей шине код, соответствую щий старшему по при9ритету запросу или другую информацию, однозначно on ределяющую источник запроса, который подлежит первоочереднсаду обслуживанию. В тех случаях, когда последовательность работы отдельных каналов может быть заранее предопределена, задача разрешения конфликтных си туаций решается в каждом канале последовательно соединенными дштафратором, счетчиком и селектором тактов i., . Недостаток устройств состоит в их сложности и больших .аппаратурных затратах, вследствие чего их применение в ряде простых систем оказывается неоправданным. Так, например, приоритетное устройство, предназначенное для подключения нескольких каналов к сверхоперативной памяти ЭВМ, должно иметь максимальное быстродействие, возможно, даже в ущерб функциональной гибкости. -наиболее близким по тех«ической сущности к предлагаемому является многоканальное приоритетное устройство ,- содержащее двухступенчатый регистр, соединенный через элемент ИЛИНЕ с блоком управления, состоящим из последовательно соединенных счетчика и дешифратора. Алгоритм работы этого устройства зависит от исла входных запросов, принятых на первую ступень двухступенчатого регистра. Если имеется лишь один запрос, то он немедленно (т.е. по первому же синхронизирукяцему импульсу записи во вторую ступень) передается на соответствующий выход устройства в виде сигнала разрешения, если имеются два или более запросов/ то выборка одного из них осуществляется циклическим сканированием начиная с некоторой случайной позиции 2.

Недостатками устройства являются сложность, обусловленная наличием в каждом из каналов многовходового элемента выделения одиночного запроса ,и двухвходового селекторного элемента, и низкое быстродействие, связанное со случайным характером выборки одного из двух или большего числа запросов . При этом помимо основной задержки, обусловленной временем pact пространения сигналов через устройство, возникает дополнительная задержка, связанная с возможным пропуском тактов при неточном попадании сканирующего сигнала опроса на нужный канаЛ. Эта задержка достигает значительной величины. Например, при восьми каналах двойные запросы обрабатываются со средней дополнительной задерхской, равной двум тактам (периодам синхронизирующих последовательностей импульсов).

Цель изобретения - упрощение устройства и повышение его быстродействия.

Поставленная цельдостигается тем что многоканальное устройство, содержащее два регистра, элемент ИЛИ-НЕ и блок управления, включающий счетчик, соединенный выходом со в-ходом дешифратора, причем информационные входы первого регистра являются соответству ющими входами запросов устройства, выходы - соединены с соответствующими информационными входами второго регистра, выходы которого подключены к соответствующим входам элемента ИЛИ-НЕ и выходам устройства, первый вход синхронизации устройства соединей со. входом синхронизации первого регистра, введены шифратор, элемент И, триггер и элемент задержки, причем вход синхронизации счетчика через элемент задержки соединен с первым входом синхронизации устройства, а информационные входы - с соответствующими выходами шифратора, входы которого подключены к соответствующим выходам первого регистра, выходы дешифратора соединены со входами синхронизации соответствующих разрядов второго регистра, управляющий вход - с выходом элемента И, первым входом подключенного к выходу- элемента ИЛИ-НЕ и синхронизирующему входу триггера/ а вторым входом - ко второму входу синхронизации устройства и установочному входу триггера, выход которого соединен с управляющим входом счетчика.

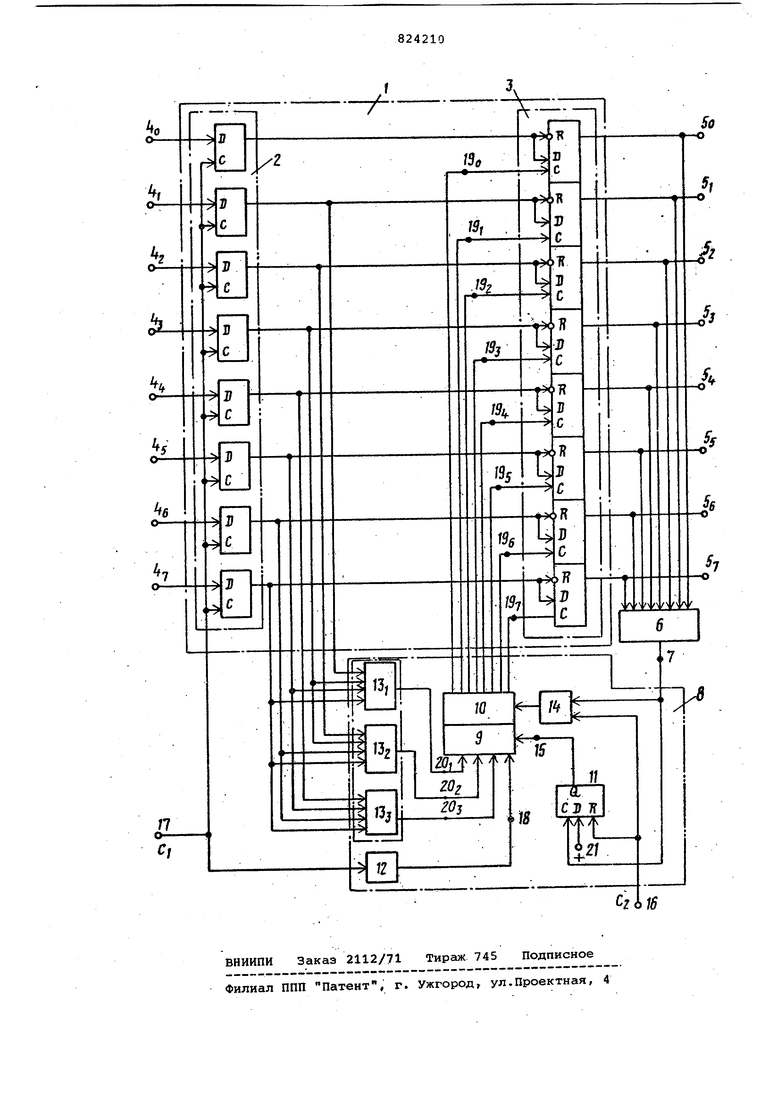

На чертеже представлена блок-схема устройства на восемь каналов.

Устройство содержит двухступенчатый регистр 1, состоящий из последовательно включенных регис ров 2 и 3. Входы регистра 2 являются входами 4

запросов устройства, выходы 5 регистра 3 являются выходами устройства. Выходы 5 устройства через элемент ИЛИ-НЕ б соединены с входом 7 блока 8 управления, который содержит последовательно соединенные счетчик 9 и дешифратор 10, а также триггер 11, элемент 12 задержки, шифраторы 12 и 13 и элемент И 14, вход синхронизации триггера 11 соединен с первым входом элемента И 14 и с входом 7, выход триггера 11 соединен с управлящим входом 15 счетчика 9, установочный вход триггера 11 соединен со вторым входом 16 синхронизации устройства и со вторым входом элемента И 14, выход которого соединен с управляющим входом дешифратора 10. Вход элемента 12 задержки соединен со входом синхронизации регистра 2 и с первым входом 17 синхронизации устройства. Выход элемента задержки соединен со входом 18 синхронизации счечика 9, выходы 19 дешифратора соединены с входами синхронизации регистра 3, выходы шифратора 13 соединены с информационными входами 20 счетчика 9 .

Регистр 2 выполнен на D-триггерах с общим управляющим входом 17. По положительному фронту синхрднизирующего сигнала С , поступающего на вход 17, информадия с входов 4 принимается в регистр 2 и хранится в нем в течение такта. При поступлении на вход 17 положительного фронта очередного импульса (в начале следующего такта) процедура записи в регистр 2 повторяется. Таким образом, регистр 2 предназначен для привязки асинхронных сигналов запросов, поступающих на входы 4 к синхронизирующей серии импульсов С .

Регистр 3 выполнен на О-триггерах с безусловным сбросом и синхронизируемой установкой в единицу. При подаче логического нуля на вход R триггер устанавливается в ноль независимо от состояния входа синхронизации С, запись единицы, поступающей н вход О триггера, производится только по положительной фронту сигнала на входе С.

Триггер 11 выполнен по схеме 0триггера, на информационный вход 21 которого постоянно подана единица. Сброс триггера 11 происходит по сигналу логической единицы на входе 16 независимо от состояния других входов . Установка в единицу происходит по положительному фронту сигнала на входе 7 при условии нашичия логического нуля на входе 16.

Счетчик,9 работает в двух режимах: при наличии логического нуля на входе 15 - в режиме вычитания единицы ИЗ старого содержимого по положительному фронту синхронизирующего сигнала на входе 18, при наличии логической единицы на входе 15 в режиме занесения в счетчик информации с потенциальных входов 20 под действием положительного фронта сигнала на входе 13. Цикл работы системы состоит в следующем. Активный блок, например процессор, инициирующий обмен с устройством общего пользования, при отсутствии (Относящегося к нему сигнала разрешения , на одном из выходов формирует сигнал запроса, который в виде логической единицы поступает на соответствующий вход 4 устройства. Получив через некоторое время сигнал разреше ния в виде логической единицы, активное устройство, не снимая сигнала за проса, производит обмен с устройством общего пользования и по окончании об мена снимает запрос. В ответ на снят запроса снимается сигнал разрешения, после чего производится анализ накопившихся запросов, выдача разрешения на один из выходов 5 на подключение очередного активного устройства к устройству общего пользования и т.д. Окончание предыдущего обмена акти ного устройства с устройством общего пользования завершается снятием логи ческой единицы (запроса) с одного из входов 4. По переднему фронту синхронизирующего сигнала С один из триггеров регистра 2, хранивший соответствующий запрос, переходит в нулевое состояние, остальные триггеры регистра 2 фиксируют накопившиеся входные запросы, подлежащие обслуживанию. Сброс триггера з:апроса вызывает немед ленный (с точностью до задержки триггера) сброс соответствующего триггера регистра 3, т.е. снятие сигнала разре шения для освободившегося канала. При этом элемент ИЛИ-НЕ б формирует логическую единицу, так как на все его 9ХОДЫ поданы логические нули. Положительный фронт сигнала на входе 7 переводит триггер 11 в единичное состоя ние, счетчик 9 переходит в режим ожидания записи исходной информации с входов 20. К этому моменту времени положительный фронт сигнала С., пройдя через элемент 12 задержки, поступает на синхронизир5пощий вход счетчика 9, вызывая прием информации с входов 20. После окончания переходных процессов в счетчике 9 и в дешифраторе 10 на вход 16 поступает сигнал л6гической единицы в виде положительного импульса. Этот импульс сбрасывает триггер 11 и, пройдя через элемент И 14, открывает выходной каскад дешифратора 10, в результате чего на одном из его выходов 19 формируется импульсный сигнал логической единицы, поступающий на вхрд синхронизации одного из триггеров регистра 3. Если на информационном входе этого триггера присутствует логическая единица (есть запрос по данной линии), то триггер устанавливается в единичное состояние, т.е. на одном из выходов 5 формируется потенциальный сигнал разрешения. В этом стнучае дешифратор 10 закрывается, так как сигнал разрешения, пройдя через элемент ИЛИНЕ 6 в виде логического нуля, закрывает элемент И 14, триггер 11 продолжает находиться в нулевом состоянии, а счетчик 9 работает в режиме вычитания единицы по каждому положительному фронту сигнала на входе 18. Такое состояние устройства поддерживается до окончания обмена с устройством общего пользования, после чего снимается текущий запрос, затем, как и в начале внутреннего цикла, снимается разрешение, срабатывает элемент ИЛИИЕ б, устанавливается в единицу триггер 11, принимается и дешифрируется код, сформированный шифратором 13. Если этот код соответствует каналу, по которому но было запроса, то регистр 3 после стробирования сигналом С по-прежнему останется в сброшенном состоянии, а счетчик 9 будет подготовлен к работе в режиме вычитания единицы. На следующем порядке убывания на выходе дешифратора формируется импульс, стробирующий соответствующий .триггер регистра 3. Если и в этом случае нет запроса по данному каналу, то в следующем такте анализируется следующий канал и т.д. При обнаружении запроса по некоторому каналу на соответствующем выходе 5 формируется логическая единица, дешифратор 10 закрывается, счетчик работает в режиме вычитания единицы и т.д. Средняя задержка обслуживания запросов, обусловленная холостым ходом счетчика,- зависит от кратности запросов-, т.е. от числа логических единиц, установившихся на входах 4. При единичиом запросе (входной код содержит лишь одну единицу на одном из входов 4) эта задержка от-сутствует, так как шифрация, а затем дешифрация такого кода приводит к точной выборке нужного канала, и следовательно, к выдаче разрешения на соответствующий выход без дополнительных потерь времени. При восьмикратном- запросе выбор любого канала дешифратором 10 также окажется успешным, т.е. не внесет в систему неоправданных задержек (пропусков тактов). Во всех, промежуточных случаях возможны неточные попадания дешифратора 10 на группу каналов, требующих обслуживания. Анализ работы устройства показывает, что средняя задержка обслуживания максимальна при обработке т тройных запросов. выигрыш во времени, по существу, объясняется тем, что предлагаемое

устройство при работе с групповыми запросами приближенно вычисляет местоположение одного из них, в то время как в известном выборка канала при работе с групповыми запросами осуществляется чисто случайным путем Действительно, при наличии, например, запросов на входах 4., 4 и 4у, шифратором 13 формируется код 10 который после записи в счетчик и дешифрации вызывает срабатывание триггера разрешения, подключенного к выходу 5у.

Таким образом, указанная комбинация тройных запросов вызывает немедленный переход к обработке одного из них. При случайном способе выборки вероятность незамедлительной обработки, т.е. попадания в группу из трех запросов, составляет лишь 3/8, а вероятность работы с задержкой, составл ет 5/8, при этом средняя задержка для данной комбинации запросов (с учетом попаданий), равна 1,12 такта.

Из рассмотренного принципа действия устройства вытекают следующие требования к шифратору 1.3:

а) выходные сигналы должны принимать нулевые значения при нулевых входных наборах;

б), выходные сигналы должны принимать единичные значения при входных наборах, содержащих только одну единицу/

в) при осташьных входных наборах выходные сигналы могут задаваться произвольно.

Простейшей функцией, отвечающей первьм двум усло.виям, является функция ИЛИ, более сложньвми функциягуш являются такие, как ИСКЛЮЧАЮЩЕЕ ИЛИ, ряды многопороговых функций и др. Выбор конкретной функции определяется системными требованиями к устройству на этапе технического проектирования.

Таким образом, применение предлагаемого устройства позволяет уменьшить время задержки обслуживания запросов и сократить затраты оборудования, причем указанные характеристики улучшаются с увеличением числа каналов.

Формула изобретения

Многоканальное устройство приоритета, содержащее два регистра, элеме ИЛИ-НЕ и блок управления, включающий счетчи-к, соединенный выходом со входом дешифратора, причем информационные входы первого регистра являются соответствующими входами запросов устройства, выходы - соединены с соответствующими информационными входами второго регистра, выходы которого подключены к соответствующим входам элемента ИЛИ-НЕ и выходам устройства, первый вход синхронизации устройства соединен со входом синхронизации первого регистра, отличающееся тем, что, с целью, упрощения устройства и повышения его быстродействия, в блок управления введены шифратор, элемент И, триггер и элемент задержки, причем вход синхронизации счетчика через элемент задержки соединен с первым входом синхронизации устройства, а информационные входы - с соответствующими выходами шифратора, входы которого подключены к соответствующим выходам первого регистра, выходы дешифратора (Соединены со входами синхронизации соответствующих разрядов второго регистра, управляющий вход - с выходом элемента И, первым входом подключенного к выходу элемента ИЛИ-НЕ и синхронизирующему входу триггера, а вторым входом - ко второму входу синхронизации устройства и установочному входу триггера, выход которого соединен с управляющим входом счетчика.

Источники.информации, принятые во внимание при экспертизе

Авторы

Даты

1981-04-23—Публикация

1979-06-22—Подача